正在加载图片...

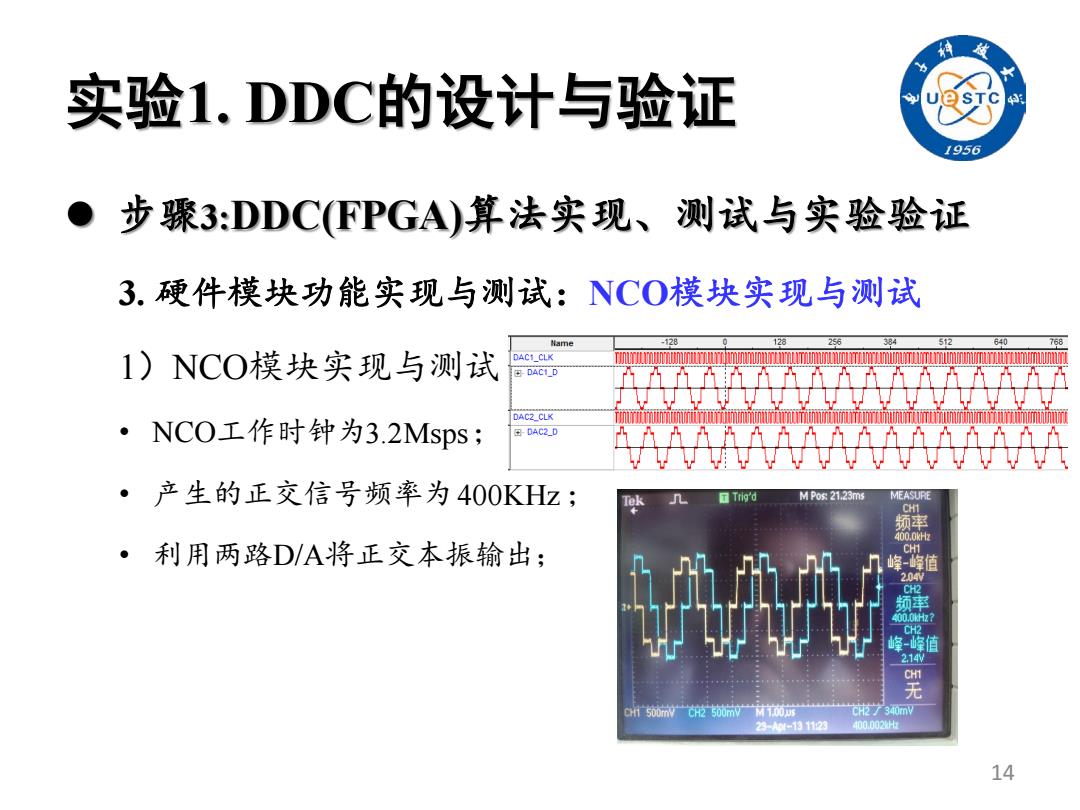

实验1.DDC的设计与验证 L956 步骤3:DDC(FPGA)算法实现、测试与实验验证 3.硬件模块功能实现与测试:NCO模块实现与测试 Name 1)NCO模块实现与测试 DACI CLK DACI D DAC2 CLK ·NCO工作时钟为3.2Msps; DAC2_D ·产生的正交信号频率为400KHz; M Pos:21.23ms MEASURE ·利用两路D/A将正交本振输出; 峰峰值 CH2 2 峰峰值 214W 无 c50t范00m材00g 花7340mv 23-A-131123 400.002h 1414 步骤3:DDC(FPGA)算法实现、测试与实验验证 3. 硬件模块功能实现与测试:NCO模块实现与测试 1)NCO模块实现与测试 • NCO工作时钟为 ; • 产生的正交信号频率为 ; • 利用两路D/A将正交本振输出; 3.2Msps 400KHz 实验1. DDC的设计与验证