试题5参考答案 一、填空 1.如果(A)=45I,(R1)=20H,(20H)=12H,执行XCHD A,@R1;结果(A)=42H,(20H)= 15H 2.AT89S51的异步通信口为全双工(单工/半双工/全双工),若传送速率为每秒 120帧,每帧10位,则波特率为1200bit/s 3.AT89S51内部数据存储器的位地址空间的字节地址范围是20H-2班,对应的位地址范围 是00H-F旺 4.单片机也可称为微控制器或嵌入式控制器 5.当MCS-51执行MOVX A,@R1指令时,伴随着RD控制信号有效。 6.当单片机的PSW=01H时,这时当前的工作寄存器区是0区,R4所对应的存储单 元地址为04H 7.AT89S51的P0 口为高8位地址总线口。 8.设计一个以AT89C51单片机为核心的系统,如果不外扩程序存储器,使其内部4KB闪烁 程序存储器有效,则其EA*引脚应该接+5V 9.在R7初值为OOH的情况下,DJNZ R7,rel指令将循环执行 256次。 10.欲使P1口的低4位输出0,高4位不变,应执行一条ANLP1,#0F0班 命令。 11.单片机外部三大总线分别为数据总线、地址总线和控制总线。 12.数据指针DPTR有16位,程序计数器PC有16位 13.74LS138是具有3个输入的译码器芯片,用其输出作片选信号,最多可在8块芯片 中选中其中任一块。 14.MCS一51指令系统中,ADD与ADDC指令的区别是进位位Cy是否参与加法运算 15.特殊功能寄存器中,单元地址低位为0或8的特殊功能寄存器,可以位寻址。 16.开机复位后,CPU使用的是寄存器第0组,地址范围是00H-OH 17.若某存储器芯片地址线为12根,那么它的存储容量为4kB 18.关于定时器,若振荡频率为12Mz,在方式0下最大定时时间为8.192@s。■ 19.AT89S51复位后,PC与SP的值为分别为O000g和 07H

1 试题 5 参考答案 一、填空 1. 如果(A)=45H,(R1)=20H,(20H)=12H,执行 XCHD A, @ R1;结果(A)= 42H ,(20H)= 15H 2. AT89S51 的异步通信口为 全双工 (单工/半双工/全双工),若传送速率为每秒 120 帧,每帧 10 位,则波特率为 1200 bit/s 3. AT89S51 内部数据存储器的位地址空间的字节地址范围是 20H-2FH ,对应的位地址范围 是 00H-FFH。 4. 单片机也可称为 微控制器 或 嵌入式控制器 5. 当 MCS-51 执行 MOVX A,@R1 指令时,伴随着 RD 控制信号有效。 6. 当单片机的 PSW=01H 时,这时当前的工作寄存器区是 0 区,R4 所对应的存储单 元地址为 04 H 7. AT89S51 的 P0 口为高 8 位地址总线口。 8. 设计一个以 AT89C51 单片机为核心的系统,如果不外扩程序存储器,使其内部 4KB 闪烁 程序存储器有效,则其 EA* 引脚应该接 +5V 9. 在 R7 初值为 00H 的情况下,DJNZ R7,rel 指令将循环执行 256 次。 10. 欲使 P1 口的低 4 位输出 0,高 4 位不变,应执行一条 ANL P1, #0F0H 命令。 11. 单片机外部三大总线分别为 数据总线 、 地址总线 和控制总线。 12. 数据指针 DPTR 有 16 位,程序计数器 PC 有 16 位 13. 74LS138 是具有 3 个输入的译码器芯片,用其输出作片选信号,最多可在 8 块芯片 中选中其中任一块。 14. MCS-51 指令系统中,ADD 与 ADDC 指令的区别是 进位位 Cy 是否参与加法运算 15. 特殊功能寄存器中,单元地址低位为 0 或 8 的特殊功能寄存器,可以位寻址。 16. 开机复位后,CPU 使用的是寄存器第 0 组,地址范围是 00H-07H 17. 若某存储器芯片地址线为 12 根,那么它的存储容量为 4kB 18. 关于定时器,若振荡频率为 12MHz,在方式 0 下最大定时时间为 8.192ms 19. AT89S51 复位后,PC 与 SP 的值为分别为 0000H 和 07H

20.LJP跳转空间最大可达到64红 21.执行如下三条指令后,30H单元的内容是#0EH M OV R1,#30H M O V 40H,#0EH M O V @R1,40H 二、判断题 1当EA脚接高电平时,对ROM的读操作只访问片外程序存储器。(X) 2必须有中断源发出中断请求,并且CPU开中断,CPU才可能响应中断。(X) 38155是一种8位单片机。(X) 451单片机只能做控制用,不能完成算术运算。(X) 5单片机内部RAM和外部RAM是统一编址的,它们的访问指令相同。(X) 6指令AJMP的跳转范围是2KB。(√) 7扩展I/0口占用片外数据存储器的地址资源。(√) 88051单片机,程序存储器数和数据存储器扩展的最大范围都是一样的。(√) 9单片机系统扩展时使用的锁存器,是用于锁存低8位地址(√) 10在A/D变换时,转换频率越高越好。(X) 三、简答题 1、采用6MHz的晶振,定时5ms,用定时器方式1时的初值应为多少?(请给出计算过程》 答: (1)(216-X)×2us=5ms65536-2500=63036 从而X=63036….4分 (2)64536=F63CH…1分 2、 MCS一51单片机片内256B的数据存储器可分为几个区?分别作什么用? 答: (1)通用工作寄存器区,O0i-1FH,共4组,R0-R7,在程序中直接使用 (2)可位寻址区,20册-2阻,可进行位操作,也可字节寻址 (3)用户4AM区,30H-7FH,只可字节寻址,用于数据缓冲及堆找区 (4)特殊功能寄存器区,80H旺,21个特殊功能寄存器离散地分布在该区内,用于实现各 种控制功能

2 20. LJMP 跳转空间最大可达到 64K 21. 执行如下三条指令后,30H 单元的内容是 #0EH M O V R 1,#30H M O V 40H,#0 E H M O V ﹫R 1,40H 二、判断题 1 当 EA 脚接高电平时,对 ROM 的读操作只访问片外程序存储器。(X ) 2 必须有中断源发出中断请求,并且 CPU 开中断,CPU 才可能响应中断。(X ) 3 8155 是一种 8 位单片机。(X ) 4 51 单片机只能做控制用,不能完成算术运算。(X ) 5 单片机内部 RAM 和外部 RAM 是统一编址的,它们的访问指令相同。(X ) 6 指令 AJMP 的跳转范围是 2KB。(√ ) 7 扩展 I/O 口占用片外数据存储器的地址资源。(√ ) 8 8051 单片机,程序存储器数和数据存储器扩展的最大范围都是一样的。(√ ) 9 单片机系统扩展时使用的锁存器,是用于锁存低 8 位地址(√ ) 10 在 A/D 变换时,转换频率越高越好。(X ) 三、简答题 1、采用 6MHz 的晶振,定时 5ms,用定时器方式 1 时的初值应为多少?(请给出计算过程) 答: (1) (21 6-X)×2us=5ms 65536 – 2500 = 63036 从而 X=63036………………………..4 分 (2) 64536=F63CH………………………1 分 2、 MCS-51 单片机片内 256B 的数据存储器可分为几个区?分别作什么用? 答: (1)通用工作寄存器区,00H – 1FH,共4组,R0-R7,在程序中直接使用 (2)可位寻址区,20H-2FH,可进行位操作,也可字节寻址 (3)用户RAM区,30H-7FH,只可字节寻址,用于数据缓冲及堆栈区 (4)特殊功能寄存器区,80H-FFH,21个特殊功能寄存器离散地分布在该区内,用于实现各 种控制功能

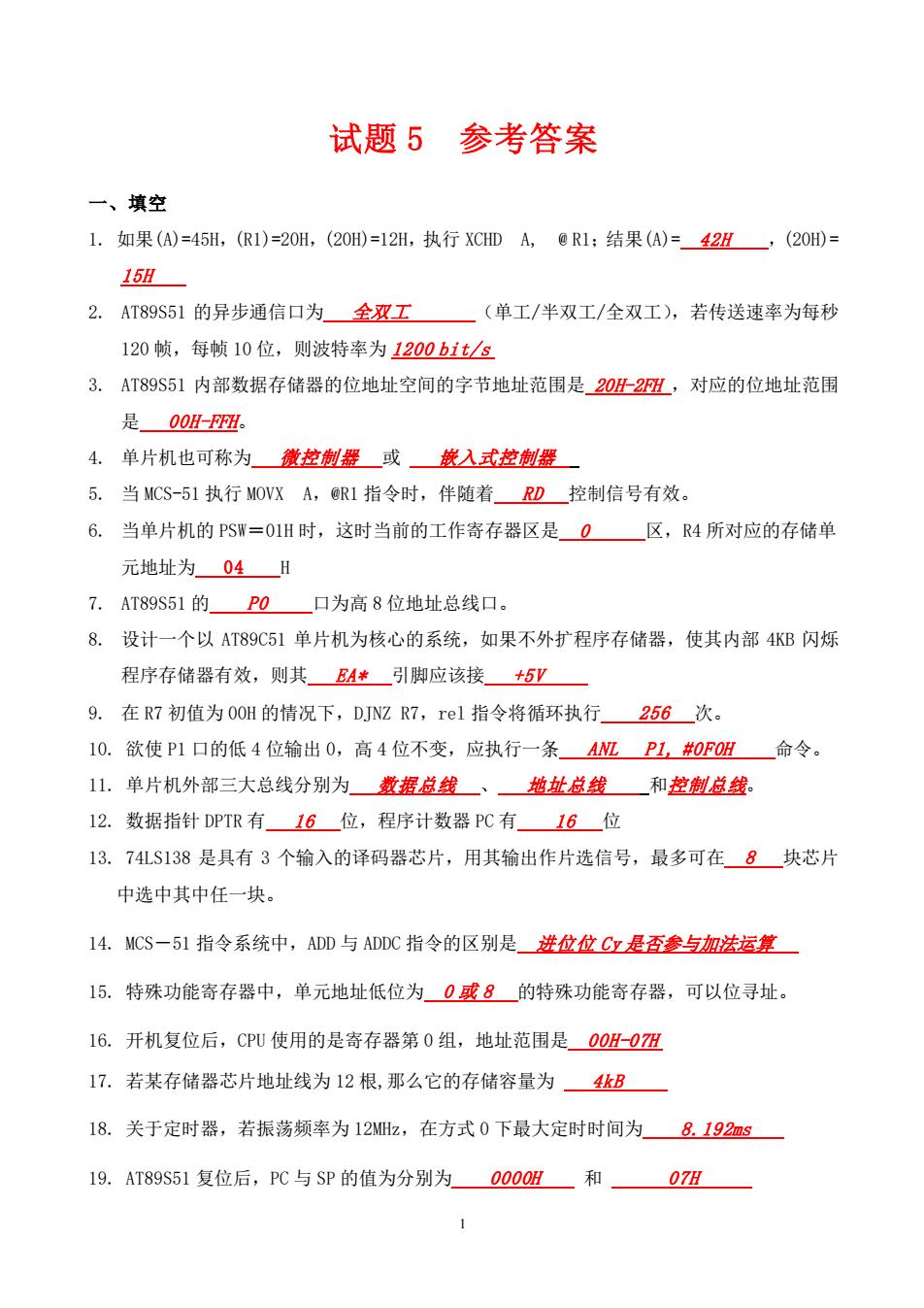

3、 指出以下程序段每一条指令执行后累加器A内的值,己知(R0)=30H。 MOV A,#OAAH (A)=OAAH CPL A ;(A)=55H RL A (A)=0AAH CLR c (A)=OAAH ADDC A,RO (A)=ODAH 四、下图是四片2K×8位存储器芯片的连线图。(1)确定四片存储器芯片地址范围,要求写 出必要的推导过程。(2)编程将片内RAM3OH4FH单元中的32个字节数据传送到片外RAM左 数第一块芯片的最低端32个字节单元(按地址由低至高存放)。 A10-A0 A15 G1 7ō 11 11 11 T A14-o G2A Y2 G2B Y3 A13 A12 8 A11 CE CE CE A74LS138 CE 十8 ”8 8 DB- -8 8 74LS138真值表 GI G2A G2B Y7 Y6 Y5 Y4 Y3 Y2 YI YO 10 0 000 11111110 10 0 001 11111101 100 010 11111011 100 011 11110111 100 100 11101111 100 101 11011111 100 110 10111111 1 00 111 01111111 其岂快爸 XXX 11111111 答:(1)设从左至右RAM芯片号为#1,#2,3,#料 芯片 A15A4 A13A12A11 A10ABABATABASAASA2AAO 地址范围 10 000 00000000000 低8000H (1分) #1 10 000 11111111111 高87FFH (1分) 10 001 00000000000 低8800H (1分) #2 10 001 11111111111 高8FFFH (1分) #3 10 010 00000000000 低9000H (1分) 3

3 3、 指出以下程序段每一条指令执行后累加器 A 内的值,已知(R0)=30H。 MOV A,#0AAH ;(A)= 0AAH CPL A ;(A)= 55H RL A ;(A)= 0AAH CLR C ;(A)= 0AAH ADDC A,R0 ;(A)= 0DAH 四、下图是四片 2K×8 位存储器芯片的连线图。(1)确定四片存储器芯片地址范围,要求写 出必要的推导过程。(2)编程将片内 RAM 30H~4FH 单元中的 32 个字节数据传送到片外 RAM 左 数第一块芯片的最低端 32 个字节单元(按地址由低至高存放)。 G1 G2A G2B C B A Y7 Y6 Y5 Y4 Y3 Y2 Y1 Y0 74LS138真 值 表 答:(1) 设从左至右 RAM 芯片号为#1,#2,#3,#4 芯片 A1 5A14 A1 3 A12A11 A1 0A9A8A7A6A5A4A3A2A1A0 地址范围 #1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 低 8000H (1 分) 1 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 高 87FFH (1 分) #2 1 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 低 8800H (1 分) 1 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 高 8FFFH (1 分) #3 1 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 低 9000H (1 分)

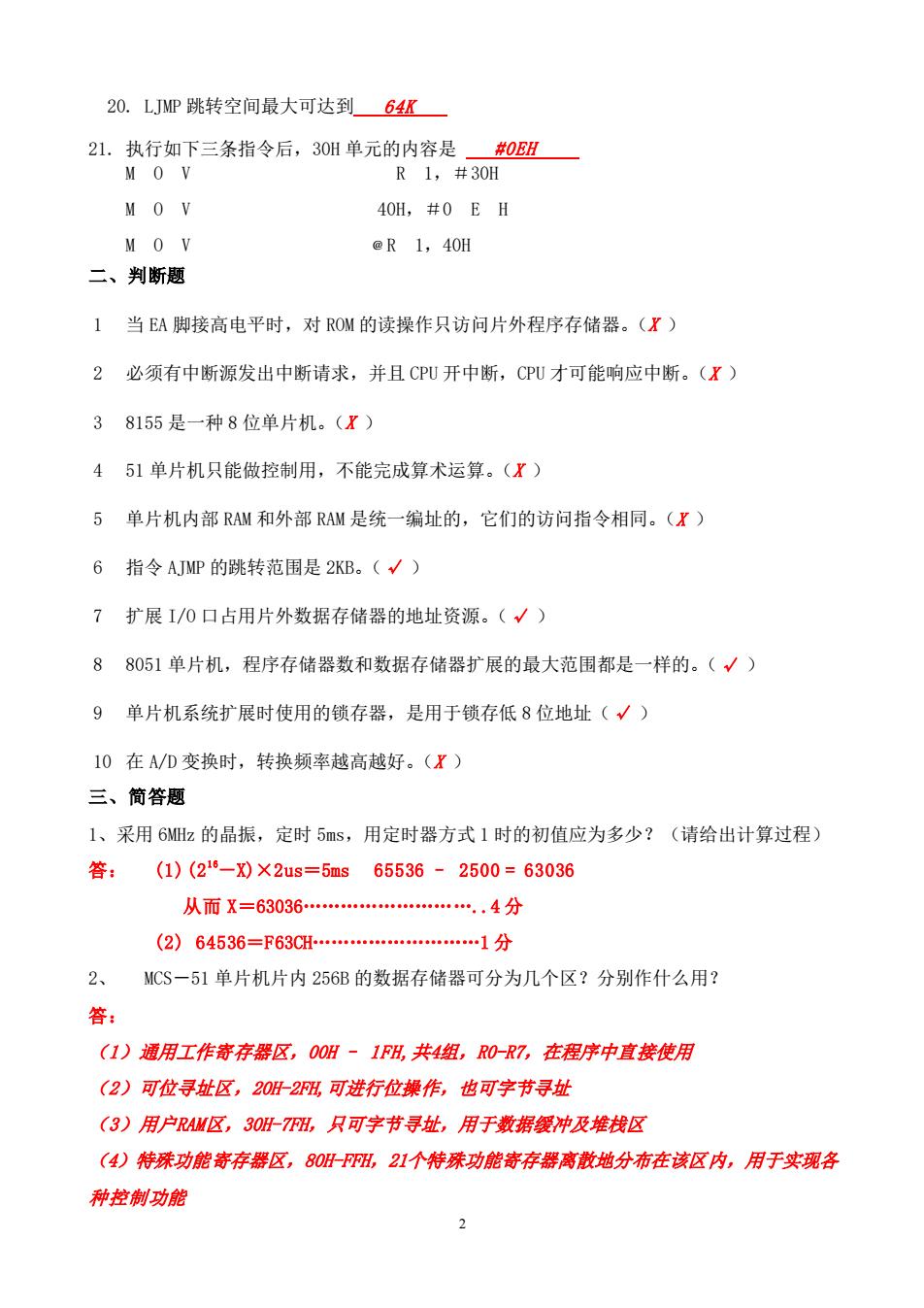

10 010 11111111111 高97FFH (1分) 10 011 00000000000 低9800H (1分) #4 10 011 11111111111 高9FFFH (1分) (2) ORG 1000H MOV DPTR, #8000H; MOV R0,#20H MOV R1,#30H L00P: MOV A,@R1 MOVX ODPTR,A INC DPTR INC R1 DJNZ RO,LOOP HERE: RET ;或AJMP HERE 五、简述行列式键盘线反转法识别按键的工作原理。 +5。y MCS-51 P1.0 DO P1.1 DI P1.2 D2 P1.3 D3 +5 V P1.4 D4012入3 P1.5 D54567 P1.6 D689101 P1.7 D712131415 答: 第1步:让行线编程为输入线,列线编程为输出线,使输出线输出为全低电平,则行线中电 平由高变低的所在行为按键所在行。(3分) 第2步:再把行线编程为输出线,列线编程为输入线,使输出线输出为全低电平,则列线中 电平由高变低的所在列为按键所在列。(3分) 综合上述两步,可确定按键所在行和列。 六、图为8段共阴数码管,请写出如下数值的段码。 4

4 1 0 0 1 0 1 1 1 1 1 1 1 1 1 1 1 高 97FFH (1 分) #4 1 0 0 1 1 0 0 0 0 0 0 0 0 0 0 0 低 9800H (1 分) 1 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 高 9FFFH (1 分) (2) ORG 1000H MOV DPTR, #8000H ; MOV R0, #20H ; MOV R1, #30H ; LOOP: MOV A, @R1 ; MOVX @DPTR,A ; INC DPTR ; INC R1 ; DJNZ R0, LOOP ; HERE: RET ;或 AJMP HERE 五、简述行列式键盘线反转法识别按键的工作原理。 答: 第 1 步:让行线编程为输入线,列线编程为输出线,使输出线输出为全低电平,则行线中电 平由高变低的所在行为按键所在行。(3 分) 第 2 步:再把行线编程为输出线,列线编程为输入线,使输出线输出为全低电平,则列线中 电平由高变低的所在列为按键所在列。(3 分) 综合上述两步,可确定按键所在行和列。 六、图为 8 段共阴数码管,请写出如下数值的段码

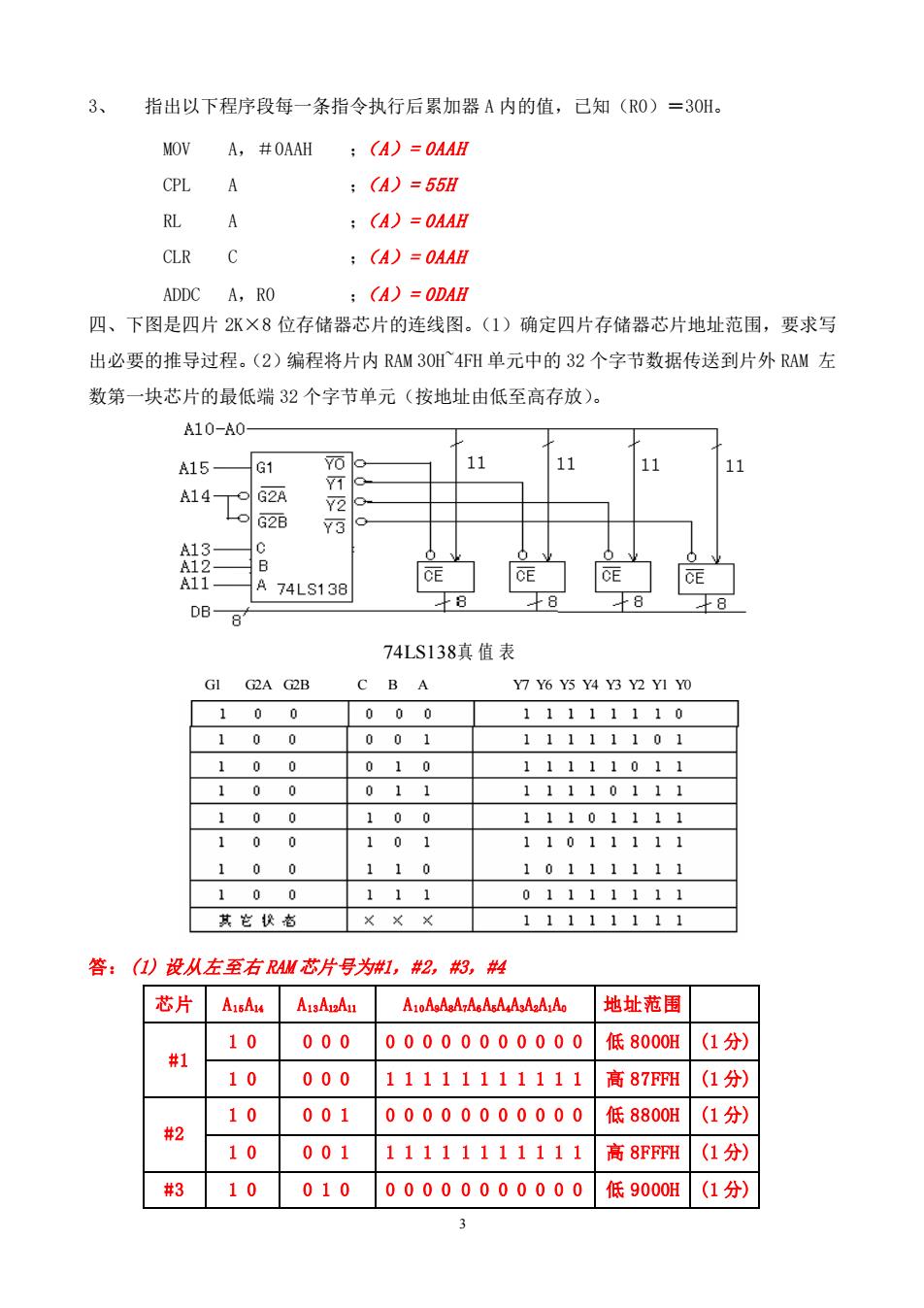

a b c d e f g h 立立立立立立立立 d 答: 03FH(0.5分) 130H(06H)(0.5分) 26DH(0.5分) 379H(0.5分)472H (0.5分) 55BH(0.5分) P67H(0.5分)731H(0.5分) 87FH(0.5分) C0FH(0.5分) 七、回答下列问题并写出简要分析过程。 左下图是DAC0832的应用电路,DA转换时数字量FFH与0OH分别对应于模拟量+5V与OV。 右下图给出了DAC0832的逻辑结构。(1)将图中空缺的电路补充完整;(2)编写程序,产生 图中所示锯齿波。设有一个延时3.905ms的子程序DELAY可以直接调用。 P0.78 D 89 P0.0 7415373 ALE 02 D17o13 D16014 oV时 D15o15 8051 8位输入 8位DAC 8位D/A WR1 WR2 D14o16 D13o- 寄存器 寄存器 转换电路 ID D12o3 D1106 9 IDo ILE DAC 0832 D10o7 E LE2 0 &M1 OAGND AGND +5V DGND 1OODGND +5- DAC0832 DAC0832的逻辑结构 答: (1)共6根线,每根线1分。连线如图,如果WR2*与WR*或XFER*相连也给分。ILE直接接 +5V也正确。 (2)0RG1000H 5

5 答: 0 3FH (0.5 分) 1 30H(06H) (0.5 分) 2 6DH (0.5 分) 3 79H (0.5 分) 4 72 H (0.5 分) 5 5BH (0.5 分) P 67H (0.5 分) 7 31 H (0.5 分) 8 7FH (0.5 分) C 0FH (0.5 分) 七、回答下列问题并写出简要分析过程。 左下图是 DAC0832 的应用电路,DA 转换时数字量 FFH 与 00H 分别对应于模拟量+5V 与 0V。 右下图给出了 DAC0832 的逻辑结构。(1)将图中空缺的电路补充完整;(2)编写程序,产生 图中所示锯齿波。设有一个延时 3.905ms 的子程序 DELAY 可以直接调用。 DAC0832 的逻辑结构 答: (1)共 6 根线,每根线 1 分。连线如图,如果 WR2*与 WR*或 XFER*相连也给分。ILE 直接接 +5V 也正确。 (2) ORG 1000H a b c d e f g h D0 D1 D2 D3 D4 D5 D6 D7 f a e d c b g h

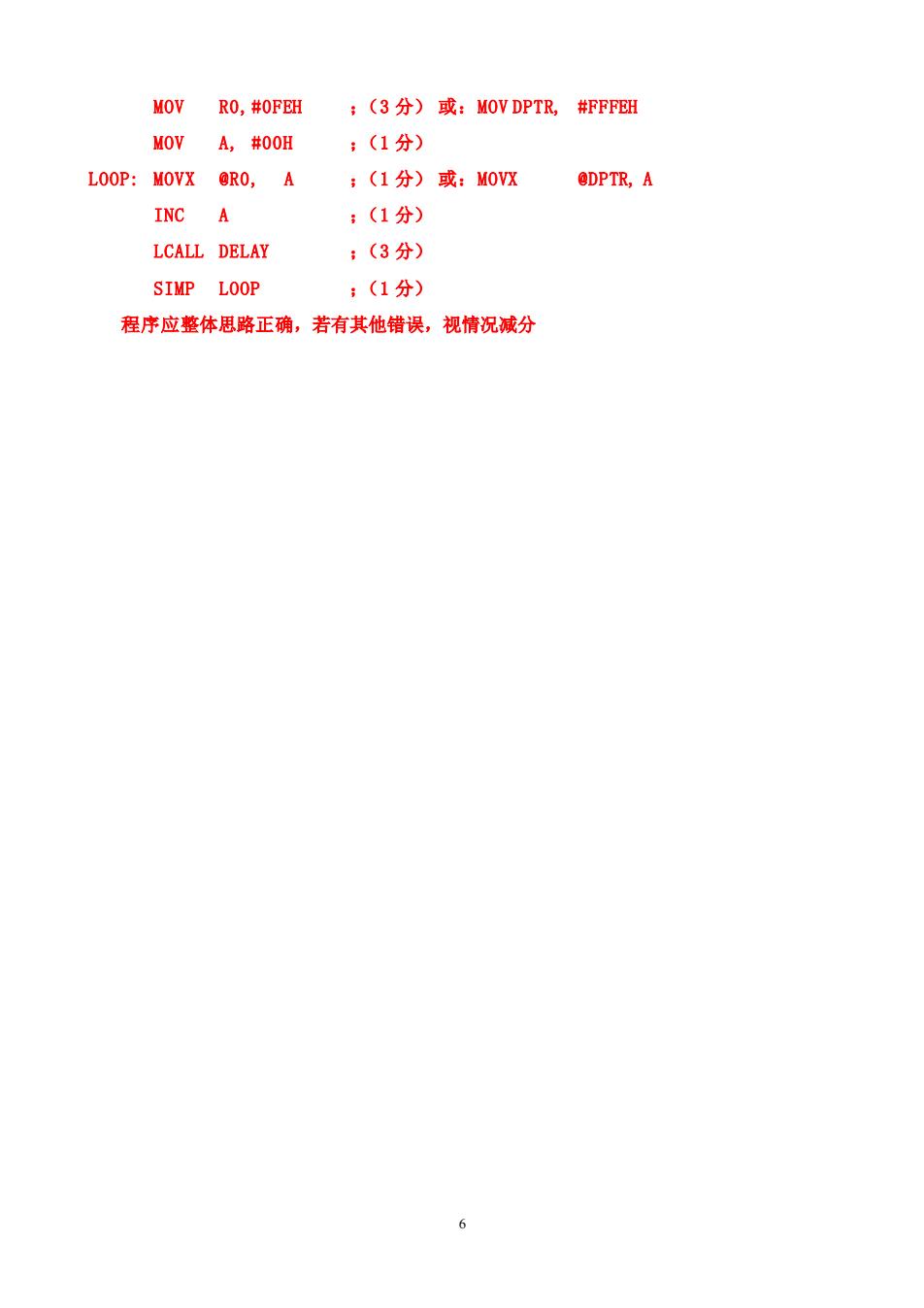

MOV RO,#0FEH ;(3分)或:MOV DPTR, #FFFEH MOV A,#00H ;(1分) LOOP:MOVX @R0,A ;(1分)或:M0VX ODPTR,A INC A :(1分) LCALL DELAY ;(3分) SIMP LOOP ;(1分) 程序应整体思路正确,若有其他错误,视情况减分 6

6 MOV R0, #0FEH ;(3 分) 或:MOV DPTR, #FFFEH MOV A, #00H ;(1 分) LOOP: MOVX @R0, A ;(1 分) 或:MOVX @DPTR, A INC A ;(1 分) LCALL DELAY ;(3 分) SIMP LOOP ;(1 分) 程序应整体思路正确,若有其他错误,视情况减分