第8章 AT89S52单片机外部 存储器的扩展 2 1

1 第8章 AT89S52单片机外部 存储器的扩展 1

第8章AT89S52单片机外部存储器的并行扩展 8.1系统并行扩展结构 8.2地址空间分配和外部地址锁存器 8.2.1存储器地址空间分配 8.2.2外部地址锁存器 8.3静态数据存储器RAM的并行扩展 8.3.1常用的静态RAM(SRAM)芯片 8.3.2外扩数据存储器的读写操作时序 8.3.3AT89S52单片机与RAM的接口设计与软件编程 8.4片内Flash存储器的编程 8.4.1使用通用编程器的程序写入 8.4.2使用下载线的SP编程 2

2 第8章 AT89S52单片机外部存储器的并行扩展 8.1 系统并行扩展结构 8.2 地址空间分配和外部地址锁存器 8.2.1 存储器地址空间分配 8.2.2 外部地址锁存器 8.3 静态数据存储器RAM的并行扩展 8.3.1 常用的静态RAM(SRAM)芯片 8.3.2 外扩数据存储器的读写操作时序 8.3.3 AT89S52单片机与RAM的接口设计与软件编程 8.4 片内Flash存储器的编程 8.4.1 使用通用编程器的程序写入 8.4.2 使用下载线的ISP编程

8.5E2PROM的并行扩展 8.5.1并行E2PROM芯片简介 8.5.2E2PROM的工作方式 8.5.3AT89S52单片机扩展E2 PROM AT2864的设计 3

3 8.5 E2PROM的并行扩展 8.5.1 并行E2PROM芯片简介 8.5.2 E2PROM的工作方式 8.5.3 AT89S52单片机扩展E2PROM AT2864的设计

【内容概要】 当AT89S52单片机片内的数据存储器与程序存储器(Flash 存储器)的容量不能满足需要的情况下,需要进行扩展。存储 器的扩展分为并行扩展和串行扩展,本章介绍并行扩展存储器 的基本方法,首先介绍了系统并行扩展的基本结构,还介绍了 片外存储器地址空间分配的的两种方法:线选法和译码法,以 及外部地址锁存器的选择。对于片内Flash程序存储器,重点介 绍了程序的写入,而对片外数据存储器以及E2PROM的并行扩 展则进行了较为详细的阐述。 4

4 【内容概要】 当AT89S52单片机片内的数据存储器与程序存储器(Flash 存储器)的容量不能满足需要的情况下,需要进行扩展。存储 器的扩展分为并行扩展和串行扩展,本章介绍并行扩展存储器 的基本方法,首先介绍了系统并行扩展的基本结构,还介绍了 片外存储器地址空间分配的的两种方法:线选法和译码法,以 及外部地址锁存器的选择。对于片内Flash程序存储器,重点介 绍了程序的写入,而对片外数据存储器以及E2PROM的并行扩 展则进行了较为详细的阐述

8.1系统扩展结构 AT89S52单片机采用总线结构,使扩展易于实现, AT89S52单片机系统扩展结构如图8-1所示。 地址总线(AB) AT89S52 数据总线(DB) 控制总线(CB) 数据 程序 I/O接口 I/O接口 存储器 存储器 I/O设备 I/O设备 图8-1AT89S52单片机的系统扩展结构 5

5 8.1 系统扩展结构 AT89S52单片机采用总线结构,使扩展易于实现, AT89S52单片机系统扩展结构如图8-1所示。 5 图8-1 AT89S52单片机的系统扩展结构

由图8-1可以看出,系统扩展主要包括存储器扩展和I/0 接口部件扩展。 AT89S52单片机的存储器扩展即包括程序存储器扩展又包 括数据存储器扩展。AT89S52单片机采用程序存储器空间和 数据存储器空间截然分开的哈佛结构。扩展后,系统形成了 两个并行的外部存储器空间。 系统扩展是以AT89$52为核心,通过总线把单片机与各扩 展部件连接起来。因此,要进行系统扩展首先要构造系统总 线。 系统总线按功能通常分为3组,如图8-1所示。 6

6 由图8-1可以看出,系统扩展主要包括存储器扩展和I/O 接口部件扩展。 AT89S52单片机的存储器扩展即包括程序存储器扩展又包 括数据存储器扩展。AT89S52单片机采用程序存储器空间和 数据存储器空间截然分开的哈佛结构。扩展后,系统形成了 两个并行的外部存储器空间。 系统扩展是以AT89S52为核心,通过总线把单片机与各扩 展部件连接起来。因此,要进行系统扩展首先要构造系统总 线。 系统总线按功能通常分为3组,如图8-1所示。 6

(1)地址总线 (Address Bus,AB):用于传送单片机发 出的地址信号,以便进行存储单元和O接口芯片中的寄存器单 元的选择。 (2)数据总线 (Data Bus,DB):用于单片机与外部存储 器之间或与O接口之间传送数据,数据总线是双向的。 (3)控制总线(Control Bus,CB):控制总线是单片机发 出的各种控制信号线。 7

7 (1)地址总线(Address Bus,AB):用于传送单片机发 出的地址信号,以便进行存储单元和I/O接口芯片中的寄存器单 元的选择。 (2)数据总线(Data Bus,DB):用于单片机与外部存储 器之间或与I/O接口之间传送数据,数据总线是双向的。 (3)控制总线(Control Bus,CB):控制总线是单片机发 出的各种控制信号线

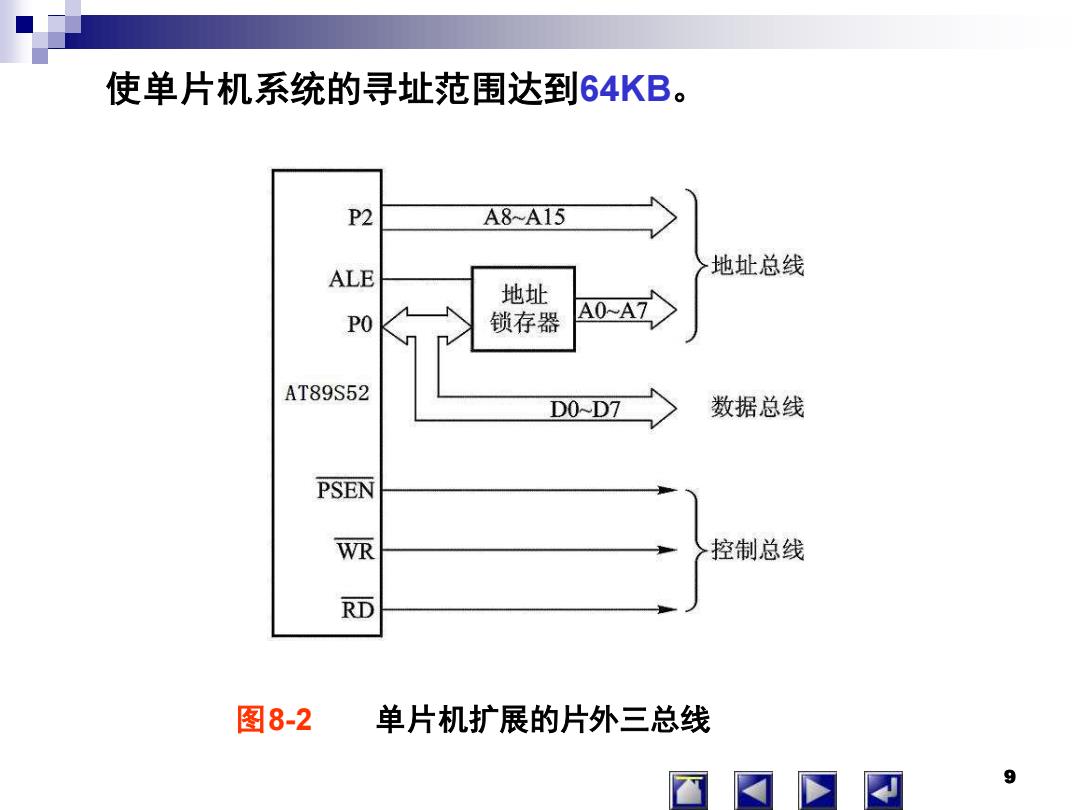

如何来构造系统的三总线。 1.P0口作为低8位地址/数据总线 AT89S51受引脚数目限制,P0口既用作低8位地址总线,又用 作数据总线(分时复用),因此需增加一个8位地址锁存器。 AT89S51访问外部扩展的存储器单元或I/0接口寄存器时,先发 出低8位地址送地址锁存器锁存,锁存器输出作为系统的低8位 地址(A7~A0)。随后,P0口又作为数据总线口(D7~D0),如 图8-2所示。 2.P2口的口线作为高位地址线 P2口用作系统的高8位地址线,再加上地址锁存器提供的低8 位地址,便形成了系统完整的16位地址总线。 8

8 如何来构造系统的三总线。 1.P0口作为低8位地址/数据总线 AT89S51受引脚数目限制,P0口既用作低8位地址总线,又用 作数据总线(分时复用),因此需增加一个8位地址锁存器。 AT89S51访问外部扩展的存储器单元或I/O接口寄存器时,先发 出低8位地址送地址锁存器锁存,锁存器输出作为系统的低8位 地址(A7~ A0)。随后,P0口又作为数据总线口(D7~ D0),如 图8-2所示。 2.P2口的口线作为高位地址线 P2口用作系统的高8位地址线,再加上地址锁存器提供的低8 位地址,便形成了系统完整的16位地址总线。 8

使单片机系统的寻址范围达到64KB。 P2 A8A15 ALE 地址总线 地址 PO 锁存器 A0-A7 AT89S52 DO~D7 数据总线 PSEN WR 控制总线 RD 图8-2 单片机扩展的片外三总线 9

9 使单片机系统的寻址范围达到64KB。 图8-2 单片机扩展的片外三总线

3.控制信号线 除地址线和数据线外,还要有系统的控制总线。这些信号 有的就是单片机引脚的第一功能信号,有的则是P3口第二功 能信号。包括: ()PSEN*作为外扩程序存储器的读选通控制信号。 (2)RD*和WR*为外扩数据存储器和VO的读、写选通控制 信号。 (3)ALE作为P0口发出的低8位地址锁存控制信号。 (4)EA*为片内、片外程序存储器的选择控制信号。 可见,AT89S51的4个并行VO口,由于系统扩展的需要, 真正作为数字O用,就剩下P1和P3的部分口线。 10

10 3.控制信号线 除地址线和数据线外,还要有系统的控制总线。这些信号 有的就是单片机引脚的第一功能信号,有的则是P3口第二功 能信号。包括: (1)PSEN*作为外扩程序存储器的读选通控制信号。 (2)RD*和WR*为外扩数据存储器和I/O的读、写选通控制 信号。 (3)ALE作为P0口发出的低8位地址锁存控制信号。 (4)EA*为片内、片外程序存储器的选择控制信号。 可见,AT89S51的4个并行I/O口,由于系统扩展的需要, 真正作为数字I/O用,就剩下P1和P3的部分口线。 10