共6页第1页 年月日 考试用 西安邮电学院课程考试试题(A卷) (2010一一2011学年度第1学期) 课程名称: 数字电路与逻辑设计 试卷类型:(A、B、C) 考试专业、年级:电子0801-0808、 通工0801-0816、科技0801-0804 光电0801-0804、光信息0801-0803 题号 三 四 五 六 七 八 九总分 得分 阅卷人 ,填空题(每空2分,共20分) 1. 十六进制数(16F)休用8421余3码表示为 2.函数F=AB+BC的最小项表达式为F(4,B,C)=∑( 毁 F的与非与非表达式为 (允许反变量输入). F的反演式为 F的对偶式为 3.某T与非门的标准输入高电平为3.6伏,标准输入低电平为0.3伏,关门电平 'o=0.8V开门电平Vo=18,则低电平噪声容限Va= 高电平噪声容限'a= 4.要构成容量为4K×8bit的RAM,需要 片容量为256×8bit的RAM. 5.一个初始状态为0001的模值为12的四位二进制同步递加计数器经过33个CP脉冲后, 其状态为 一组合逻辑电路的输入、输出波形如下图所示,A、B为输入信号,F为输出信号, 则输出信号F与输入信号A、B的逻辑关系为F= 蹬 说明:1、除填空愿、图解及特要求外一般不留答题空间

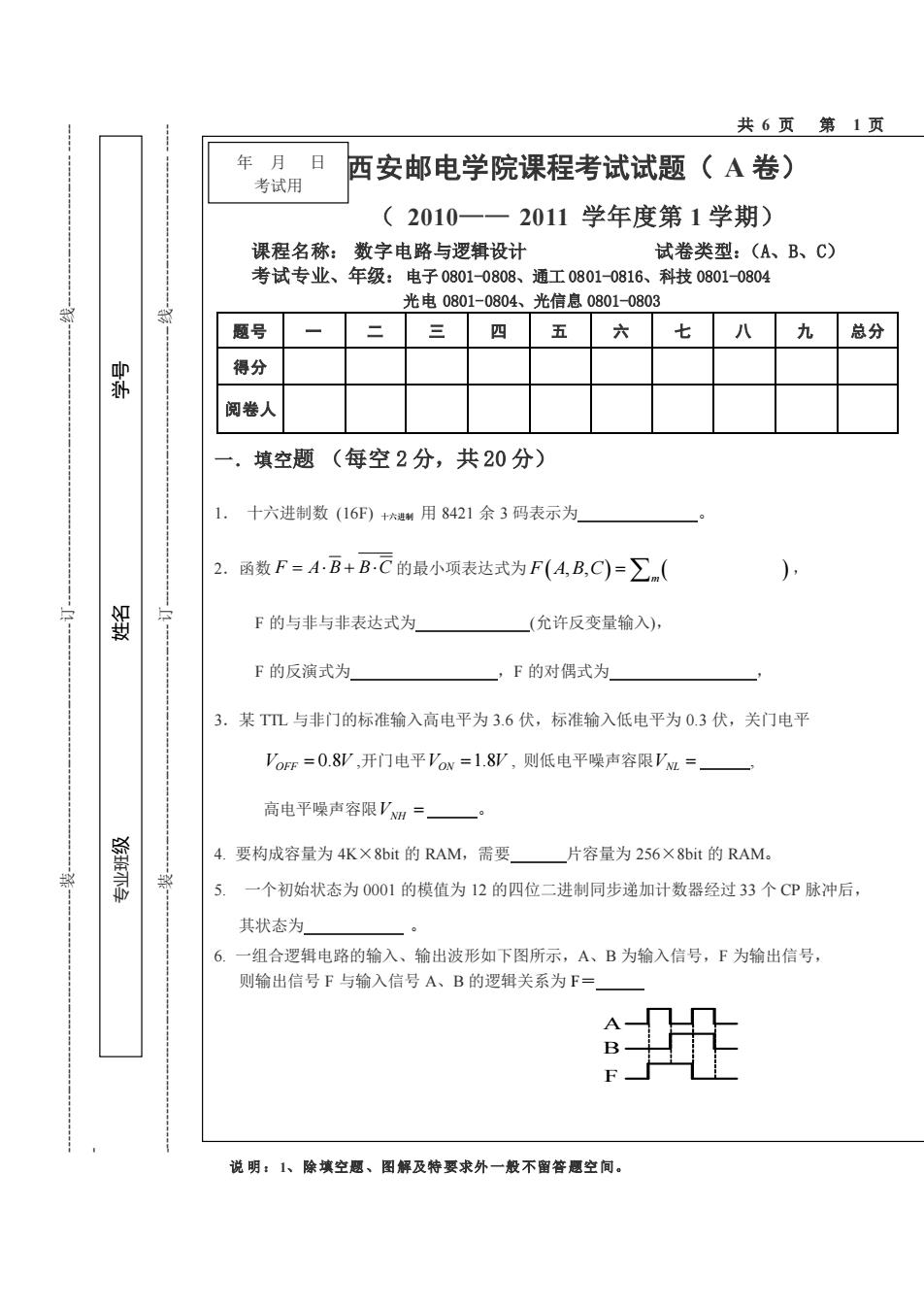

共 6 页 第 1 页 说 明 :1、 除 填空题、图 解及特 要求外 一般 不留答 题空 间。 - 装- 订- 线- - - - 装- 订- 线- - - 西安邮电学院课程考试试题( A 卷) ( 2010—— 2011 学年度第 1 学期) 课程名称: 数字电路与逻辑设计 试卷类型:(A、B、C) 考试专业、年级:电子 0801-0808、通工 0801-0816、科技 0801-0804 光电 0801-0804、光信息 0801-0803 题号 一 二 三 四 五 六 七 八 九 总分 得分 阅卷人 一.填空题 (每空 2 分,共 20 分) 1. 十六进制数 (16F) 十六进制 用 8421 余 3 码表示为 。 2.函数 F A B B C = + 的最小项表达式为 ( , , ) ( ) m F A B C = , F 的与非与非表达式为 (允许反变量输入), F 的反演式为 ,F 的对偶式为 , 3.某 TTL 与非门的标准输入高电平为 3.6 伏,标准输入低电平为 0.3 伏,关门电平 VOFF = 0.8V ,开门电平 VON =1.8V , 则低电平噪声容限 VNL = , 高电平噪声容限 VNH = 。 4. 要构成容量为 4K×8bit 的 RAM,需要 片容量为 256×8bit 的 RAM。 5. 一个初始状态为 0001 的模值为 12 的四位二进制同步递加计数器经过 33 个 CP 脉冲后, 其状态为 。 6. 一组合逻辑电路的输入、输出波形如下图所示,A、B 为输入信号,F 为输出信号, 则输出信号 F 与输入信号 A、B 的逻辑关系为 F= A B F 专业班 级 姓名 学号 年 月 日 考试用

总印1600份 (附答趣纸1页) 二.选择题:(30分) 注意: 1.每道题的正确答案只有一个,请将正确答案填入第二题答题栏中,以横线划过答 题栏所选的答案,例如: 2.题中涉及到的中规模器件的功能表,附在试卷纸的最后一页。 第二题答题栏 1 3 4 5 789 AA AAAAA c DDDD 1.TTL与非门电路如右图所示,输出下=」 A.0 B.I C.AB D.4+B E.A©B 2.下图所示电路中,Y1= A.F=0 B.F-4+B+C.D+E C.F=ABC.DE D.F=ABC+DE E.以上答案都不对 Y 100K 2. 装订试卷 考生答卷时不得拆开或在框外留写标记,否则按零分计

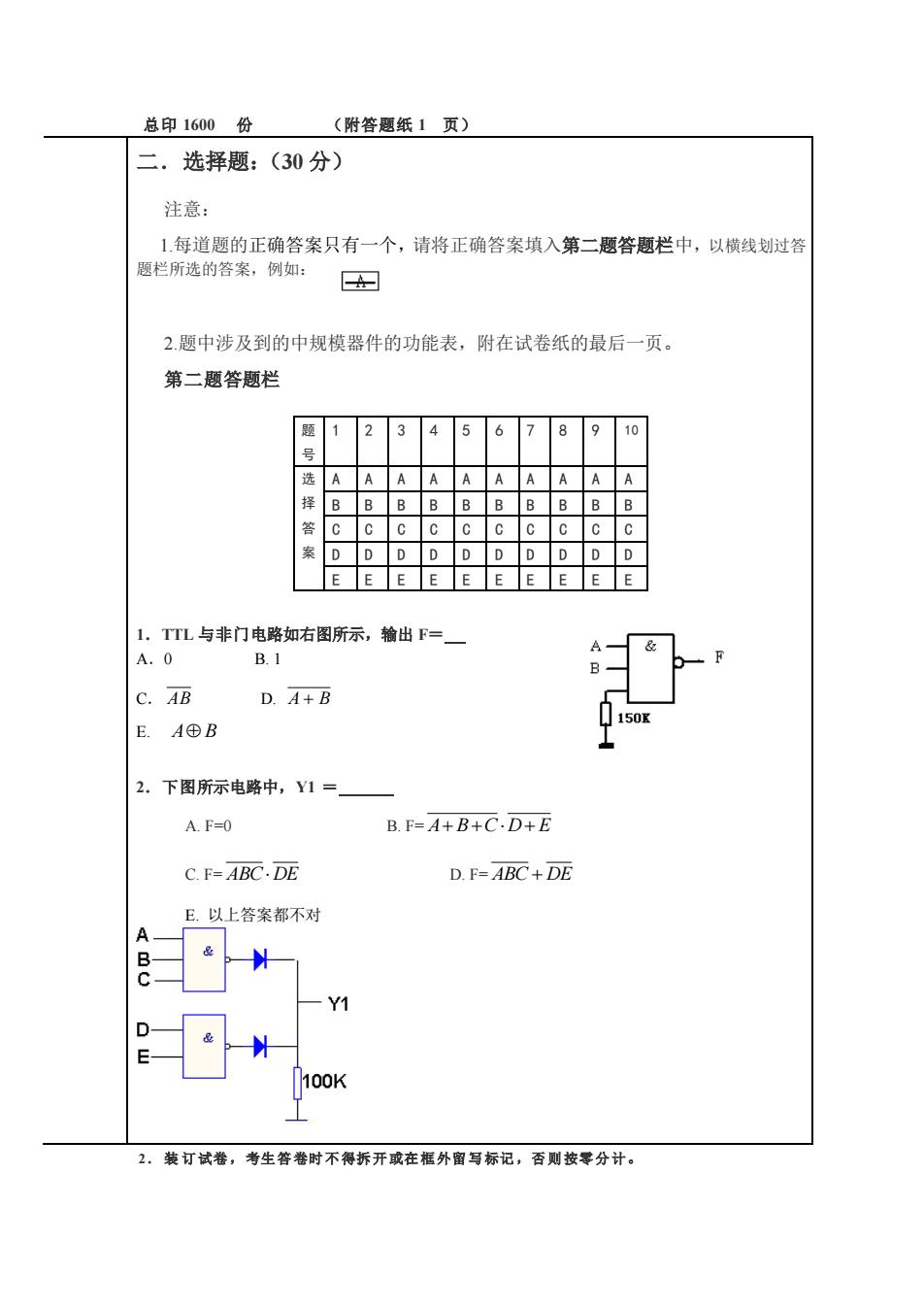

总印 1600 份 (附答题纸 1 页) 二.选择题:(30 分) 注意: 1.每道题的正确答案只有一个,请将正确答案填入第二题答题栏中,以横线划过答 题栏所选的答案,例如: 2.题中涉及到的中规模器件的功能表,附在试卷纸的最后一页。 第二题答题栏 1.TTL 与非门电路如右图所示,输出 F= A.0 B. 1 C. AB D. A + B E. A B 2.下图所示电路中,Y1 = A. F=0 B. F= A B C D E + + + C. F= ABC DE D. F= ABC DE + E. 以上答案都不对 题 号 1 2 3 4 5 6 7 8 9 10 选 择 答 案 A A A A A A A A A A B B B B B B B B B B C C C C C C C C C C D D D D D D D D D D E E E E E E E E E E 2. 装 订 试卷 , 考生 答 卷时 不 得拆 开 或在 框 外留 写 标记 ,否 则 按零分计

共6页第2页 .以下各单元电路中, 可以产生时序电路所需要的占空比近似为50%的时钟脉冲信号。 A.多诰振荡器 B.单稳态触发器 C.四位并行全加器 D.数值比较器 E.JK触发器 4.某电路的VHDL语言描述 ENTITY tests 如右所示,此test实现的 PORT (a.bs:IN STD LOGIC 逻辑功能为: 器 A 一位二进制数半加器 ARCHITECTURE one OFtest IS B.D触发器 BEGIN C.二输入与非门 PROCESS(ab.s) D.二选一数据选择器 BEGIN E.2-4线译码器 yc=a; ELSE y<=b: END IF: END PROCESS 毁 日 END ARCHITECTURE one: 5.电路如下,芯片4008为四位二进制全加器,管脚A3A2A1A0、B3B2B1B0为被加数、加数: 管脚S3S2S1S0为本位和,管脚CN为低位向本位的进位,外接信号(,管脚C0UT为本位向 高位的进位,电路如图所示,分析电路,下列说法正确的是: COUT 81 7 0 4008 A.M0,S3S2S1S0为 1001,00T为1 B.M=0,S3S2S1S0为1001,C0UT为0 C.M=1,S3S2S1S0为0100,C0UT为1 D.M1,S3S2S1S0为0100,C0UT为0 E.以上均不对 说明:1、除填空题、图解及特要求外一般不留答愿空间

共 6 页 第 2 页 - 说 明 : 1、 除 填空题 、图 解及特 要求外 一般 不留答 题空 间。 装- 订- 线- - - - 装- 订- 线- - - 3.以下各单元电路中, 可以产生时序电路所需要的占空比近似为 50%的时钟脉冲信号。 A. 多谐振荡器 B.单稳态触发器 C. 四位并行全加器 D.数值比较器 E. JK 触发器 4. 某电路的 VHDL 语言描述 如右所示,此 test 实现的 逻辑功能为: A. 一位二进制数半加器 B. D 触发器 C. 二输入与非门 D. 二选一数据选择器 E. 2-4 线译码器 5. 电路如下,芯片 4008 为四位二进制全加器,管脚 A3 A2 A1 A0、B3 B2 B1 B0 为被加数、加数, 管脚 S3 S2 S1 S0 为本位和,管脚 CIN 为低位向本位的进位,外接信号 M, 管脚 COUT 为本位向 高位的进位,电路如图所示,分析电路,下列说法正确的是: A. M=0,S3 S2 S1 S0 为 1001,COUT 为 1 B. M=0 ,S3 S2 S1 S0 为 1001,COUT 为 0 C. M=1 ,S3 S2 S1 S0 为 0100,COUT 为 1 D. M=1 ,S3 S2 S1 S0 为 0100,COUT 为 0 E. 以上均不对 专业班 级 姓名 学号 ENTITY test IS PORT ( a , b ,s: IN STD_LOGIC ; y : OUT STD_LOGIC ); END ENTITY test; ARCHITECTURE one OFtest IS BEGIN PROCESS(a,b,s) BEGIN IF s = '0' THEN y<=a; ELSE y<=b; END IF; END PROCESS; END ARCHITECTURE one;

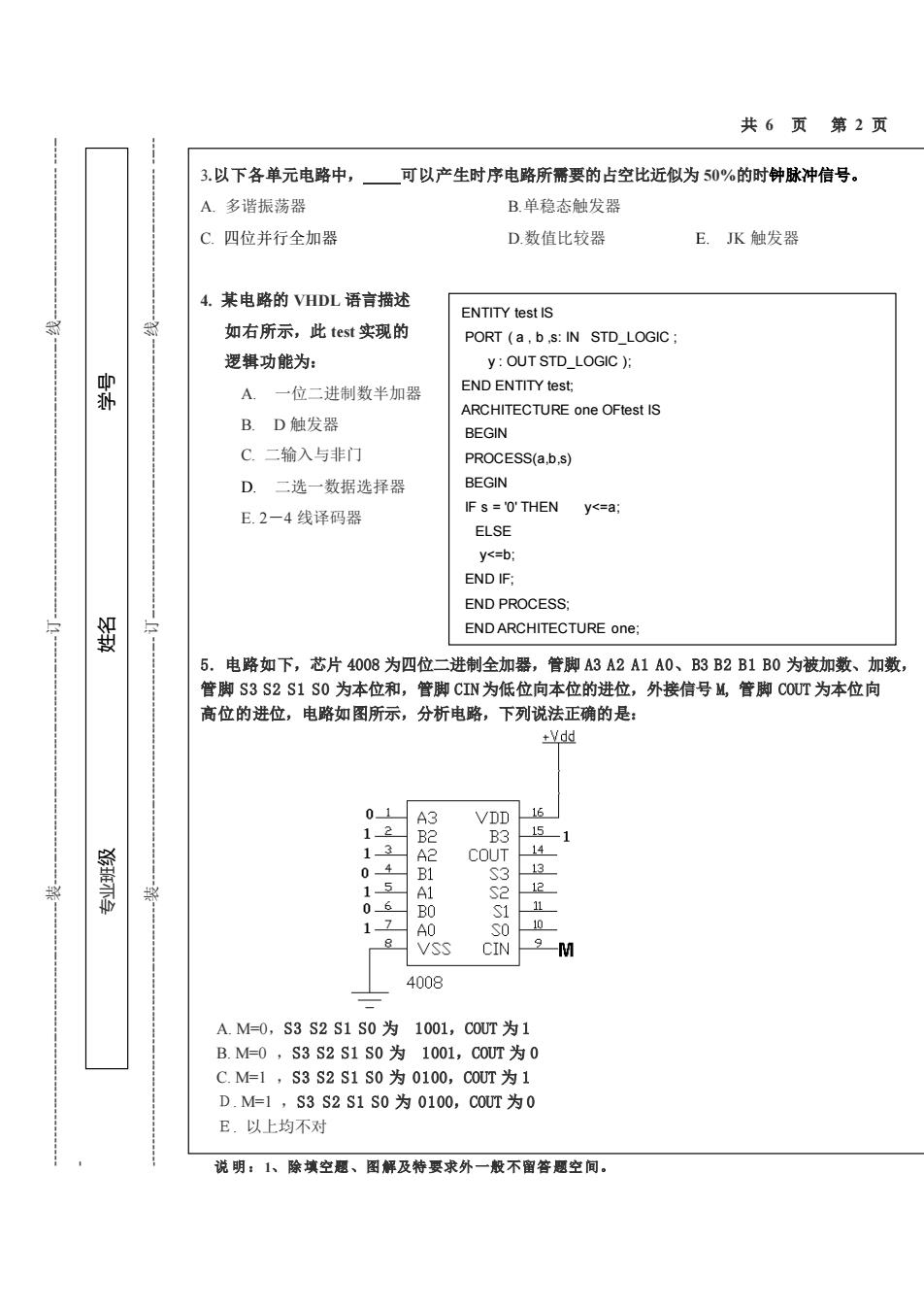

总印1600份 (附答题纸1页) 6.下列电略的逻辑功能为: A. 模16计数器 B.可以自启动的扭环形计数器 C.可以自启动的环形计数器 D.不可自启动的环形计数器 E。不可自启动的扭环形计数器 CP 国国因国 7.74153是4选1数据选择器,用74153实现函数:FA,B,C)-m(0,3,5,6,7), 正确的电路是: ST 74153 74153 D D3 A. A B 74153 74153 C. E,以上电路均不对 2,装订试卷,考生答卷时不得拆开或在框外留写标记,否则安零分计

总印 1600 份 (附答题纸 1 页) 6. 下列电路的逻辑功能为: A. 模 16 计数器 B. 可以自启动的扭环形计数器 C. 可以自启动的环形计数器 D. 不可自启动的环形计数器 E. 不可自启动的扭环形计数器 7. 74153 是 4 选 1 数据选择器,用 74153 实现函数:F(A,B,C)=∑m(0,3,5, 6,7), 正确的电路是: E,以上电路均不对 2. 装 订 试卷 , 考生 答 卷时 不 得拆 开 或在 框 外留 写 标记 ,否 则 安零 分 计

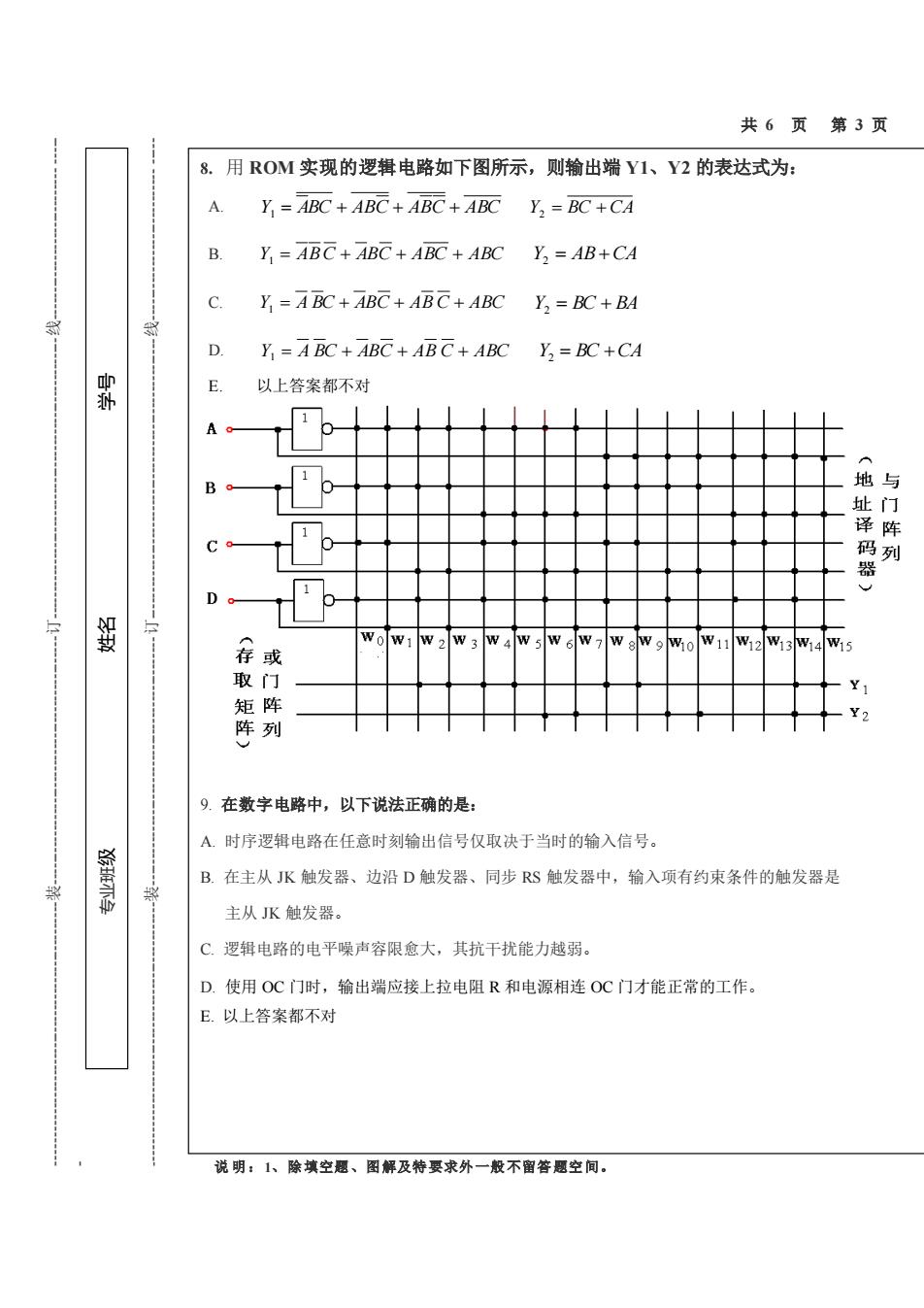

共6页第3页 8. 用ROM实现的逻辑电略如下图所示,则输出端Y1、Y2的表达式为: A Y ABC+ABC+ABC+ABC Y,BC+CA B. Y=ABC+ABC+ABC+ABC Y,=AB+CA C. Y=ABC+ABC+ABC+ABC Y,=BC+BA D Y=ABC+ABC+ABC+ABC Y,=BC+CA E. 以上答案都不对 A B 地与 c 阵列 D 1 毁 存或 矩阵) 9.在数字电路中,以下说法正确的是 A时序逻辑电路在任意时刻输出信号仅取决于当时的输入信号。 B.在主从JK触发器、边沿D触发器、同步RS触发器中,输入项有约束条件的触发器是 主从JK触发器。 C.逻辑电路的电平噪声容限愈大,其抗干扰能力越弱, D.使用OC门时,输出端应接上拉电阻R和电源相连OC门才能正常的工作。 E.以上答案都不对 说明:1、除填空题、图解及特要求外一般不留答愿空间

共 6 页 第 3 页 - 说 明 : 1、 除 填空题 、图 解及特 要求外 一般 不留答 题空 间。 装- 订- 线- - - - 装- 订- 线- - - 8. 用 ROM 实现的逻辑电路如下图所示,则输出端 Y1、Y2 的表达式为: A. Y1 = ABC + ABC + ABC + ABC Y2 = BC + CA B. Y1 = ABC + ABC + ABC + ABC Y2 = AB +CA C. Y1 = A BC + ABC + AB C + ABC Y2 = BC + BA D. Y1 = A BC + ABC + AB C + ABC Y2 = BC +CA E. 以上答案都不对 9. 在数字电路中,以下说法正确的是: A. 时序逻辑电路在任意时刻输出信号仅取决于当时的输入信号。 B. 在主从 JK 触发器、边沿 D 触发器、同步 RS 触发器中,输入项有约束条件的触发器是 主从 JK 触发器。 C. 逻辑电路的电平噪声容限愈大,其抗干扰能力越弱。 D. 使用 OC 门时,输出端应接上拉电阻 R 和电源相连 OC 门才能正常的工作。 E. 以上答案都不对 专业班 级 姓名 学号

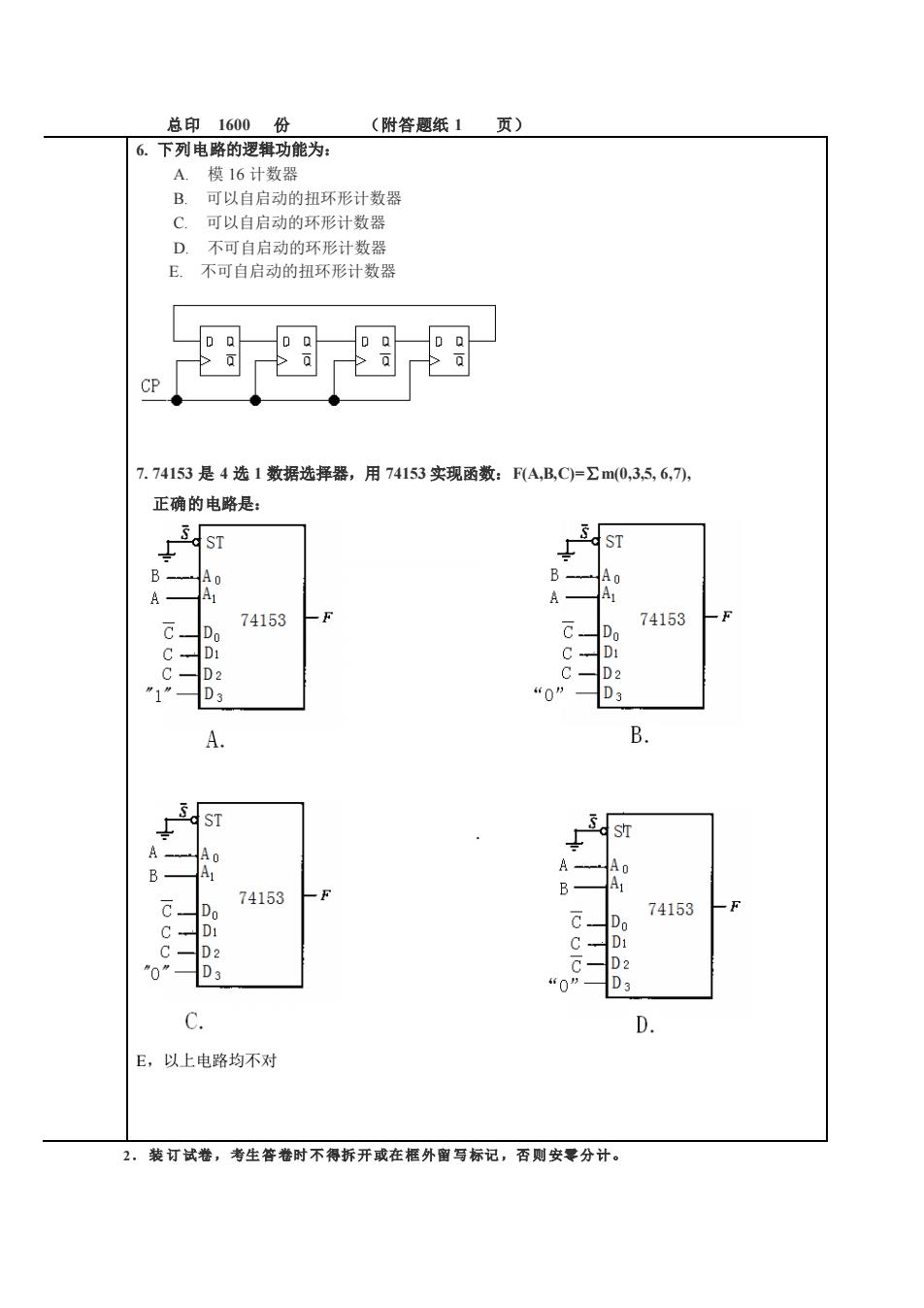

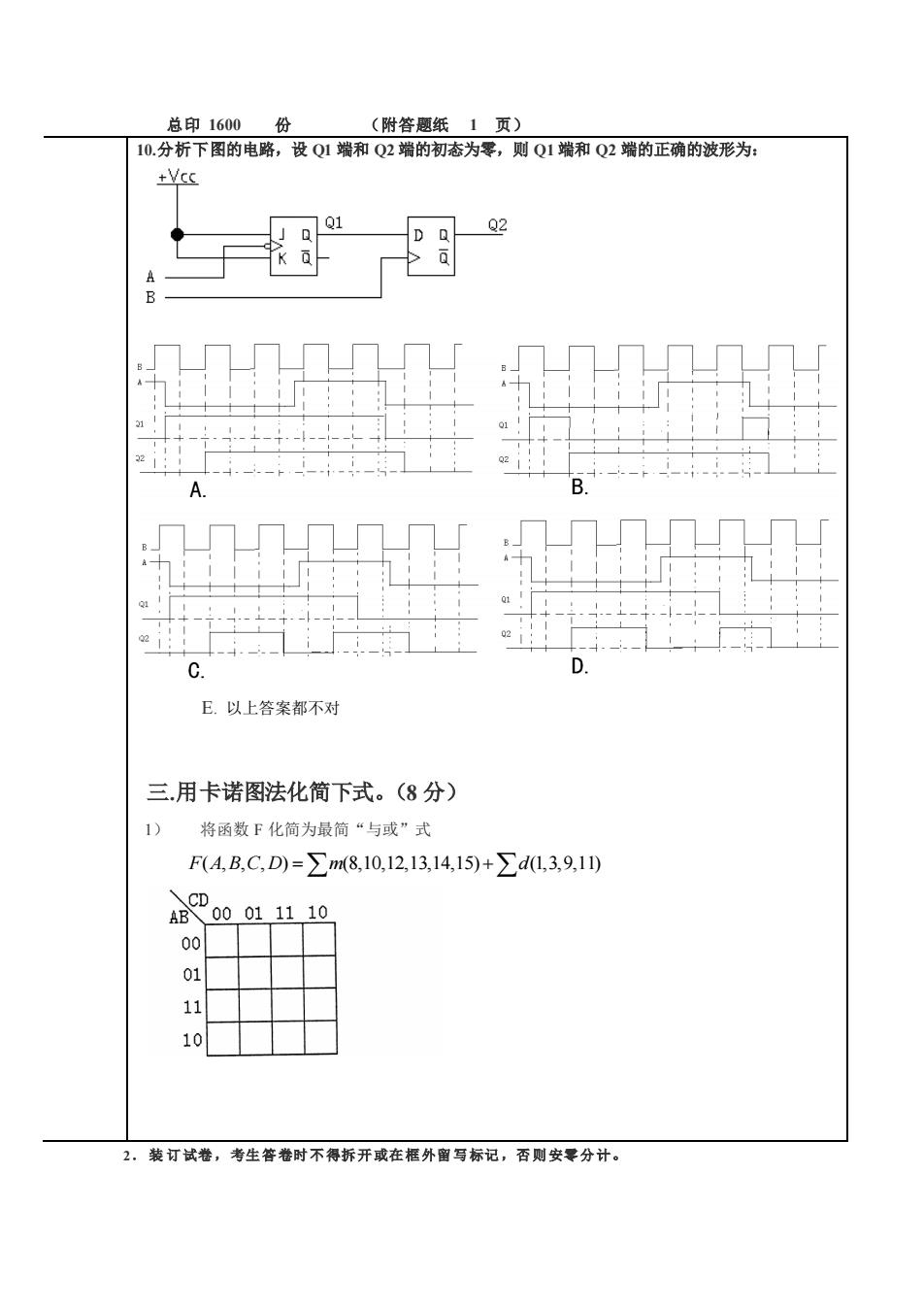

总印1600份 (附答题纸1页) 10.分析下图的电略,设Q1端和Q2端的初态为零,则Q1端和Q2端的正确的波形为: D a - A 2 C. 0 E.以上答案都不对 三用卡诺图法化简下式。(8分) 将函数下化简为最简“与或”式 F(4,B,C,D)=∑nm8,10,12,13,14,15)+∑d1,3,9,1) 00 0 11 10 2。装订试卷,考生答卷时不得拆开或在框外留写标记,否则安零分计

总印 1600 份 (附答题纸 1 页) 10.分析下图的电路,设 Q1 端和 Q2 端的初态为零,则 Q1 端和 Q2 端的正确的波形为: E. 以上答案都不对 三.用卡诺图法化简下式。(8 分) 1) 将函数 F 化简为最简“与或”式 F A B C D m d ( , , , ) (8,10,12,13,14,15) (1,3,9,11) = + 2. 装 订 试卷 , 考生 答 卷时 不 得拆 开 或在 框 外留 写 标记 ,否 则 安零 分 计

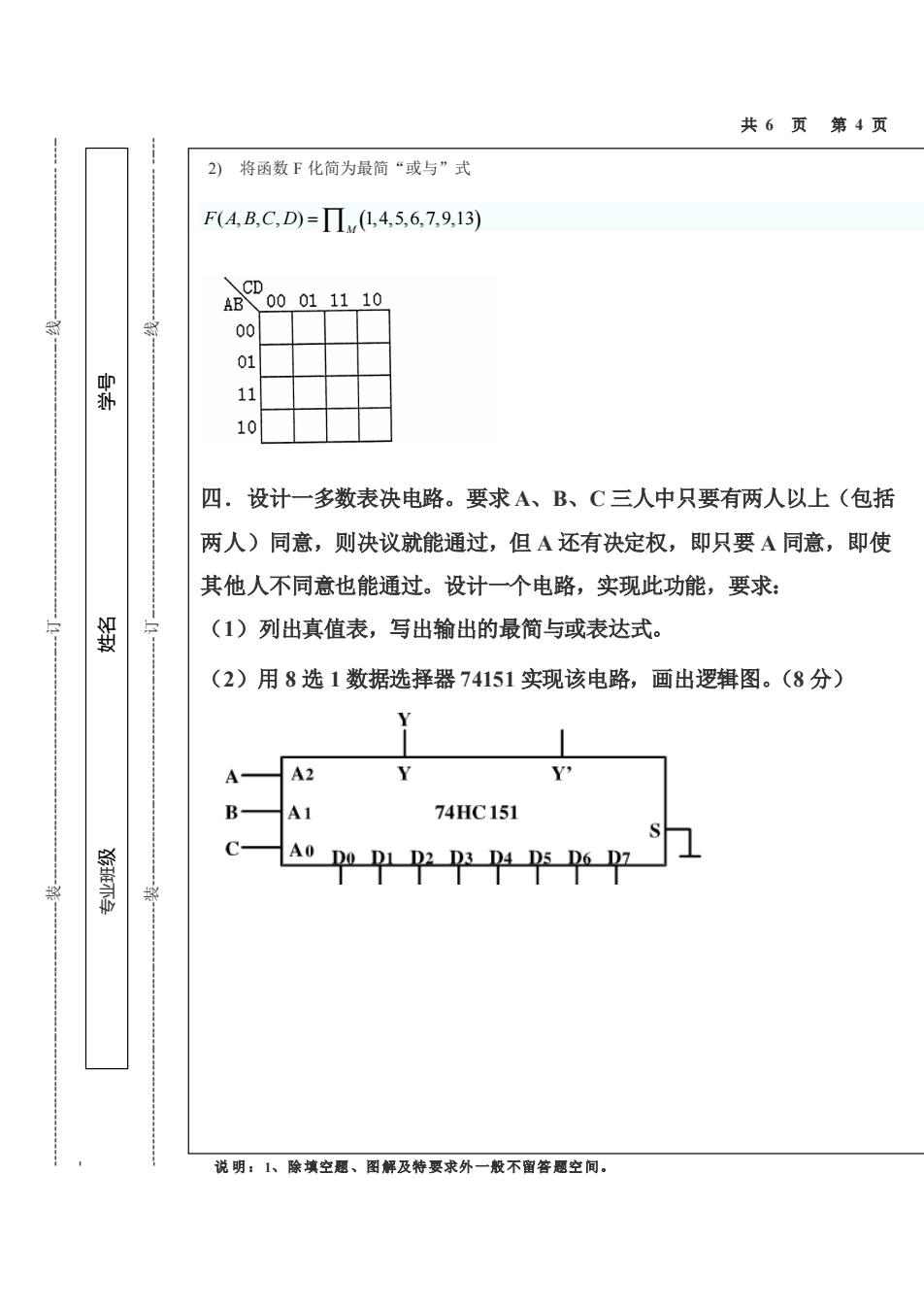

共6页第4页 2)将函数F化简为最简“或与”式 F(4B,C,D)=Π,4,5,67,9,13) ABC000011110 00/ 01 11 10 四.设计一多数表决电路。要求A、B、C三人中只要有两人以上(包括 两人)同意,则决议就能通过,但A还有决定权,即只要A同意,即使 其他人不同意也能通过。设计一个电路,实现此功能,要求: (1)列出真值表,写出输出的最简与或表达式。 (2)用8选1数据选择器74151实现该电路,画出逻辑图。(8分) A A2 B A1 74HC151 说明:1、除填空题、图解及特要求外一般不留答愿空间

共 6 页 第 4 页 - 说 明 : 1、 除 填空题 、图 解及特 要求外 一般 不留答 题空 间。 装- 订- 线- - - - 装- 订- 线- - - 2) 将函数 F 化简为最简“或与”式 ( , , , ) 1,4,5,6,7,9,13 ( ) M F A B C D = 四.设计一多数表决电路。要求 A、B、C 三人中只要有两人以上(包括 两人)同意,则决议就能通过,但 A 还有决定权,即只要 A 同意,即使 其他人不同意也能通过。设计一个电路,实现此功能,要求: (1)列出真值表,写出输出的最简与或表达式。 (2)用 8 选 1 数据选择器 74151 实现该电路,画出逻辑图。(8 分) 专业班 级 姓名 学号

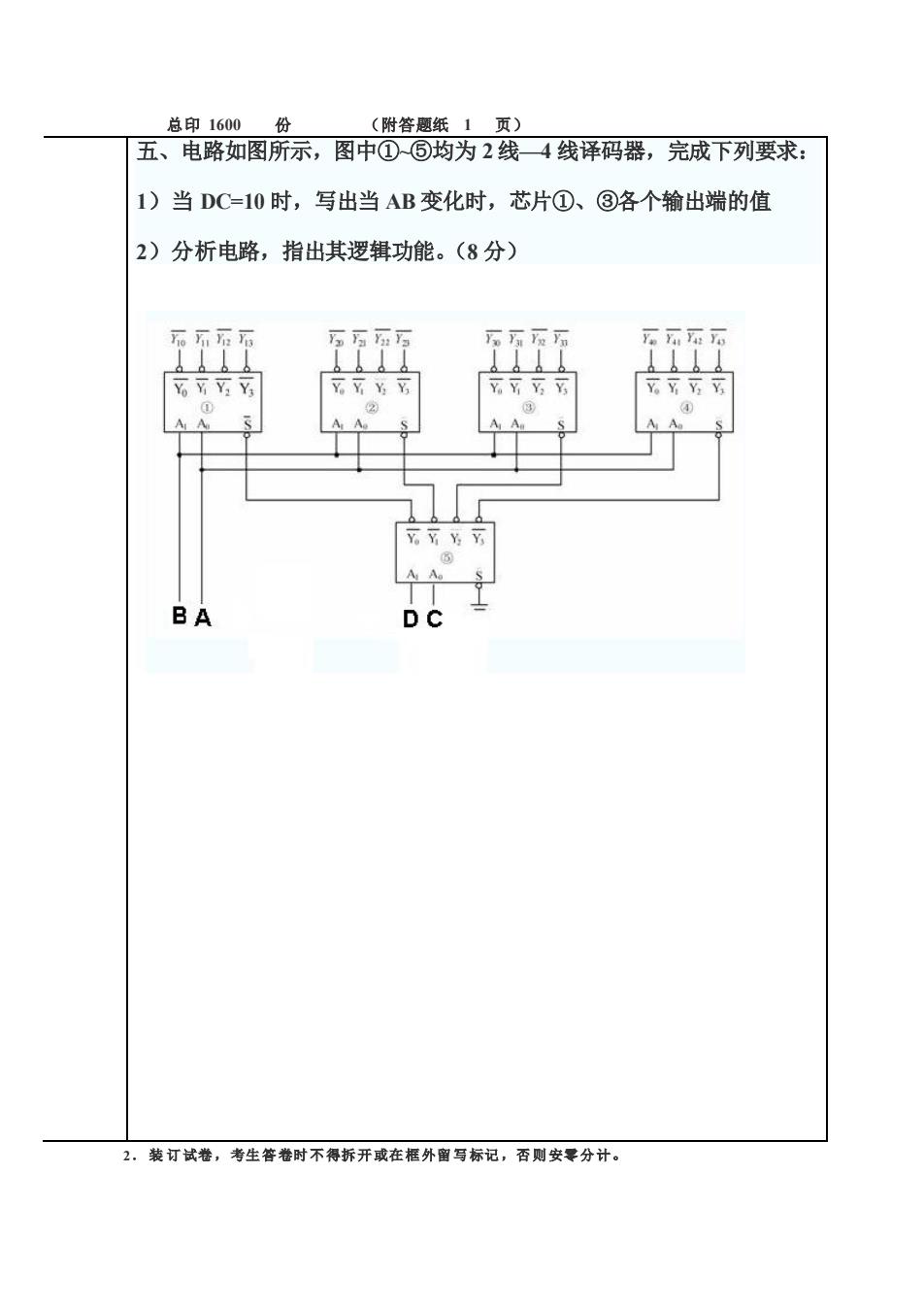

总印1600份 (附答题纸1页) 五、电路如图所示,图中①⑤均为2线一4线译码器,完成下列要求: 1)当DC=10时,写出当AB变化时,芯片①、③各个输出端的值 2)分析电路,指出其逻辑功能。(8分) BA DC 2,装订试卷,考生答卷时不得拆开或在框外留写标记,否则安零分计

总印 1600 份 (附答题纸 1 页) 五、电路如图所示,图中①~⑤均为 2 线—4 线译码器,完成下列要求: 1)当 DC=10 时,写出当 AB 变化时,芯片①、③各个输出端的值 2)分析电路,指出其逻辑功能。(8 分) 2. 装 订 试卷 , 考生 答 卷时 不 得拆 开 或在 框 外留 写 标记 ,否 则 安零 分 计

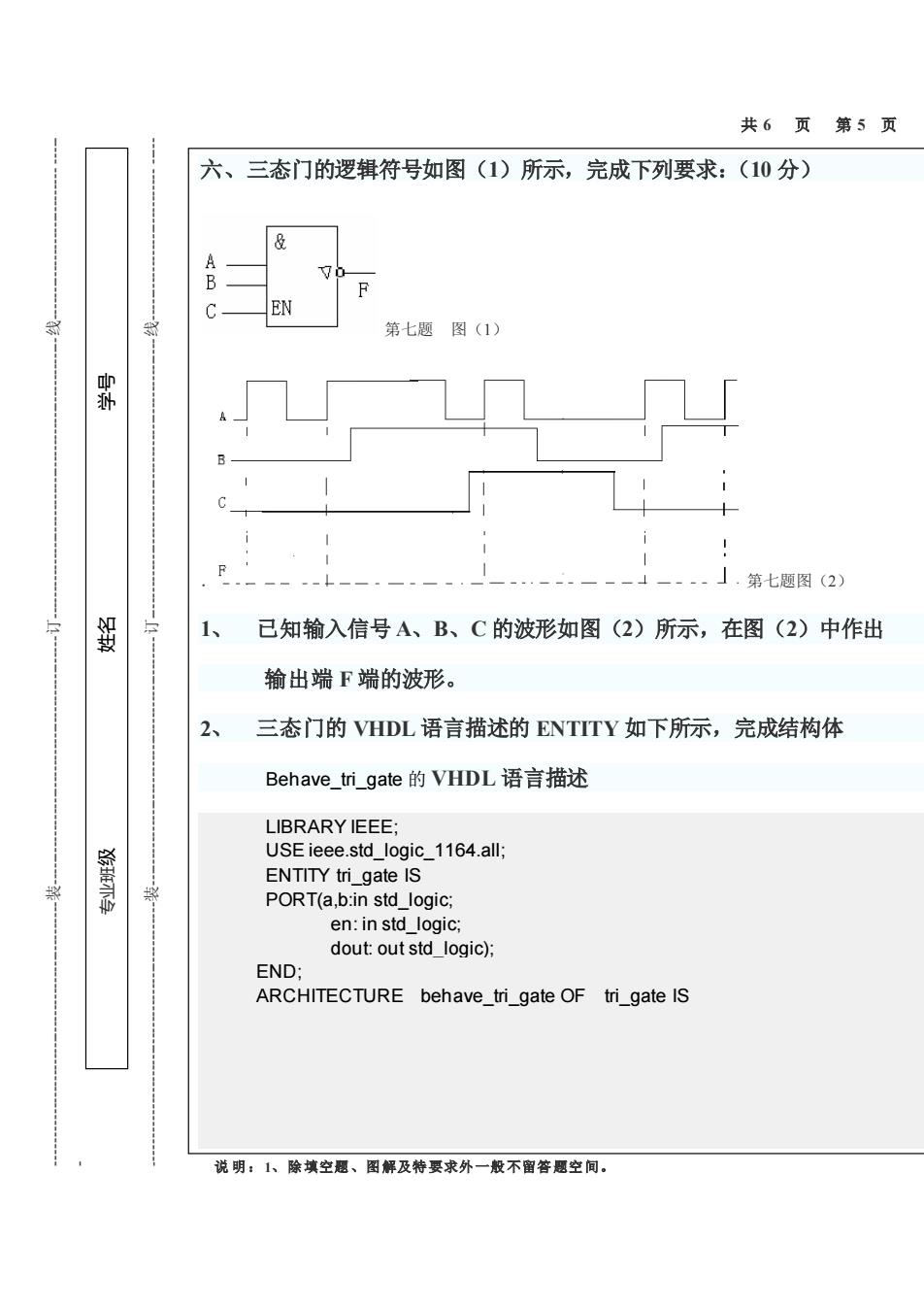

共6页第5页 六、三态门的逻辑符号如图(1)所示,完成下列要求:(10分) C 第七题图(1) F -.一-」一」.第七题图(2) 毁 1、 已知输入信号A、B、C的波形如图(2)所示,在图(2)中作出 输出端F端的波形。 2、 三态门的VHDL语言描述的ENTITY如下所示,完成结构体 Behave tri gate的VHDL语言描述 LBRARY IFEE USEieee.std_logic_1164.all: ENTITY tri_gate IS PORT(a,b:in std_logic; en:in std logic: dout:out std_logic) END ARCHITECTURE behave_tri_gate OF tri_gate IS 说明:1、除填空题、图解及特要求外一般不留答愿空间

共 6 页 第 5 页 - 说 明 : 1、 除 填空题 、图 解及特 要求外 一般 不留答 题空 间。 装- 订- 线- - - - 装- 订- 线- - - 六、三态门的逻辑符号如图(1)所示,完成下列要求:(10 分) 第七题 图(1) . 第七题图(2) 1、 已知输入信号 A、B、C 的波形如图(2)所示,在图(2)中作出 输出端 F 端的波形。 2、 三态门的 VHDL 语言描述的 ENTITY 如下所示,完成结构体 Behave_tri_gate 的 VHDL 语言描述 LIBRARY IEEE; USE ieee.std_logic_1164.all; ENTITY tri_gate IS PORT(a,b:in std_logic; en: in std_logic; dout: out std_logic); END; ARCHITECTURE behave_tri_gate OF tri_gate IS 专业班 级 姓名 学号

总印1600份 (附答题纸1页) 七.用一片四位二进制同步计数器74161设计一个状态从0001~1010的 模10的计数器。(8分) 74161 CLK COUNTER 八.7415为移位寄存器,分析下列电路,要求 1.画出完整的状态转移图: 2.指出电路的逻辑功能。(8分) 1 CLR VCC 6 3 14 4 1 12 6 10 8 CLK CP GND SH/LD 厂启动信号 74195 2。装订试卷,考生答卷时不得拆开或在框外留写标记,否则安零分计

总印 1600 份 (附答题纸 1 页) 七.用一片四位二进制同步计数器 74161 设计一个状态从 0001~1010 的 模 10 的计数器。(8 分) 八.74195 为移位寄存器,分析下列电路,要求: 1.画出完整的状态转移图; 2.指出电路的逻辑功能。(8 分) 2. 装 订 试卷 , 考生 答 卷时 不 得拆 开 或在 框 外留 写 标记 ,否 则 安零 分 计