实验三组合电路设计(一) 1.实验目的 掌握设计组合逻辑电路的方法 ● 过开发CPLD来实现组合逻辑电路的功能 2.示例 (1)数选器74153的VHDL描述。 源程序: Library iece Use ieee.std_logic_1164.all. Entity mux4 is Port(do,d1,d2,d3:in std_logic; Sta,b:in std logic. y:out std_logic). End, Architecture bhv of mux4 is Signal co:std_logic_vector(1 downto 0); Begin Coyy Whem"11"=>yy<='0', End case; End if End process, End; (2)代码转换 要求:输入为8421BCD码,输出为2421码,如表43-1所示

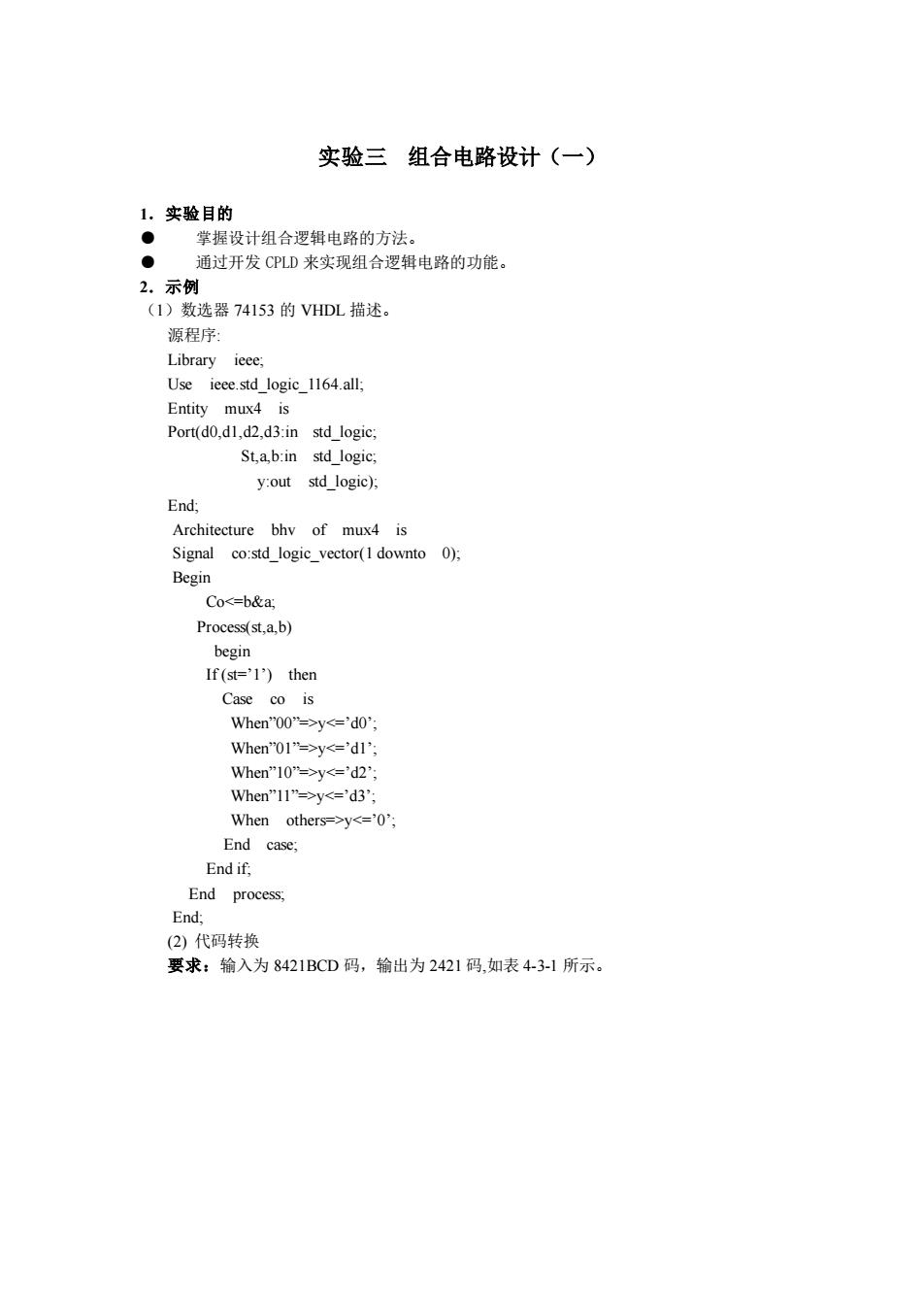

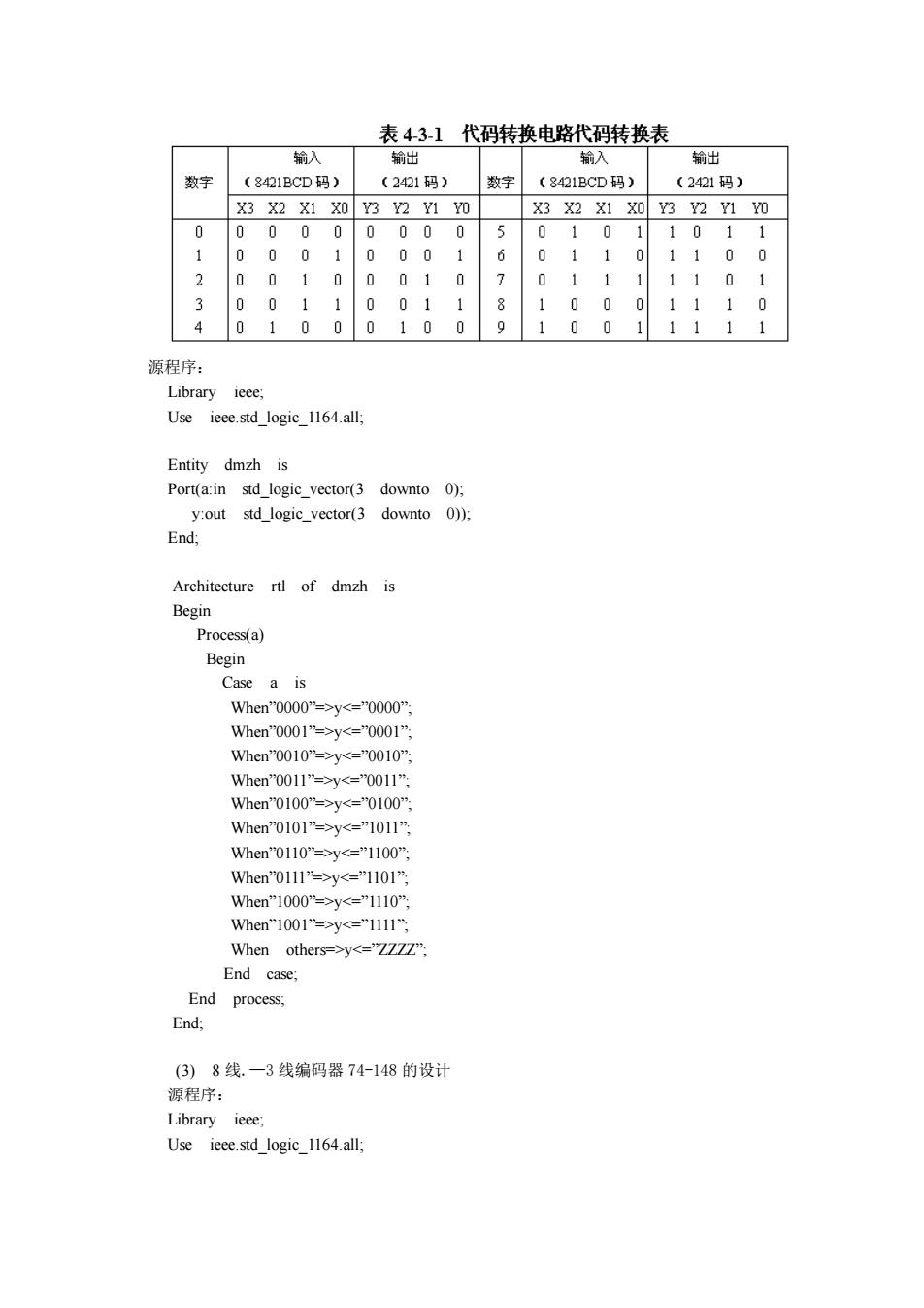

实验三 组合电路设计(一) 1.实验目的 ● 掌握设计组合逻辑电路的方法。 ● 通过开发 CPLD 来实现组合逻辑电路的功能。 2.示例 (1)数选器 74153 的 VHDL 描述。 源程序: Library ieee; Use ieee.std_logic_1164.all; Entity mux4 is Port(d0,d1,d2,d3:in std_logic; St,a,b:in std_logic; y:out std_logic); End; Architecture bhv of mux4 is Signal co:std_logic_vector(1 downto 0); Begin Coyyyyy<=’0’; End case; End if; End process; End; (2) 代码转换 要求:输入为 8421BCD 码,输出为 2421 码,如表 4-3-1 所示

表43】代码转换电路代码转换表 给入 输出 输入 输出 数字 (8421BCD) (2421码) 数字 (8421BCD码) (2421码) 32别 20 Y3 Y2 Y1 YO X32810 0 110 1 0 0 6 0 11 0 0 0 0 0 0 01 0 0 1111101 0 00 1110 1 1 1 源程序: Library ieee Use icee.std_logic_1164.all: Entity dmzh is Port(a:in std_logic_vector(3 downto 0); y:out std_logic_vector(3 downto 0)): End; Architecture rtl of dmzh is Begin Process(a) Begin Case a is Whem0000=>yyyv yyyyy<=" End case; End process, End; (3)8线.一3线编码器74-148的设计 源程序: Library ieee; Use ieee.std_logic_1164.all;

源程序: Library ieee; Use ieee.std_logic_1164.all; Entity dmzh is Port(a:in std_logic_vector(3 downto 0); y:out std_logic_vector(3 downto 0)); End; Architecture rtl of dmzh is Begin Process(a) Begin Case a is When”0000”=>yyyyyyyyyyy<=”ZZZZ”; End case; End process; End; (3) 8 线.—3 线编码器 74-148 的设计 源程序: Library ieee; Use ieee.std_logic_1164.all;

Entity vxbm8 3 is Port(i:in std_logic_vector(7 downto 0). St:in std_logic; Y:out std_logic_vector(2 downto 0); Ys,yex:out std_logic); End: Architecture bhv of yxbm8_3 is Begin Process(i,s) Begin If st='1'then Ys<='l' Yex='1': Else If I(7)='0'then V 000. Ys<='1' Yex<='0'; Elsif I(6)=0°then Y="001: Y= Yex<- 0 Elsif I(5)='0" then Yc="010": Ys<=1': Yex<='0' Elsif I(4)='0'ther Ys<=1: Yex<-'0, Elsif I(3)='0'then Y=”100 Ys<=1 Yx='0', Elsif I(2)='0'then Y<="101": Ys<=1 Yex<=0 Elsif I(1)='0'then Y="110m, Ys<=1': Yex<='0':

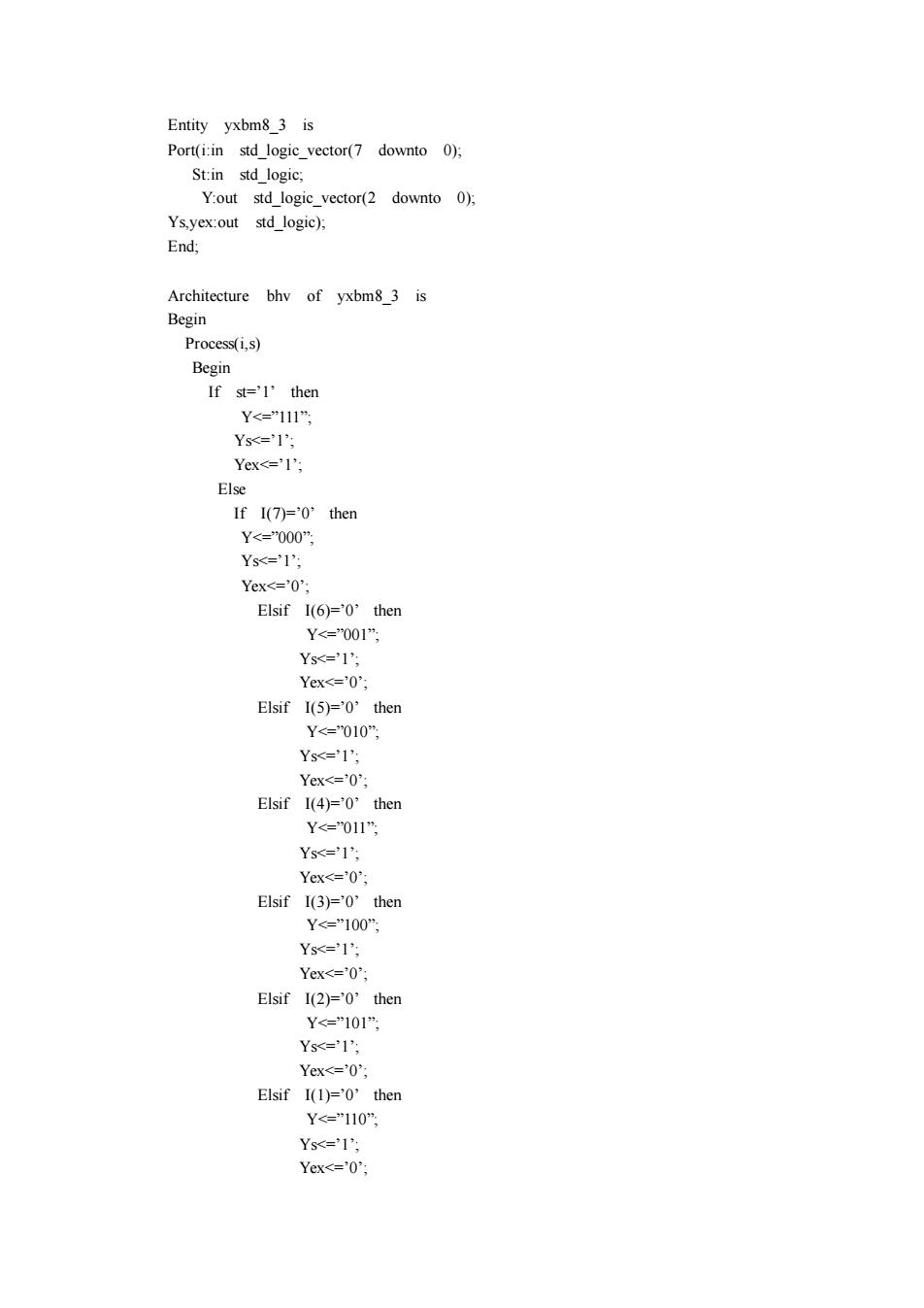

Entity yxbm8_3 is Port(i:in std_logic_vector(7 downto 0); St:in std_logic; Y:out std_logic_vector(2 downto 0); Ys,yex:out std_logic); End; Architecture bhv of yxbm8_3 is Begin Process(i,s) Begin If st=’1’ then Y<=”111”; Ys<=’1’; Yex<=’1’; Else If I(7)=’0’ then Y<=”000”; Ys<=’1’; Yex<=’0’; Elsif I(6)=’0’ then Y<=”001”; Ys<=’1’; Yex<=’0’; Elsif I(5)=’0’ then Y<=”010”; Ys<=’1’; Yex<=’0’; Elsif I(4)=’0’ then Y<=”011”; Ys<=’1’; Yex<=’0’; Elsif I(3)=’0’ then Y<=”100”; Ys<=’1’; Yex<=’0’; Elsif I(2)=’0’ then Y<=”101”; Ys<=’1’; Yex<=’0’; Elsif I(1)=’0’ then Y<=”110”; Ys<=’1’; Yex<=’0’;

Elsif I(0)='0'then y”111” Yex<=0 ElsifI=”1 mm1”then Y=”111” Ys=0: Yex<=1'. End if. End if: End process, End 3.实验内容 (1)多数表决电略设计 a.要求:当输入A、B、C、D有3个或3个以上为1时输出F为1:输入为其他状态 时输出为0。 b.写出实验内容的真值表及逻辑表达式。 c.编写出实现该电路的VHDL程序。 d.用MX+plusII进行仿真, ©.将编写好的程序下载到CPLD芯片里,观察结果 (2)代码转换电路设计 a.要求:输入为8421BCD码,输出为余3码,如表4-3-2所示。 表432代码转换电路代码转换表 输出 数字 (8421BCD码)〔余3码) 数字(8421BCD码) 〔余3码) 32X10321w X3 X2 X1 XO Y3 Y2 YI Y0 00000011 5 0101 1000 10 10 1 100 1 0 1 0 0 0 0 1 0 0 0 0 0 10 1 4 0 100011 1 9 1 00 1 1100 b.按照实验内容及代码转换表,写出逻辑表达式。 c编写出实现该电路的VHDL程序。 d.用MAK+plusII进行仿真。 e.将编写好的程序下载到CPLD芯片里,观察结果。 4.注意率项 (1)电路的编程要根据要求及真值表,要考虑输入所有可能出现的情况,尽量简洁 (2)仿真信号要包括所有端子的各种情况。 (3)测试信号要包括所有端子的各种情况 5.预习要求 (1)复习有关组合逻辑电路的设计方法,分析其逻辑功能,写出其真值表及逻辑表达 式

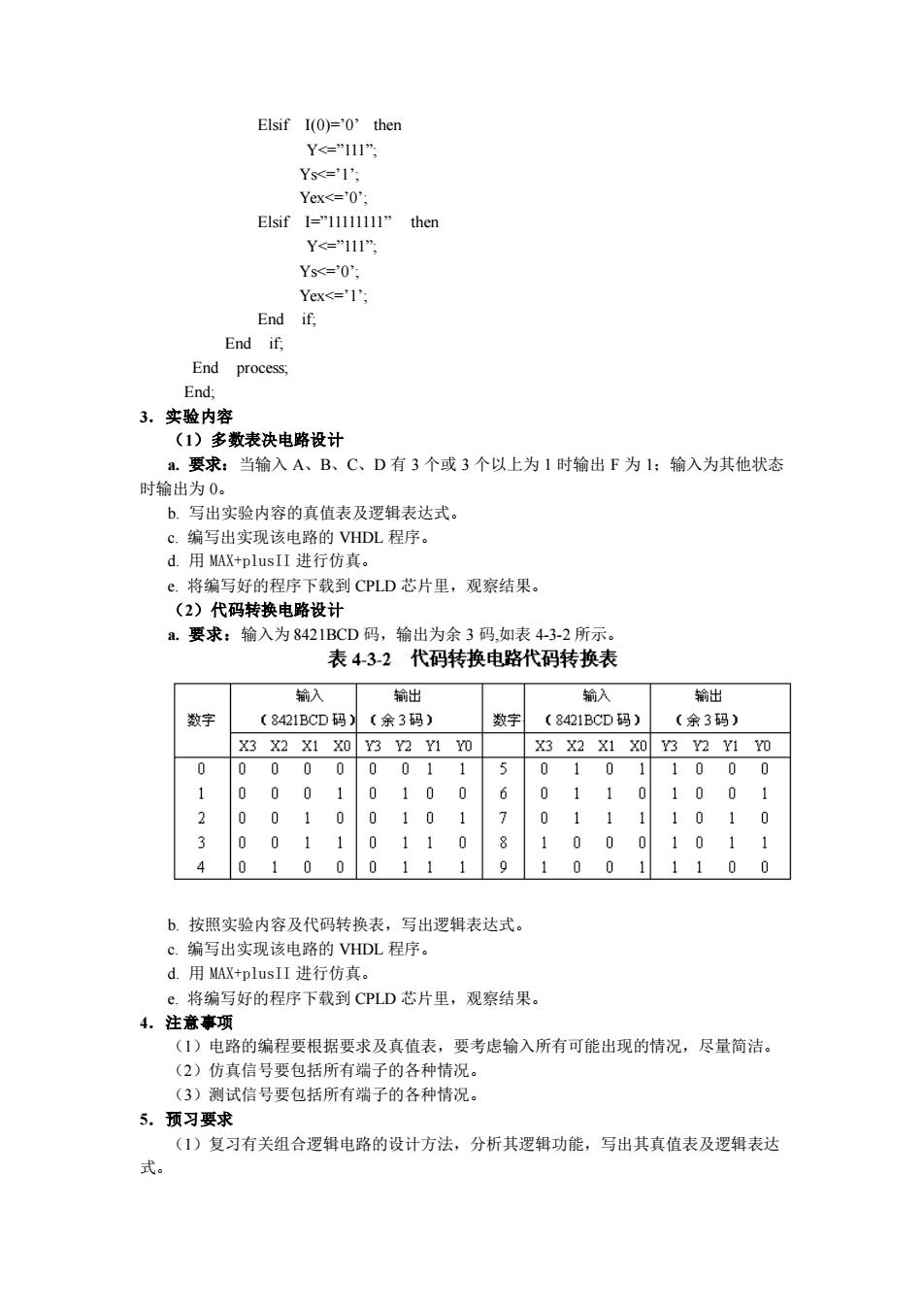

Elsif I(0)=’0’ then Y<=”111”; Ys<=’1’; Yex<=’0’; Elsif I=”11111111” then Y<=”111”; Ys<=’0’; Yex<=’1’; End if; End if; End process; End; 3.实验内容 (1)多数表决电路设计 a. 要求:当输入 A、B、C、D 有 3 个或 3 个以上为 1 时输出 F 为 1;输入为其他状态 时输出为 0。 b. 写出实验内容的真值表及逻辑表达式。 c. 编写出实现该电路的 VHDL 程序。 d. 用 MAX+plusII 进行仿真。 e. 将编写好的程序下载到 CPLD 芯片里,观察结果。 (2)代码转换电路设计 a. 要求:输入为 8421BCD 码,输出为余 3 码,如表 4-3-2 所示。 b. 按照实验内容及代码转换表,写出逻辑表达式。 c. 编写出实现该电路的 VHDL 程序。 d. 用 MAX+plusII 进行仿真。 e. 将编写好的程序下载到 CPLD 芯片里,观察结果。 4.注意事项 (1)电路的编程要根据要求及真值表,要考虑输入所有可能出现的情况,尽量简洁。 (2)仿真信号要包括所有端子的各种情况。 (3)测试信号要包括所有端子的各种情况。 5.预习要求 (1)复习有关组合逻辑电路的设计方法,分析其逻辑功能,写出其真值表及逻辑表达 式

(2)分析输入信号的所有情况,进行记录,便于实验进行验证。 (3)自己绘制激励波形,考虑输入端子的各种情况。 6.实验报告 根据以上的实验内容写出实验报告:包括程序设计、软件编译、(功能、时序)仿真分析、 硬件测试和和分析:设计程序、程序分析报告、仿真波形图及其分析报告

(2)分析输入信号的所有情况,进行记录,便于实验进行验证。 (3)自己绘制激励波形,考虑输入端子的各种情况。 6.实验报告 根据以上的实验内容写出实验报告:包括程序设计、软件编译、(功能、时序)仿真分析、 硬件测试和和分析;设计程序、程序分析报告、仿真波形图及其分析报告