正在加载图片...

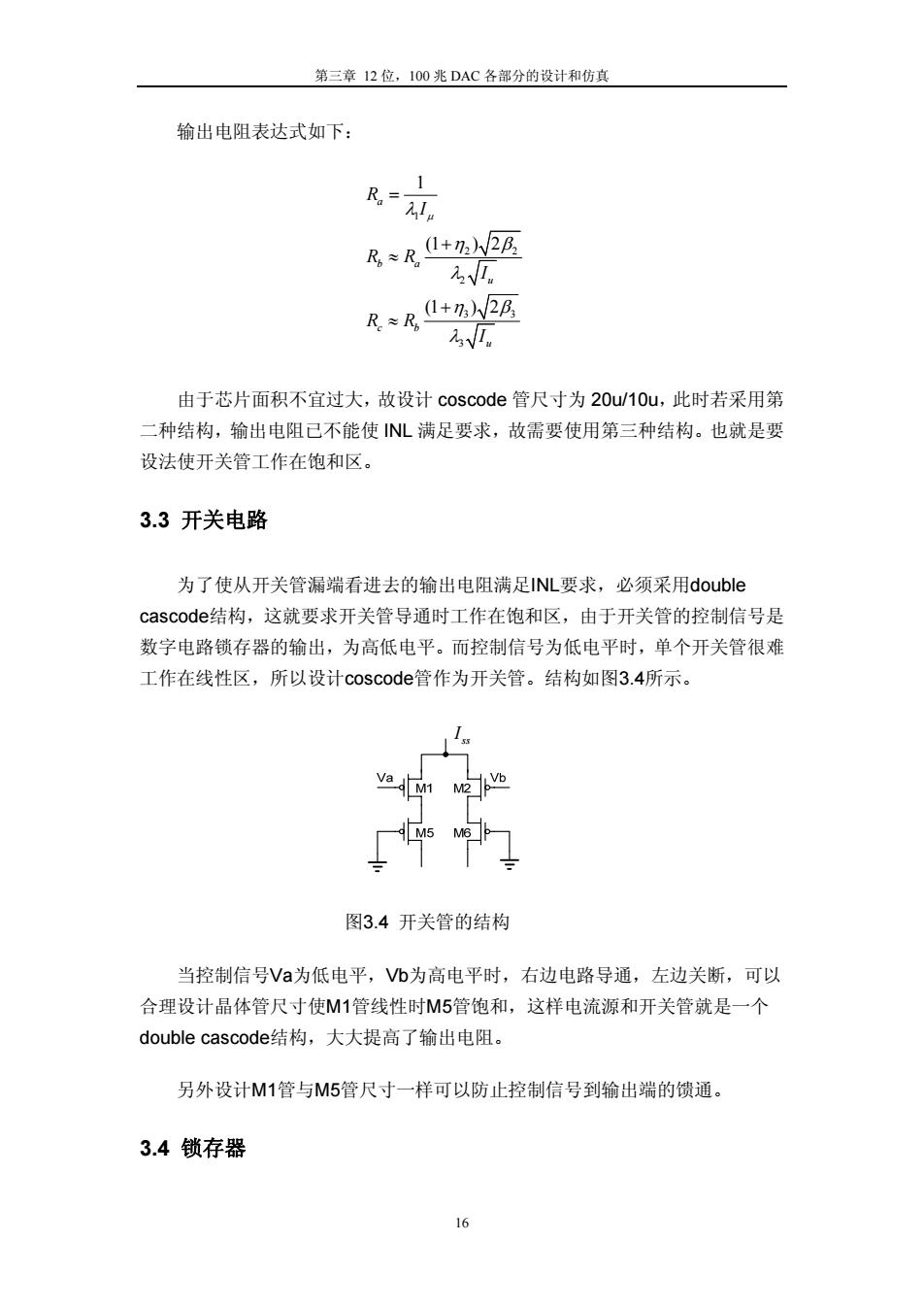

第三章12位,I00兆DAC各部分的设计和仿真 输出电阻表达式如下: 1 R≈R+h2g 乃Vm 1+)W2β R≈R, N 由于芯片面积不宜过大,故设计coscode管尺寸为20u/10u,此时若采用第 二种结构,输出电阻己不能使NL满足要求,故需要使用第三种结构。也就是要 设法使开关管工作在饱和区。 3.3开关电路 为了使从开关管漏端看进去的输出电阻满足INL要求,必须采用double cascode结构,这就要求开关管导通时工作在饱和区,由于开关管的控制信号是 数字电路锁存器的输出,为高低电平。而控制信号为低电平时,单个开关管很难 工作在线性区,所以设计coscode管作为开关管。结构如图3.4所示。 图3.4开关管的结构 当控制信号Va为低电平,Vb为高电平时,右边电路导通,左边关断,可以 合理设计晶体管尺寸使M1管线性时M5管饱和,这样电流源和开关管就是一个 double cascode结构,大大提高了输出电阻。 另外设计M1管与M5管尺寸一样可以防止控制信号到输出端的馈通。 3.4锁存器 16第三章 12 位,100 兆 DAC 各部分的设计和仿真 16 输出电阻表达式如下: 1 2 2 2 3 3 3 1 (1 ) 2 (1 ) 2 a b a u c b u R I R R I R R I λ μ η β λ η β λ = + ≈ + ≈ 由于芯片面积不宜过大,故设计 coscode 管尺寸为 20u/10u,此时若采用第 二种结构,输出电阻已不能使 INL 满足要求,故需要使用第三种结构。也就是要 设法使开关管工作在饱和区。 3.3 开关电路 为了使从开关管漏端看进去的输出电阻满足INL要求,必须采用double cascode结构,这就要求开关管导通时工作在饱和区,由于开关管的控制信号是 数字电路锁存器的输出,为高低电平。而控制信号为低电平时,单个开关管很难 工作在线性区,所以设计coscode管作为开关管。结构如图3.4所示。 ss I 图3.4 开关管的结构 当控制信号Va为低电平,Vb为高电平时,右边电路导通,左边关断,可以 合理设计晶体管尺寸使M1管线性时M5管饱和,这样电流源和开关管就是一个 double cascode结构,大大提高了输出电阻。 另外设计M1管与M5管尺寸一样可以防止控制信号到输出端的馈通。 3.4 锁存器