正在加载图片...

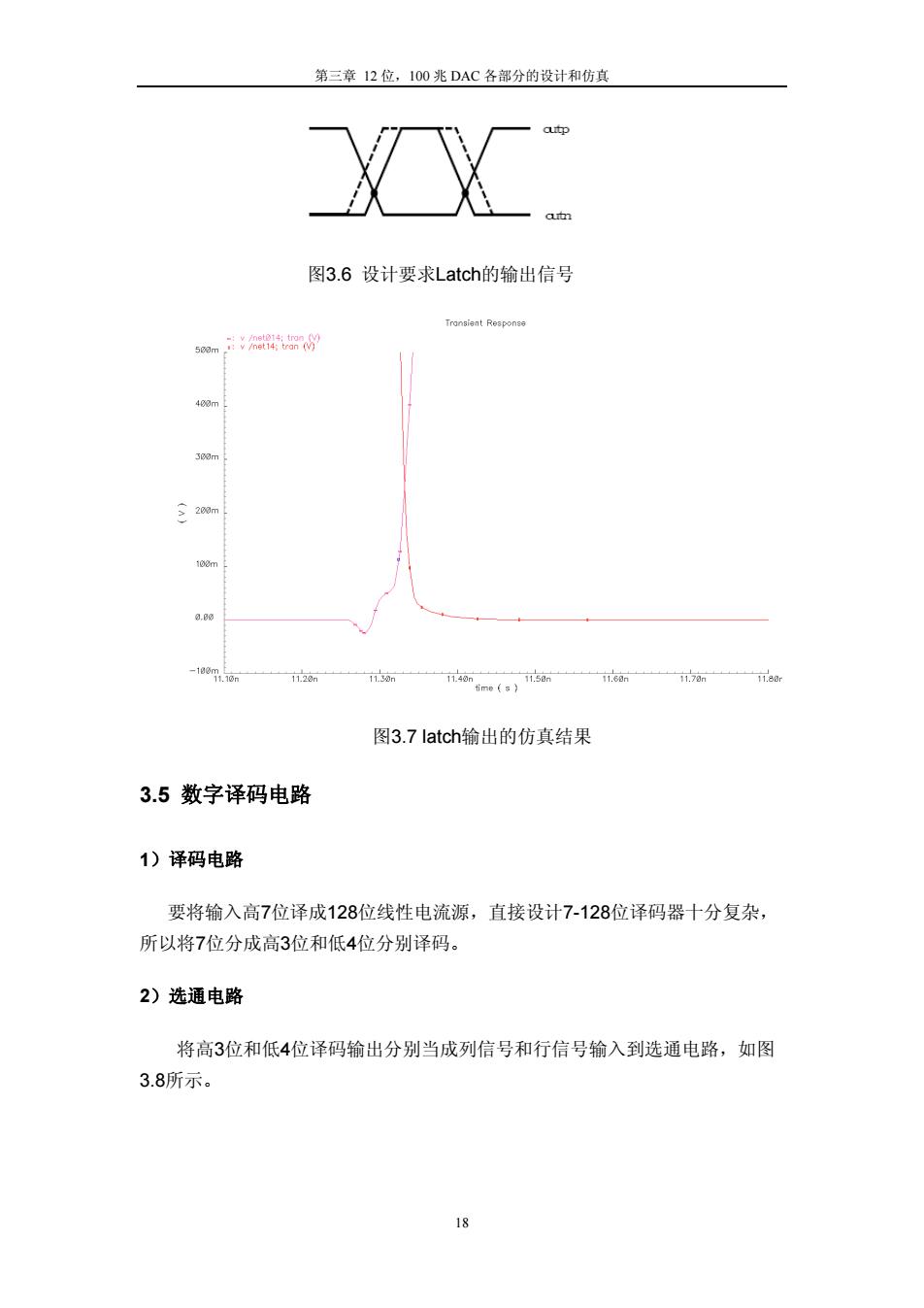

第三章12位,1O0兆DAC各部分的设计和仿真 图3.6设计要求Latch的输出信号 Tronsient Response 50am¥e4 403m 50m 三200m 100m 0.00 一18091.1@n 11.20n 1i.50n 11.40n 11.7an 1i. 节me(s) 图3.7 latch输出的仿真结果 3.5数字译码电路 1)译码电路 要将输入高7位译成128位线性电流源,直接设计7-128位译码器十分复杂, 所以将7位分成高3位和低4位分别译码。 2)选通电路 将高3位和低4位译码输出分别当成列信号和行信号输入到选通电路,如图 3.8所示。 8第三章 12 位,100 兆 DAC 各部分的设计和仿真 18 图3.6 设计要求Latch的输出信号 图3.7 latch输出的仿真结果 3.5 数字译码电路 1)译码电路 要将输入高7位译成128位线性电流源,直接设计7-128位译码器十分复杂, 所以将7位分成高3位和低4位分别译码。 2)选通电路 将高3位和低4位译码输出分别当成列信号和行信号输入到选通电路,如图 3.8所示