易建助编著《计算机维修技术第2版》 附件3-6:DDR2内存引脚信号 《计算机维修技术第2版》 易建勋编著 清华大学出版社2009.8 附件3-6:64位DDR2 SDRAM Unb-DMM内存条引脚功能定义(240脚) Pin Name Pin Name Pin Name Pin Name Pin Name Pin Name VREF 41 VSS 81 DQ33 121 VSS 161 NC(CB4) 201 VSS 2 VSS 42 NC(CBO)* 82 VSS 122 DQ4 162 NC(CB5)* 202 DM4 2 DQ0 43 NC(CBI)* 83 DQS4 123 DQ5 163 VSS 203 NC DQI 44 VSs 84 DQS4 124 VSS 164 NC(DM8)* 204 VSS 5 VSS 45 NC(DOS8* 85 VSS 125 DMO 165 NC 205 DO38 6 DQSO 46 NC(DQS8)* 86 DQ34 126 NC 166 VSS 206 DQ39 7 DOSO 47 VSS 87 DQ35 127 VSS 167 NC(CB6)* 207 VSS VSS 48 NC(CB2)* 88 VSS 128 DQ6 168 NC(CB7)* 208 DQ44 9 DQ2 49 NC(CB3)* 89 DQ40 129 DQ7 169 VSS 209 DQ45 10 DQ3 50 VSS 90 DQ41 130 VSS 170 VDDQ 210 VSS 11 VSS 51 VDDQ 91 VSS 131 DQ12 171 CKE1 211 DM5 12 DQ8 52 CKEO 92 DOS5 132 DQ13 172 VDD 212 NC 13 DQ9 53 VDD 93 DQS5 133 VSS 173 A15 213 VSS 14 VSS 54 BA2 94 VSS 134 DMI 174 A14 214 DQ46 5 DOSI 55 NC 95 DO42 135 NC 175 VDDQ 215 D047 16 DQSI 56 VDDQ 96 DQ43 136 VSS 176 A12 216 VSS 17 VSS 57 A11 97 VSS 137 CKI 177 A9 217 D052 18 NC 58 A7 98 DQ48 138 CKI 178 VDD 218 DQ53 19 NC 59 VDD 99 DQ49 139 VSS 179 A8 219 VSS 20 VSS 60 A5 100 VSS 140 DQ14 180 A6 220 CK2 21 DO1O 61 A4 101 SA2 141 DO15 181 VDDO 221 CK2

易建勋 编著《计算机维修技术 第 2 版》 附件 3-6:DDR2 内存引脚信号 《计算机维修技术 第 2 版》 易建勋 编著 清华大学出版社 2009.8 附件 3-6:64 位 DDR2 SDRAM Unb-DIMM 内存条引脚功能定义(240 脚) Pin Name Pin Name Pin Name Pin Name Pin Name Pin Name 1 VREF VREF 41 VSS 81 DQ33 121 VSS 161 NC(CB4) 201 VSS 2 VSS 42 NC(CB0)* 82 VSS 122 DQ4 162 NC(CB5)* 202 DM4 3 DQ0 43 NC(CB1)* 83 DQS4 123 DQ5 163 VSS 203 NC 4 DQ1 44 VSS 84 DQS4 124 VSS 164 NC(DM8)* 204 VSS 5 VSS 45 NC(DQS8)* 85 VSS 125 DM0 165 NC 205 DQ38 6 DQS0 46 NC(DQS8)* 86 DQ34 126 NC 166 VSS 206 DQ39 7 DQS0 47 VSS 87 DQ35 127 VSS 167 NC(CB6)* 207 VSS 8 VSS 48 NC(CB2)* 88 VSS 128 DQ6 168 NC(CB7)* 208 DQ44 9 DQ2 49 NC(CB3)* 89 DQ40 129 DQ7 169 VSS 209 DQ45 10 DQ3 50 VSS 90 DQ41 130 VSS 170 VDDQ VDDQ 210 VSS 11 VSS 51 VDDQ 91 VSS 131 DQ12 171 CKE1 CKE1 211 DM5 12 DQ8 52 CKE0 CKE0 92 DQS5 132 DQ13 172 VDD VDD 212 NC 13 DQ9 53 VDD VDD 93 DQS5 133 VSS 173 A15 213 VSS 14 VSS 54 BA2 94 VSS 134 DM1 174 A14 214 DQ46 15 DQS1 55 NC 95 DQ42 135 NC 175 VDDQ 215 DQ47 16 DQS1 56 VDDQ 96 DQ43 136 VSS 176 A12 216 VSS 17 VSS 57 A11 97 VSS 137 CK1 CK1 177 A9 217 DQ52 18 NC 58 A7 98 DQ48 138 CK1 CK1 178 VDD VDD 218 DQ53 19 NC 59 VDD VDD 99 DQ49 139 VSS 179 A8 219 VSS 20 VSS 60 A5 100 VSS 140 DQ14 180 A6 220 CK2 CK2 21 DQ10 61 A4 101 SA2 141 DQ15 181 VDDQ 221 CK2 CK2

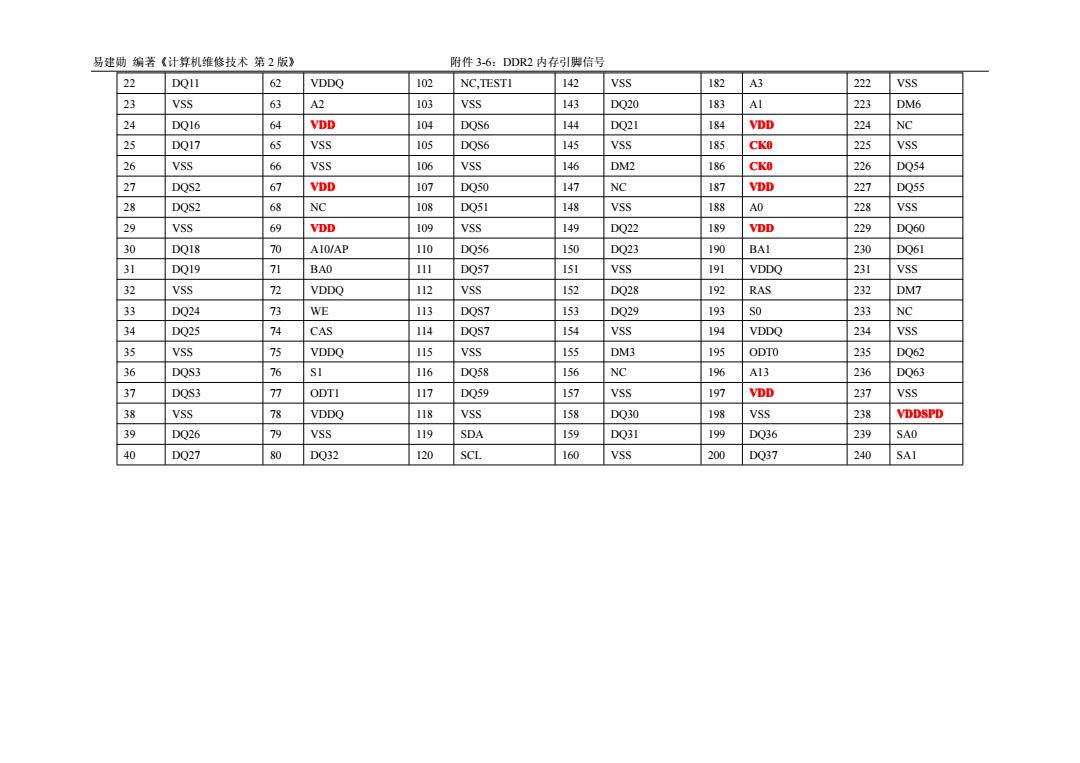

易建助编著《计算机维修技术第2版》 附件3-6:DDR2内存引脚信号 22 DQ1I 62 VDDQ 102 NC,TESTI 142 VSS 182 A3 222 VSS 23 VSS 63 A2 103 VSS 143 DQ20 183 Al 223 DM6 24 DO16 64 VDD 104 DOS6 144 DQ21 184 VDD 224 NC 25 DQ17 65 VSS 105 DOS6 145 VSS 185 CKO 225 VSS 26 VSS 66 VSS 106 VSS 146 DM2 186 CKO 226 DQ54 27 DQS2 67 VDD 107 DQ50 147 NC 187 VDD 227 DQ55 28 DQS2 68 NC 108 DO51 148 VSS 188 A0 228 VSS 29 VSS 69 VDD 109 VSS 149 DQ22 189 VDD 229 DQ60 30 DQ18 70 A10/AP 110 DQ56 150 DQ23 190 BAI 230 DQ61 31 DQ19 71 BAO 111 DQ57 151 VSS 191 VDDQ 231 VSS 32 VSS 72 VDDO 112 VSS 152 DQ28 192 RAS 232 DM7 33 DO24 73 WE 113 DOS7 153 D029 193 SO 233 NC 34 D025 74 CAS 114 DQS7 154 VSS 194 VDDQ 234 VSS 35 VSS 75 VDDO 115 VSS 155 DM3 195 ODTO 235 DQ62 36 DQS3 76 SI 116 DQ58 156 NC 196 A13 236 DQ63 37 DOS3 77 ODTI 117 DQ59 157 VSS 197 VDD 237 VSS 38 VSS 78 VDDQ 118 VSS 158 DQ30 198 Vss 238 VDDSPD 39 DQ26 79 VSS 119 SDA 159 DQ31 199 DQ36 239 SAO 40 DQ27 80 DO32 120 SCL 160 VSS 200 DQ37 240 SAl

易建勋 编著《计算机维修技术 第 2 版》 附件 3-6:DDR2 内存引脚信号 22 DQ11 62 VDDQ 102 NC,TEST1 142 VSS 182 A3 222 VSS 23 VSS 63 A2 103 VSS 143 DQ20 183 A1 223 DM6 24 DQ16 64 VDD VDD 104 DQS6 144 DQ21 184 VDD VDD 224 NC 25 DQ17 65 VSS 105 DQS6 145 VSS 185 CK0 CK0 225 VSS 26 VSS 66 VSS 106 VSS 146 DM2 186 CK0 CK0 226 DQ54 27 DQS2 67 VDD VDD 107 DQ50 147 NC 187 VDD VDD 227 DQ55 28 DQS2 68 NC 108 DQ51 148 VSS 188 A0 228 VSS 29 VSS 69 VDD VDD 109 VSS 149 DQ22 189 VDD VDD 229 DQ60 30 DQ18 70 A10/AP 110 DQ56 150 DQ23 190 BA1 230 DQ61 31 DQ19 71 BA0 111 DQ57 151 VSS 191 VDDQ 231 VSS 32 VSS 72 VDDQ 112 VSS 152 DQ28 192 RAS 232 DM7 33 DQ24 73 WE 113 DQS7 153 DQ29 193 S0 233 NC 34 DQ25 74 CAS 114 DQS7 154 VSS 194 VDDQ 234 VSS 35 VSS 75 VDDQ 115 VSS 155 DM3 195 ODT0 235 DQ62 36 DQS3 76 S1 116 DQ58 156 NC 196 A13 236 DQ63 37 DQS3 77 ODT1 117 DQ59 157 VSS 197 VDD VDD 237 VSS 38 VSS 78 VDDQ 118 VSS 158 DQ30 198 VSS 238 VDDSPD VDDSPD 39 DQ26 79 VSS 119 SDA 159 DQ31 199 DQ36 239 SA0 40 DQ27 80 DQ32 120 SCL 160 VSS 200 DQ37 240 SA1

易建助编著《计算机维修技术第2版》 附件3-6:DDR2内存引脚信号 DDR2内存引脚 Front Back Pin Symbol Pin Symbol Pin Symbol Pin Symbol Pin Symbol Pin Symbol Pin Symbol Pin Symbol VREF 31 DO19 61 A4 91 VSS 121 VSS 151 VSS 181 VDDO 211 DM5/DQS14 2 VSS 32 VSS 62 VDDQ 92 DQS5# 122 DQ4 152 DQ28 182 A3 212 NC/DOS14# 3 DOO 33 DQ24 63 A2 93 DOS5 123 DO5 153 DQ29 183 Al 213 VSS 4 DOI 34 D025 64 VDD 94 VSS 124 VSS 154 VSS 184 VDD 214 DQ46 5 VSS 35 VSS 65 VSS 95 DQ42 125 DMO/DOS9 155 DM3/DOS12 185 CKO 215 D047 6 DOSO# 36 DQS3# 66 VSS 96 DQ43 126 NC/DOS9# 156 NC/DOS12# 186 CKO# 216 VSS DOSO 37 DQS3 67 VDD 97 VSS 127 VSS 157 VSS 187 VDD 217 DQ52 VSS 38 VSS 68 PAR IN 98 DQ48 128 DQ6 158 DQ30 188 A0 218 DQ53 D02 39 DO26 69 VDD 99 D049 129 DQ7 159 DQ31 189 VDD 219 VSS 10 DQ3 40 DQ27 70 Al0/AP 100 VSS 130 VSS 160 VSS 190 BAI 220 RFU VSS 41 VSS 71 BAO 101 SA2 131 DQ12 161 CB4 191 VDDO 221 RFU 12 DQ8 42 CBO 72 VDDQ 102 NC 132 DQ13 162 CB5 192 RAS# 222 VSS 13 DQ9 43 CBI 73 WE# 103 VSS 133 VSS 163 VSS 193 S04 223 DM6/DOS15 14 VSS 44 VSS 74 CAS# 104 D0S64 134 DMI/DOS10 164 DM8/DOS17 194 VDDQ 224 NC/DOS15# 15 DOSI# 45 DOS8# 75 VDDQ 105 DQS6 135 NC/DQS10# 165 NC/DQS17# 195 ODTO 225 VSS 16 DOSI 46 DOS8 76 SI# 106 VSS 136 VSS 166 VSS 196 NC/A13 226 DQ54 17 VSS 47 VsS 77 ODTI 107 DQ50 137 RFU 167 CB6 197 VDD 227 DQ55 18 RESET# 48 CB2 78 VDDQ 108 DQ5I 138 RFU 168 CB7 198 VSS 228 VSS 19 NC 49 CB3 79 VSS 109 VSS 139 VSS 169 VSS 199 DQ36 229 DQ60 20 VSS 50 VSS 80 DQ32 110 DQ56 140 DQ14 170 VDDQ 200 DQ37 230 DQ61 21 DQ10 51 VDDQ 81 DQ33 111 DQ57 141 DQI5 171 CKEI 201 VSS 231 VSS 22 DOII 52 CKEO 82 VSS 112 VSS 142 VSS 172VDD 202 DM4/DOS13 232 DM7/DOS16 23 VSS 53 VDD 83 DOS4# 1I3 DOS7# 143 DQ20 173 NC 203 NC/DOS13# 233 NC/DQS16# 24 DQ16 54 NC/BA2 84 DQS4 114 DOS7 144 DQ21 174 NC 204 VSS 234 VSS 25 DQ17 55 ERR OUT 85 VSS 1I5 VSS 145 VSS 175 VDDQ 205 DO38 235 DQ62

易建勋 编著《计算机维修技术 第 2 版》 附件 3-6:DDR2 内存引脚信号 DDR2 内存引脚 Front Back Pin Symbol Pin Symbol Pin Symbol Pin Symbol Pin Symbol Pin Symbol Pin Symbol Pin Symbol 1 VREF 31 DQ19 61 A4 91 VSS 121 VSS 151 VSS 181 VDDQ 211 DM5/DQS14 2 VSS 32 VSS 62 VDDQ 92 DQS5# 122 DQ4 152 DQ28 182 A3 212 NC/DQS14# 3 DQ0 33 DQ24 63 A2 93 DQS5 123 DQ5 153 DQ29 183 A1 213 VSS 4 DQ1 34 DQ25 64 VDD 94 VSS 124 VSS 154 VSS 184 VDD 214 DQ46 5 VSS 35 VSS 65 VSS 95 DQ42 125 DM0/DQS9 155 DM3/DQS12 185 CK0 215 DQ47 6 DQS0# 36 DQS3# 66 VSS 96 DQ43 126 NC/DQS9# 156 NC/DQS12# 186 CK0# 216 VSS 7 DQS0 37 DQS3 67 VDD 97 VSS 127 VSS 157 VSS 187 VDD 217 DQ52 8 VSS 38 VSS 68 PAR_IN 98 DQ48 128 DQ6 158 DQ30 188 A0 218 DQ53 9 DQ2 39 DQ26 69 VDD 99 DQ49 129 DQ7 159 DQ31 189 VDD 219 VSS 10 DQ3 40 DQ27 70 A10/AP 100 VSS 130 VSS 160 VSS 190 BA1 220 RFU 11 VSS 41 VSS 71 BA0 101 SA2 131 DQ12 161 CB4 191 VDDQ 221 RFU 12 DQ8 42 CB0 72 VDDQ 102 NC 132 DQ13 162 CB5 192 RAS# 222 VSS 13 DQ9 43 CB1 73 WE# 103 VSS 133 VSS 163 VSS 193 S0# 223 DM6/DQS15 14 VSS 44 VSS 74 CAS# 104 DQS6# 134 DM1/DQS10 164 DM8/DQS17 194 VDDQ 224 NC/DQS15# 15 DQS1# 45 DQS8# 75 VDDQ 105 DQS6 135 NC/DQS10# 165 NC/DQS17# 195 ODT0 225 VSS 16 DQS1 46 DQS8 76 S1# 106 VSS 136 VSS 166 VSS 196 NC/A13 226 DQ54 17 VSS 47 VSS 77 0DT1 107 DQ50 137 RFU 167 CB6 197 VDD 227 DQ55 18 RESET# 48 CB2 78 VDDQ 108 DQ51 138 RFU 168 CB7 198 VSS 228 VSS 19 NC 49 CB3 79 VSS 109 VSS 139 VSS 169 VSS 199 DQ36 229 DQ60 20 VSS 50 VSS 80 DQ32 110 DQ56 140 DQ14 170 VDDQ 200 DQ37 230 DQ61 21 DQ10 51 VDDQ 81 DQ33 111 DQ57 141 DQ15 171 CKE1 201 VSS 231 VSS 22 DQ11 52 CKE0 82 VSS 112 VSS 142 VSS 172 VDD 202 DM4/DQS13 232 DM7/DQS16 23 VSS 53 VDD 83 DQS4# 113 DQS7# 143 DQ20 173 NC 203 NC/DQS13# 233 NC/DQS16# 24 DQ16 54 NC/BA2 84 DQS4 114 DQS7 144 DQ21 174 NC 204 VSS 234 VSS 25 DQ17 55 ERR_OUT 85 VSS 115 VSS 145 VSS 175 VDDQ 205 DQ38 235 DQ62

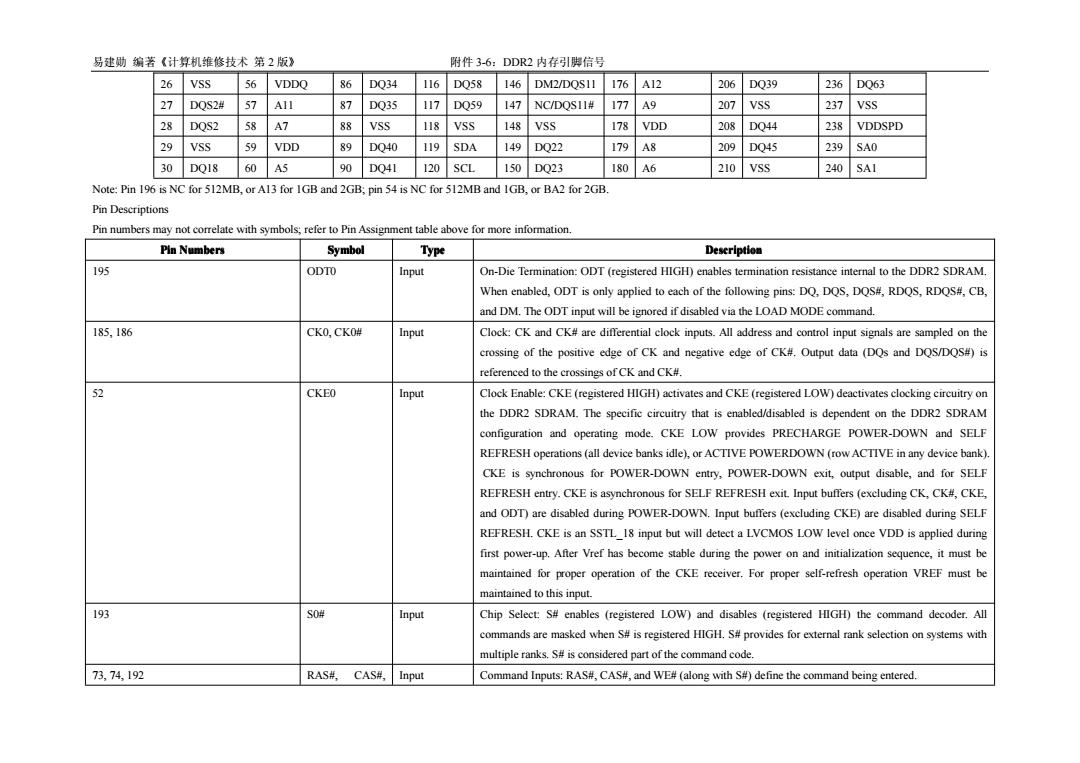

易建助编著《计算机维修技术第2版》 附件3-6:DDR2内存引脚信号 26 VSS 56 VDDQ 86 DQ34 116 DQ58 146 DM2/DQS11 176 A12 206D039 236 DQ63 27 DOS2# 57 A11 87 DO35 117 D059 147 NC/DOSI1# 177 A9 207 VSS 237 VSS 28 DOS2 58 A7 88 VSS 118 VSS 148 VSS 178 VDD 208 D044 238 VDDSPD 29 VSS 59 VDD 89 DQ40 119 SDA 149 DQ22 179 A8 209 DQ45 239 SA0 30 DO18 60 A5 90 DO41 120 SCL 150DQ23 180A6 210 VSS 240 SAl Note:Pin 196 is NC for 512MB,or Al3 for IGB and 2GB;pin 54 is NC for 512MB and IGB,or BA2 for 2GB. Pin Descriptions Pin numbers may not correlate with symbols;refer to Pin Assignment table above for more information. Pin Numbers Symbol Type Description 195 ODTO Input On-Die Termination:ODT(registered HIGH)enables termination resistance internal to the DDR2 SDRAM. When enabled,ODT is only applied to each of the following pins:DQ,DQS,DQS#,RDQS,RDQS#,CB, and DM.The ODT input will be ignored if disabled via the LOAD MODE command. 185,186 CKO,CKO# Input Clock:CK and CK#are differential clock inputs.All address and control input signals are sampled on the crossing of the positive edge of CK and negative edge of CK#.Output data (DQs and DQS/DQS#)is referenced to the crossings of CK and CK#. 52 CKEO Input Clock Enable:CKE(registered HIGH)activates and CKE(registered LOW)deactivates clocking circuitry on the DDR2 SDRAM.The specific circuitry that is enabled/disabled is dependent on the DDR2 SDRAM configuration and operating mode.CKE LOW provides PRECHARGE POWER-DOWN and SELF REFRESH operations(all device banks idle),or ACTIVE POWERDOWN (row ACTIVE in any device bank). CKE is synchronous for POWER-DOWN entry,POWER-DOWN exit,output disable,and for SELF REFRESH entry.CKE is asynchronous for SELF REFRESH exit Input buffers(excluding CK,CK#,CKE, and ODT)are disabled during POWER-DOWN.Input buffers (excluding CKE)are disabled during SELF REFRESH.CKE is an SSTL18 input but will detect a LVCMOS LOW level once VDD is applied during first power-up.After Vref has become stable during the power on and initialization sequence,it must be maintained for proper operation of the CKE receiver.For proper self-refresh operation VREF must be maintained to this input. 193 S04 Input Chip Select:S#enables (registered LOW)and disables (registered HIGH)the command decoder.All commands are masked when S#is registered HIGH.S#provides for external rank selection on systems with multiple ranks.S#is considered part of the command code. 73,74,192 RAS#CAS#. Input Command Inputs:RAS#,CAS#,and WE#(along with S#)define the command being entered

易建勋 编著《计算机维修技术 第 2 版》 附件 3-6:DDR2 内存引脚信号 Note: Pin 196 is NC for 512MB, or A13 for 1GB and 2GB; pin 54 is NC for 512MB and 1GB, or BA2 for 2GB. Pin Descriptions Pin numbers may not correlate with symbols; refer to Pin Assignment table above for more information. 26 VSS 56 VDDQ 86 DQ34 116 DQ58 146 DM2/DQS11 176 A12 206 DQ39 236 DQ63 27 DQS2# 57 A11 87 DQ35 117 DQ59 147 NC/DQS11# 177 A9 207 VSS 237 VSS 28 DQS2 58 A7 88 VSS 118 VSS 148 VSS 178 VDD 208 DQ44 238 VDDSPD 29 VSS 59 VDD 89 DQ40 119 SDA 149 DQ22 179 A8 209 DQ45 239 SA0 30 DQ18 60 A5 90 DQ41 120 SCL 150 DQ23 180 A6 210 VSS 240 SA1 Pin Pin Numbers Numbers Numbers Numbers Symbol Symbol Type Type Description Description Description Description 195 ODT0 Input On-Die Termination: ODT (registered HIGH) enables termination resistance internal to the DDR2 SDRAM. When enabled, ODT is only applied to each of the following pins: DQ, DQS, DQS#, RDQS, RDQS#, CB, and DM. The ODT input will be ignored if disabled via the LOAD MODE command. 185, 186 CK0, CK0# Input Clock: CK and CK# are differential clock inputs. All address and control input signals are sampled on the crossing of the positive edge of CK and negative edge of CK#. Output data (DQs and DQS/DQS#) is referenced to the crossings of CK and CK#. 52 CKE0 Input Clock Enable: CKE (registered HIGH) activates and CKE (registered LOW) deactivates clocking circuitry on the DDR2 SDRAM. The specific circuitry that is enabled/disabled is dependent on the DDR2 SDRAM configuration and operating mode. CKE LOW provides PRECHARGE POWER-DOWN and SELF REFRESH operations (all device banks idle), or ACTIVE POWERDOWN (row ACTIVE in any device bank). CKE is synchronous for POWER-DOWN entry, POWER-DOWN exit, output disable, and for SELF REFRESH entry. CKE is asynchronous for SELF REFRESH exit. Input buffers (excluding CK, CK#, CKE, and ODT) are disabled during POWER-DOWN. Input buffers (excluding CKE) are disabled during SELF REFRESH. CKE is an SSTL_18 input but will detect a LVCMOS LOW level once VDD is applied during first power-up. After Vref has become stable during the power on and initialization sequence, it must be maintained for proper operation of the CKE receiver. For proper self-refresh operation VREF must be maintained to this input. 193 S0# Input Chip Select: S# enables (registered LOW) and disables (registered HIGH) the command decoder. All commands are masked when S# is registered HIGH. S# provides for external rank selection on systems with multiple ranks. S# is considered part of the command code. 73, 74, 192 RAS#, CAS#, Input Command Inputs: RAS#, CAS#, and WE# (along with S#) define the command being entered

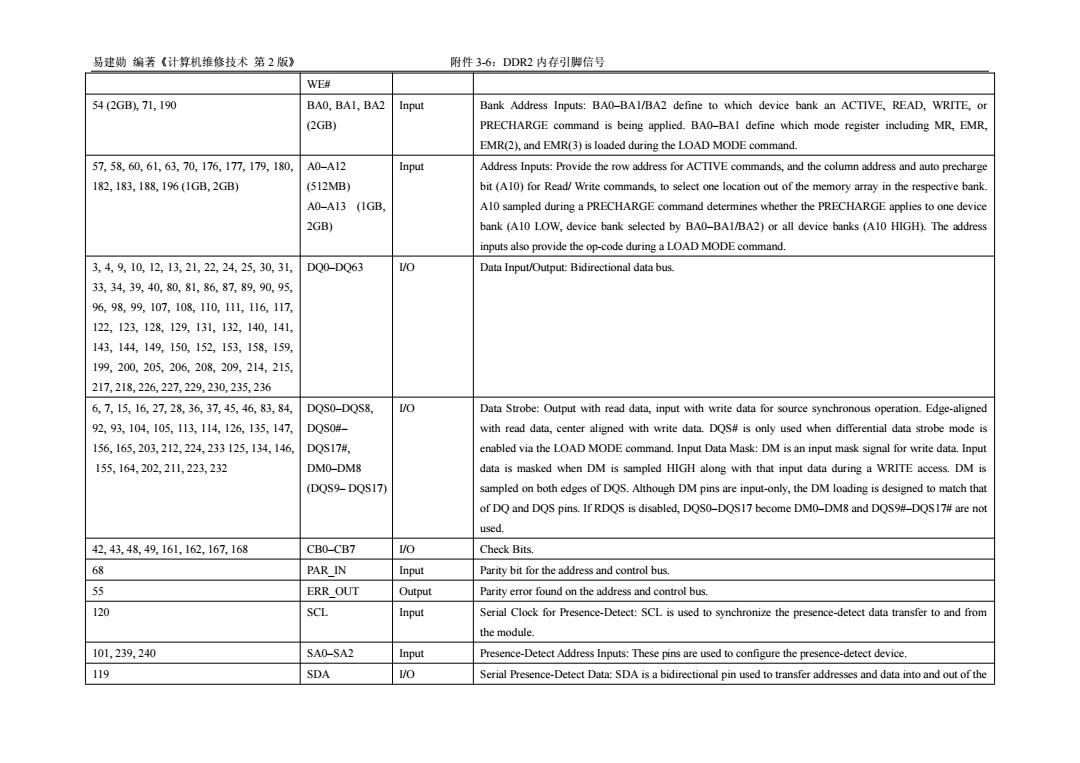

易建助编著《计算机维修技术第2版》 附件3-6:DDR2内存引脚信号 WE# 54(2GB,7L,190 BA0.BAI.BA2 Input Bank Address Inputs:BA0-BAI/BA2 define to which device bank an ACTIVE,READ,WRITE,or (2GB) PRECHARGE command is being applied.BAO-BAI define which mode register including MR,EMR, EMR(2),and EMR(3)is loaded during the LOAD MODE command. 57,58,60,61,63,70,176,177,179,180, A0-A12 Input Address Inputs:Provide the row address for ACTIVE commands,and the column address and auto precharge 182,183,188,196(1GB,2GB) (512MB) bit (A10)for Read/Write commands,to select one location out of the memory array in the respective bank. A0-A13 (IGB, Al0 sampled during a PRECHARGE command determines whether the PRECHARGE applies to one device 2GB) bank (A10 LOW,device bank selected by BA0-BAI/BA2)or all device banks (A10 HIGH).The address inputs also provide the op-code during a LOAD MODE command. 3,49,10,12,13,21,22,24,25,30,31, DQ0-DQ63 I/O Data Input/Output:Bidirectional data bus. 33,34,39,40,80,81,86,87,89,90,95 96,98,99,107,108.110,111,116117, 122,123,128,129,131,132,140,141, 143,144,149,150,152,153,158,159, 199,200,205,206,208,209,214,215, 217,218,226,227,229,230,235,236 6,7,15,1627,28,36,37,45,46,83,84, DQSO-DOS8. I/O Data Strobe:Output with read data,input with write data for source synchronous operation.Edge-aligned 92,93,104,105,113,114,126,135,147, DQS0牌- with read data,center aligned with write data.DQS#is only used when differential data strobe mode is 156,165,203,212,224,233125,134,146, DQS17#, enabled via the LOAD MODE command.Input Data Mask:DM is an input mask signal for write data.Input 155,164,202,211,223.232 DMO-DM8 data is masked when DM is sampled HIIGH along with that input data during a WRITE access.DM is (DQS9-DQSI7) sampled on both edges of DQS.Although DM pins are input-only,the DM loading is designed to match that of DQ and DOS pins.If RDOS is disabled,DOSO-DOS17 become DMO-DM8 and DOS9#-DOS17#are not used. 42,43.48,49,161,162,167,168 CBO-CB7 I/O Check Bits. 68 PAR IN Input Parity bit for the address and control bus. 55 ERR OUT Output Parity error found on the address and control bus. 120 SCL Input Serial Clock for Presence-Detect:SCL is used to synchronize the presence-detect data transfer to and from the module. 101,239,240 SA0-SA2 Input Presence-Detect Address Inputs:These pins are used to configure the presence-detect device. 119 SDA I/O Serial Presence-Detect Data:SDA is a bidirectional pin used to transfer addresses and data into and out of the

易建勋 编著《计算机维修技术 第 2 版》 附件 3-6:DDR2 内存引脚信号 WE# 54 (2GB), 71, 190 BA0, BA1, BA2 (2GB) Input Bank Address Inputs: BA0–BA1/BA2 define to which device bank an ACTIVE, READ, WRITE, or PRECHARGE command is being applied. BA0–BA1 define which mode register including MR, EMR, EMR(2), and EMR(3) is loaded during the LOAD MODE command. 57, 58, 60, 61, 63, 70, 176, 177, 179, 180, 182, 183, 188, 196 (1GB, 2GB) A0–A12 (512MB) A0–A13 (1GB, 2GB) Input Address Inputs: Provide the row address for ACTIVE commands, and the column address and auto precharge bit (A10) for Read/ Write commands, to select one location out of the memory array in the respective bank. A10 sampled during a PRECHARGE command determines whether the PRECHARGE applies to one device bank (A10 LOW, device bank selected by BA0–BA1/BA2) or all device banks (A10 HIGH). The address inputs also provide the op-code during a LOAD MODE command. 3, 4, 9, 10, 12, 13, 21, 22, 24, 25, 30, 31, 33, 34, 39, 40, 80, 81, 86, 87, 89, 90, 95, 96, 98, 99, 107, 108, 110, 111, 116, 117, 122, 123, 128, 129, 131, 132, 140, 141, 143, 144, 149, 150, 152, 153, 158, 159, 199, 200, 205, 206, 208, 209, 214, 215, 217, 218, 226, 227, 229, 230, 235, 236 DQ0–DQ63 I/O Data Input/Output: Bidirectional data bus. 6, 7, 15, 16, 27, 28, 36, 37, 45, 46, 83, 84, 92, 93, 104, 105, 113, 114, 126, 135, 147, 156, 165, 203, 212, 224, 233 125, 134, 146, 155, 164, 202, 211, 223, 232 DQS0–DQS8, DQS0#– DQS17#, DM0–DM8 (DQS9– DQS17) I/O Data Strobe: Output with read data, input with write data for source synchronous operation. Edge-aligned with read data, center aligned with write data. DQS# is only used when differential data strobe mode is enabled via the LOAD MODE command. Input Data Mask: DM is an input mask signal for write data. Input data is masked when DM is sampled HIGH along with that input data during a WRITE access. DM is sampled on both edges of DQS. Although DM pins are input-only, the DM loading is designed to match that of DQ and DQS pins. If RDQS is disabled, DQS0–DQS17 become DM0–DM8 and DQS9#–DQS17# are not used. 42, 43, 48, 49, 161, 162, 167, 168 CB0–CB7 I/O Check Bits. 68 PAR_IN Input Parity bit for the address and control bus. 55 ERR_OUT Output Parity error found on the address and control bus. 120 SCL Input Serial Clock for Presence-Detect: SCL is used to synchronize the presence-detect data transfer to and from the module. 101, 239, 240 SA0–SA2 Input Presence-Detect Address Inputs: These pins are used to configure the presence-detect device. 119 SDA I/O Serial Presence-Detect Data: SDA is a bidirectional pin used to transfer addresses and data into and out of the

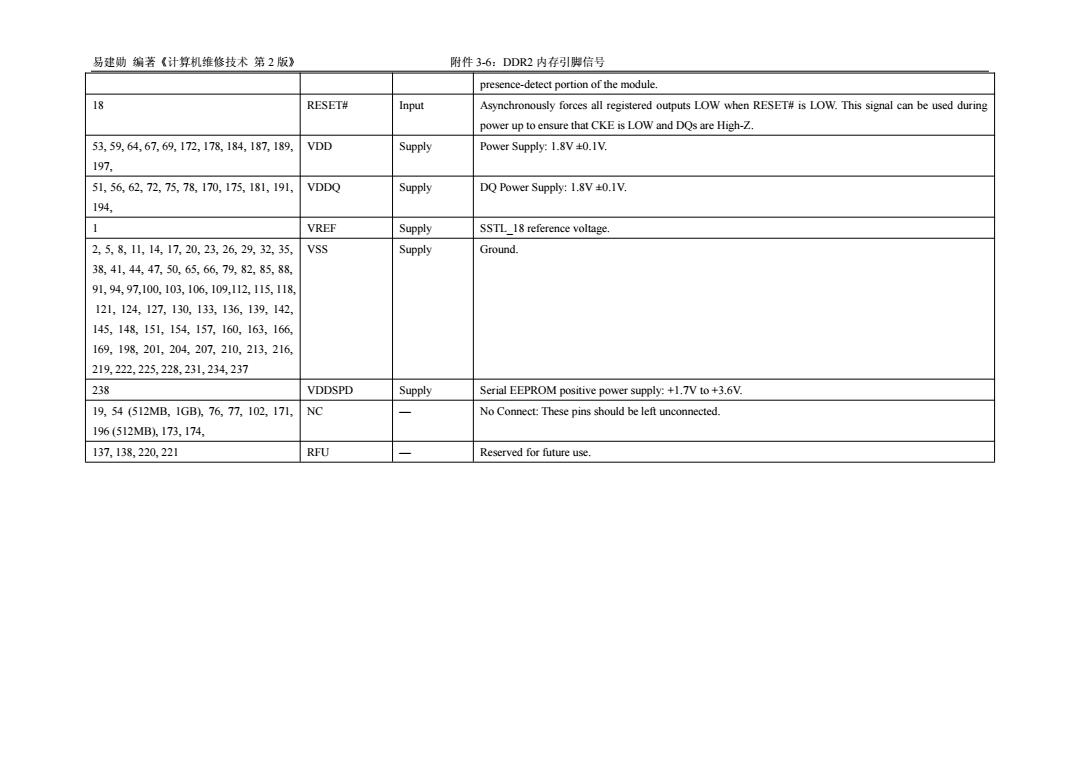

易建助编著《计算机维修技术第2版》 附件3-6:DDR2内存引脚信号 presence-detect portion of the module. 分 RESET# Input Asynchronously forces all registered outputs LOW when RESET#is LOW.This signal can be used during power up to ensure that CKE is LOW and DQs are High-Z. 53,59,64,67,69,172,178,184,187,189, VDD Supply Power Supply:1.8V +0.IV. 197, 51,56,62,72,75,78,170,175181,191, VDDQ Supply DQ Power Supply:1.8V 40.1V. 194, 1 VREF Supply SSTL 18 reference voltage. 2,58,11,14,17,20,23,2629,32,35, VSS Supply Ground. 38,41,44,47,50,65,66,79,82,85,88, 91,94,97,100,103,106,109,112,115,118, 121,124,127,130,133,136,139,142, 145,148,151,154,157,160,163,166 169,198,201,204,207,210,213,216, 219,222,225,228,231,234,237 238 VDDSPD Supply Serial EEPROM positive power supply:+1.7V to+3.6V. 19,54(512MB,1GB,76,77,102,171, NC No Connect:These pins should be left unconnected. 196(512MB),173,174, 137,138,220,221 RFU Reserved for future use

易建勋 编著《计算机维修技术 第 2 版》 附件 3-6:DDR2 内存引脚信号 presence-detect portion of the module. 18 RESET# Input Asynchronously forces all registered outputs LOW when RESET# is LOW. This signal can be used during power up to ensure that CKE is LOW and DQs are High-Z. 53, 59, 64, 67, 69, 172, 178, 184, 187, 189, 197, VDD Supply Power Supply: 1.8V ±0.1V. 51, 56, 62, 72, 75, 78, 170, 175, 181, 191, 194, VDDQ Supply DQ Power Supply: 1.8V ±0.1V. 1 VREF Supply SSTL_18 reference voltage. 2, 5, 8, 11, 14, 17, 20, 23, 26, 29, 32, 35, 38, 41, 44, 47, 50, 65, 66, 79, 82, 85, 88, 91, 94, 97,100, 103, 106, 109,112, 115, 118, 121, 124, 127, 130, 133, 136, 139, 142, 145, 148, 151, 154, 157, 160, 163, 166, 169, 198, 201, 204, 207, 210, 213, 216, 219, 222, 225, 228, 231, 234, 237 VSS Supply Ground. 238 VDDSPD Supply Serial EEPROM positive power supply: +1.7V to +3.6V. 19, 54 (512MB, 1GB), 76, 77, 102, 171, 196 (512MB), 173, 174, NC — No Connect: These pins should be left unconnected. 137, 138, 220, 221 RFU — Reserved for future use