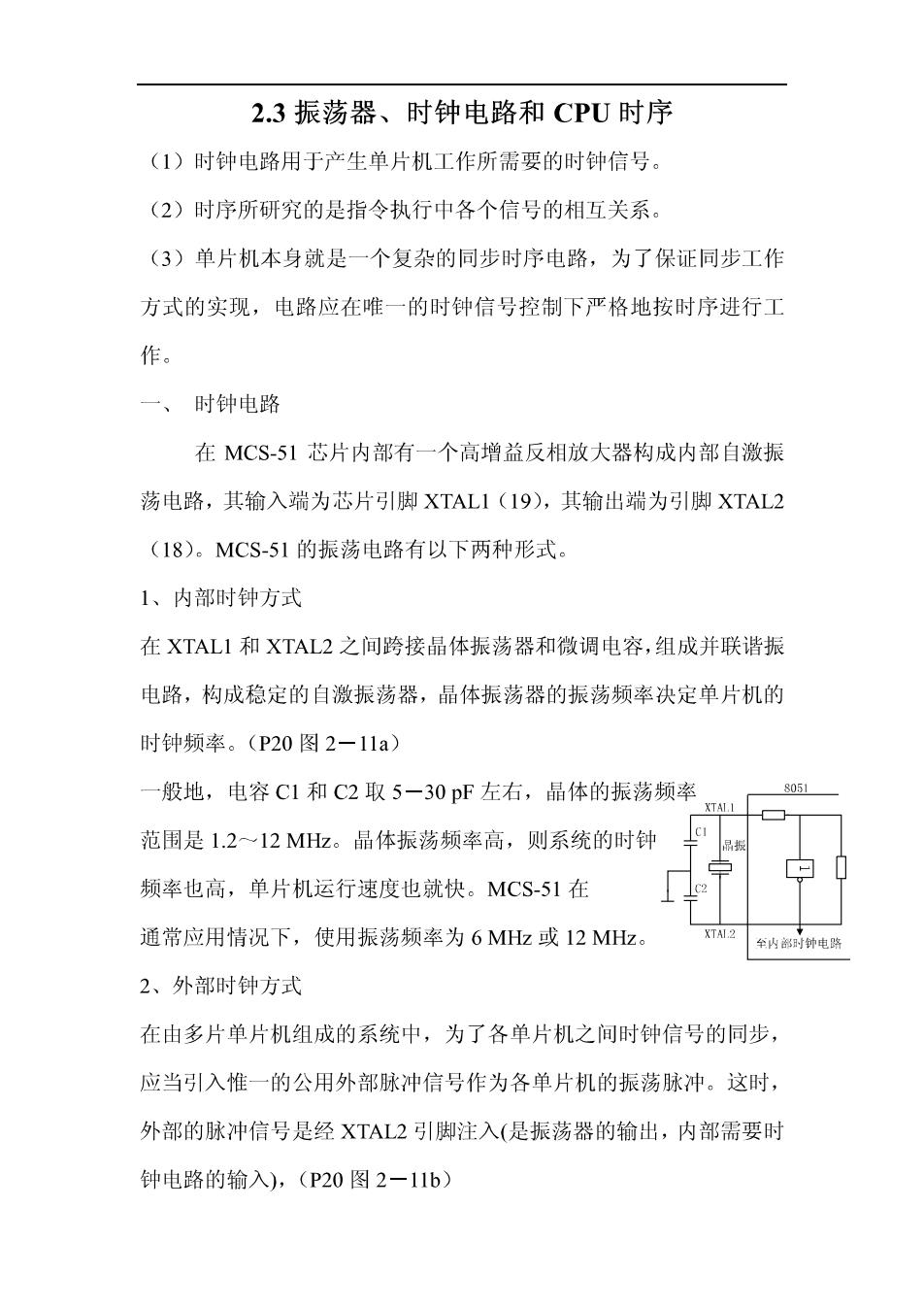

2.3振荡器、时钟电路和CPU时序 (1)时钟电路用于产生单片机工作所需要的时钟信号。 (2)时序所研究的是指令执行中各个信号的相互关系。 (3)单片机本身就是一个复杂的同步时序电路,为了保证同步工作 方式的实现,电路应在唯一的时钟信号控制下严格地按时序进行工 作。 一、时钟电路 在MCS-51芯片内部有一个高增益反相放大器构成内部自激振 荡电路,其输入端为芯片引脚XTAL1(19),其输出端为引脚XTAL2 (18)。MCS-51的振荡电路有以下两种形式。 1、内部时钟方式 在XTAL1和XTAL2之间跨接晶体振荡器和微调电容,组成并联谐振 电路,构成稳定的自激振荡器,晶体振荡器的振荡频率决定单片机的 时钟频率。(P20图2-11a) 一般地,电容C1和C2取5一30pF左右,晶体的振荡频率 805 范围是1.2一12MHz。品体振荡频率高,则系统的时钟 频率也高,单片机运行速度也就快。MCS-51在 通常应用情况下,使用振荡频率为6MHz或12MHz XTAL.2 伞内时钟电略 2、外部时钟方式 在由多片单片机组成的系统中,为了各单片机之间时钟信号的同步, 应当引入惟一的公用外部脉冲信号作为各单片机的振荡脉冲。这时, 外部的脉冲信号是经XTAL2引脚注入(是振荡器的输出,内部需要时 钟电路的输入),(P20图2一11b)

二、MCS-51单片机的时序 1、时钟的概念 单片机一启动,就在执行如下的循环 取指令一分析指令→执行指令 为了对指令的执行有一个正确的理解,需要理解单片机的时序。 时序是用定时来说明的。MCS-51的时序定时单位共有4个,从小到 大依次是:时钟周期、状态周期、机器周期和指令周期 时钟周期、状态周期 时钟周期:振荡电路的振荡周期,其值由外接晶体或外输入时钟 来决定,其值为石英振荡器频率(时钟频率)的倒数。例如:在单片 机外接1MH的晶体,则单片机的系统时钟的频率为1M,时钟周期为 1us经常将时钟周期称为节拍(用P表示)。时钟周期经过二分频后, 就是单片机的时钟信号的周期,其定义为状态周期(用S表示)。 所以,一个状态就包含两个节拍(时钟周期),具前半周期对应 的拍节叫节拍1(P1),后半周期对应的节拍叫节拍2(P2)。 机器周期 MCS-51单片机的一个机器周期为6个状态周期,并依次表示为 S1~S6。由于一个状态又包括两个节拍(振荡脉冲周期),因此, 个机器周期总共有12个时钟周期,分别记作S1P1、S1P2、.、S6P2。 (P19图2-10)

由于一个机器周期共有12个振荡脉冲周期,因此机器脉冲就是振荡 脉冲的十二分频。例:当振荡脉冲频率为12MHz时,一个机器周期 为1μs:当振荡脉冲频率为6MHz时,一个机器周期为2μs。 指令周期 执行一条指令所需要的时间称为指令周期。它一般由若干个机器 周期组成。不同的指令,所需要的机器周期不同。通常,包含一个机 器周期的指令称为单周期指令,包含两个机器周期的指令称为双周期 指令,等等。 在MCS-51系统中,指令周期有以下三种: 1,单周期指令;2,双周期指令;3,四周期指令 我们知道:一个机器周期包含了12个震荡周期如果我们使用 个12M的晶体振荡器,那么:一个机器周期为1us, 两个机器周期为2us, 四个机器周期为4us. 可见一条指令的运算速度与它所包含的机器周期数有关机器周 期数越少,执行的速度就越快.在MCS-51单片机的指令系统中,除了 乘、除法指令为四个机器周期外,其余都是单周期和双周期指令. 2、指令的字节数与指令周期之间的关系 只有在ALE(地址锁存允许)信号有效时,才可以访问存储器。 在MCS-51单片机的指令系统中有: 单字节: 双字节; 三字节指令

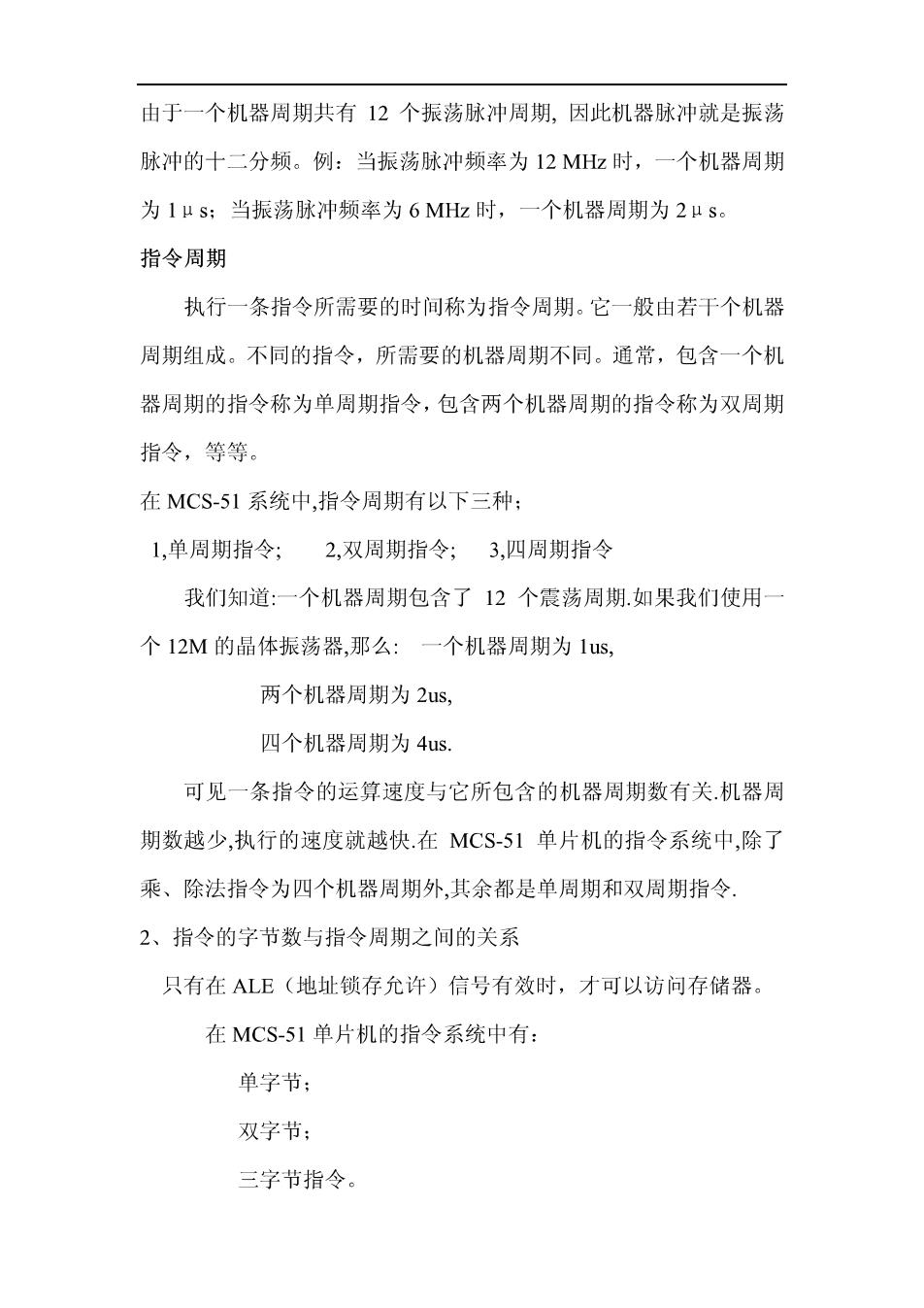

在MCS-51的111条指令中,可以分为六种基本的时序: 1,单字节单周期指令: 4,双字节单周期指令: 2,单字节双周期指令; 5,双字节双周期指令; 3,单字节四周期指令: 6,三字节双周期指令. 2.4I/0的结构 MCS-51共有4个8位的双向并行IVO口:P0、P1、P2、P3。每个 口都包含一个8位锁存器、一个输出驱动器和输入缓冲器,作输出时, 数据可以锁存,作输入时,数据可以缓冲。锁存器被归入专用寄存器 之列,并且具有字节寻址和位寻址功能 P0.0~P0.7(39一32脚):8位漏极开路的三态双向输入/输出口。 P1.0一P1.7(1一8脚):8位带有内部上拉电阻的准双向输入/输出口。 P2.0~P2.7(21一28脚):8位带有内部上拉电阻的准双向输入/输出 ▣。 P3.0~P3.7(10一17脚):8位带有内部上拉电阻的准双向输入/输出 口。 在访问片外扩展存储器时,低8位地址和数据由P0口分时传送,高 8位地址由P2口传送。在无片外扩展存储器的系统中,这4个口的 每一位均可作为双向的1/O端口使用。 P0口:P0口的结构(P21:图2一12)

地址/数据 控制 读锁存器 2 内部总线 D 锁存器 写锁存岩 CP H汇 读引脚一 硬件组成: (1)一个输出锁存器(D型触发器): (2)二个三态门(控制读引脚或读锁存器): (3)与门和MUX等元件组成的输出控制电路: (4)一对场效应晶体管FET构成的输出电路 2、P0口作为一般I/0口使用 (1)一般/O口的设置:在系统无外部存储器时,控制电路中的“控 制”=0,多路开关MUX接入锁存器的端,P0口作为通用O端口 使用。由于与门的一个输入端为“0,所以它使上端的FET截止这就是 P0口在做I/O口时输出为“漏极开路”的结构原因. (2)输出操作:作为输出口时,内部数据送到锁存器的“D”端,锁存器 写脉冲加到CP端。内部数据经“”端送场效管应输出极如送“1时 O=0,使下端的FET截止.这样出现输出极的两个FET全部截止在这 种情况下必须在端口线上外加上拉电阻.(准双向)这样在上拉电阻 的作用下,使端口为高电平.同理,若总线向口送0时,锁存器的=1,使 下端的FET导通(上面的FET仍然截止),这样端口呈现“O电平.P0口 的输出可以驱动8个TTL负载。 (3)输入操作:

读引脚:在P0作为输入端口执行输入指令时,“读引脚”打开三态门 G1,则P0口的数据经三态门G1到达内部数据总线上。 读锁存器:读锁存器控制打开三态门G2,将Q端的数据送到内部总 线上。这种方式适用于:“读一修改一写操作。在这种情况下,读入 的数据不是来自引脚,而是端口内部的锁存器的内容。 注意:由于T1并接在输出端P0上,若T1导通,则会使P0端口上 的高电平变成低电平,送到内部数据总线的数据就有错误,即产生对 P0口的误读。为了防止误读,在进行读操作前应线向锁存器写入1, 即使=0。此时,T1,T2全截止,引脚处于悬浮状态,可作高阻抗 输入。一一一先输出“1”,使T2截止,然后再读,所以P0口作为I/O 口使用时是准双向口,并不是完全双向。 3、P0口作为地址/数据总线使用 系统使用外存储器时,P0口只能作为地址/数据总线使用,不能作为 一般的I/O口。 (1)地址/数据总线方式的设计:一一控制电路的“控制=1”,MUX 接向“地址/数据”信号。 (2)写操作:在P0口上输出外部存储器低8位地址或输出内部数 据(8位)。由于上下两个T1、T2构成推拉式输出电路(T2通P0口 电位上拉,T1通P0口电位下拉)。 地址/数据=1,与门输出=1,与非门输出b处电平=0,T2通, T1止,P0=1 地址/数据=0,与门输出=0,与非门输出b处电平=1,T1通,T2 止,P0=0

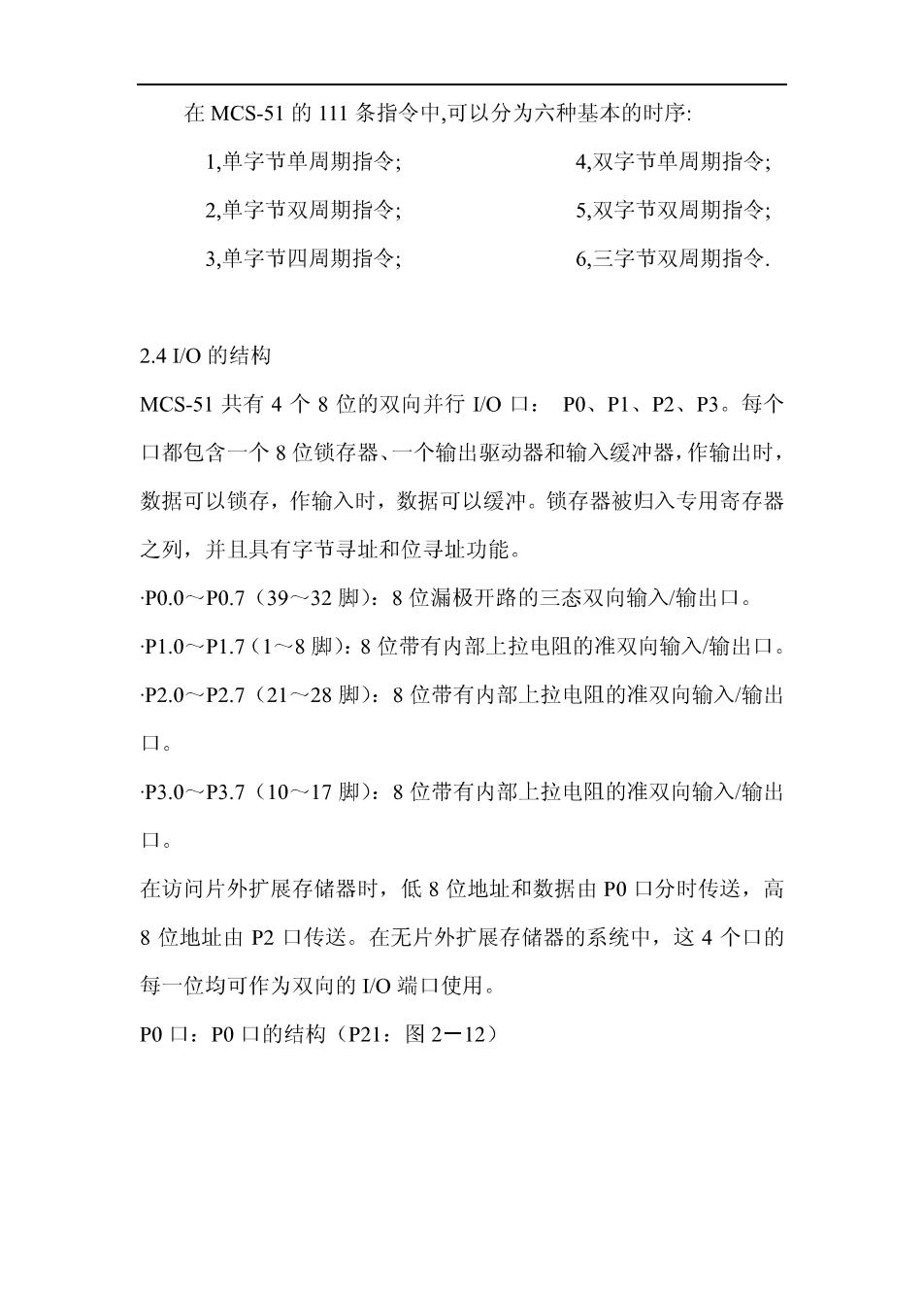

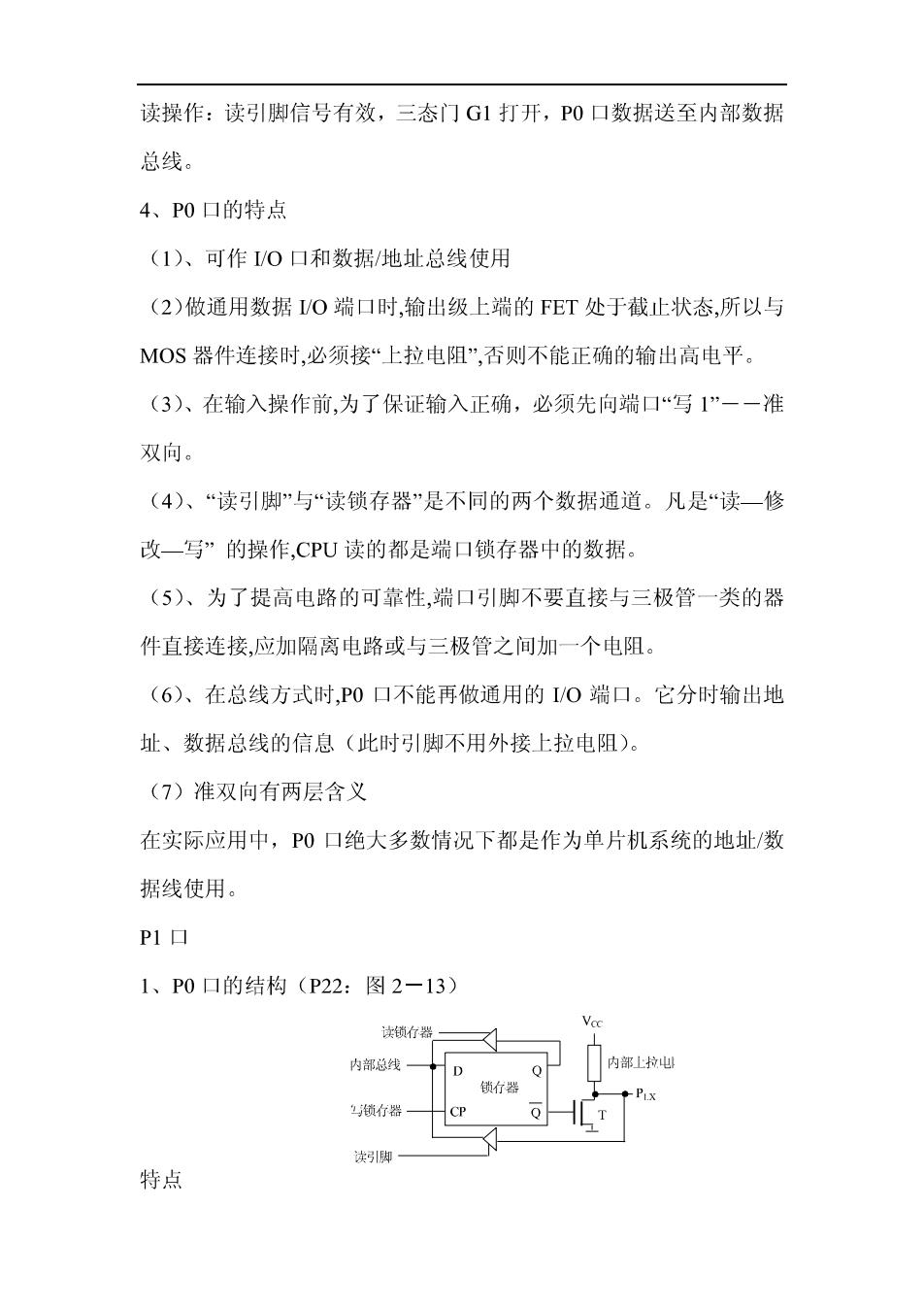

读操作:读引脚信号有效,三态门G1打开,P0口数据送至内部数据 总线。 4、P0口的特点 (1)、可作I/O口和数据/地址总线使用 (2)做通用数据VO端口时,输出级上端的FET处于截止状态,所以与 MOS器件连接时,必须接“上拉电阻”,否则不能正确的输出高电平。 (3)、在输入操作前,为了保证输入正确,必须先向端口“写1”一一准 双向。 (4)、“读引脚”与“读锁存器”是不同的两个数据通道。凡是“读一修 改一写”的操作,CPU读的都是端口锁存器中的数据。 (5)、为了提高电路的可靠性,端口引脚不要直接与三极管一类的器 件直接连接,应加隔离电路或与三极管之间加一个电阻。 (6)、在总线方式时,P0口不能再做通用的I/O端口。它分时输出地 址、数据总线的信息(此时引脚不用外接上拉电阻)。 (7)准双向有两层含义 在实际应用中,P0口绝大多数情况下都是作为单片机系统的地址/数 据线使用。 P1口 1、P0口的结构(P22:图2一13) 读锁行器 内部总线 内部上拉 横行器 CP 读好引牌 特点

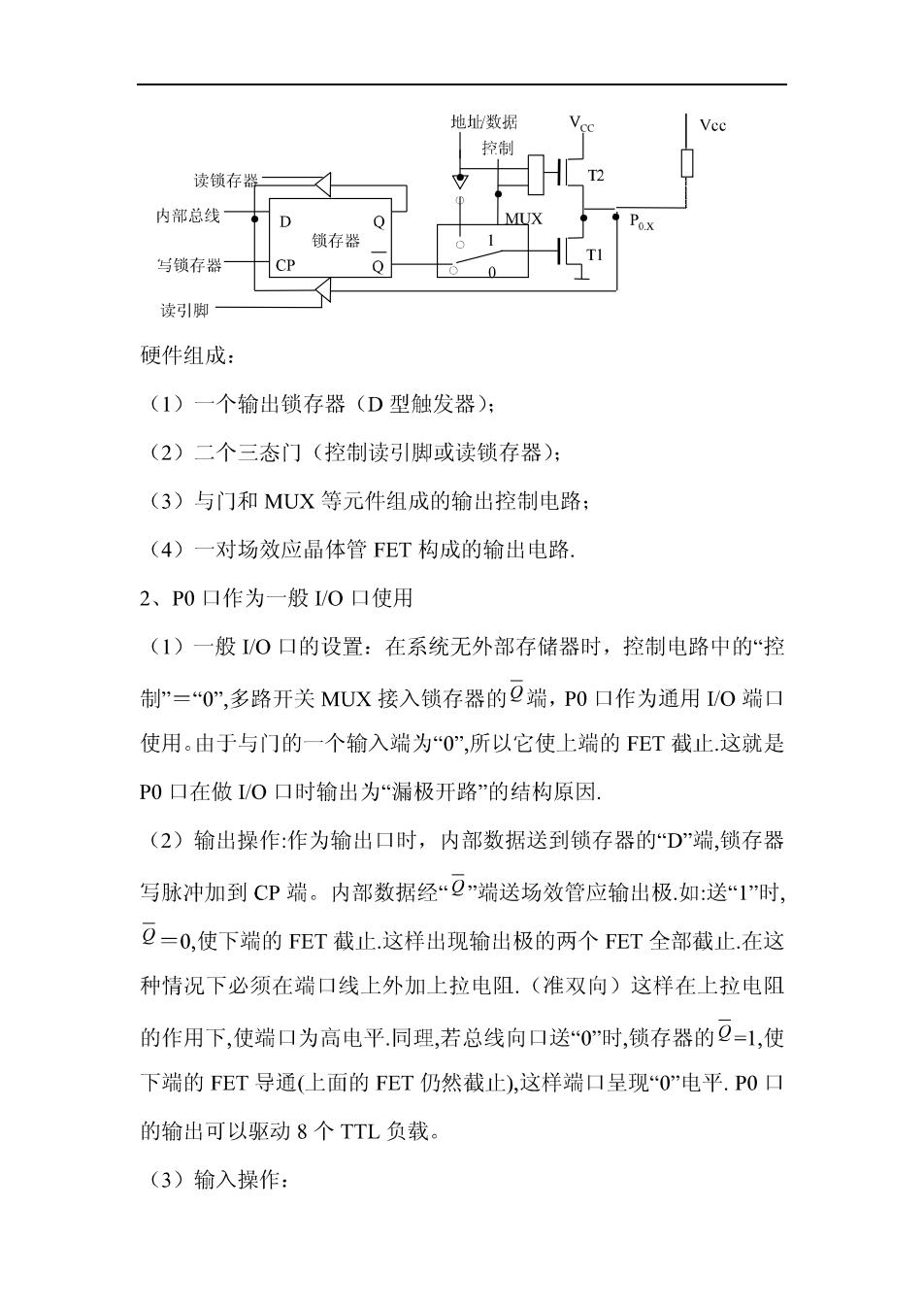

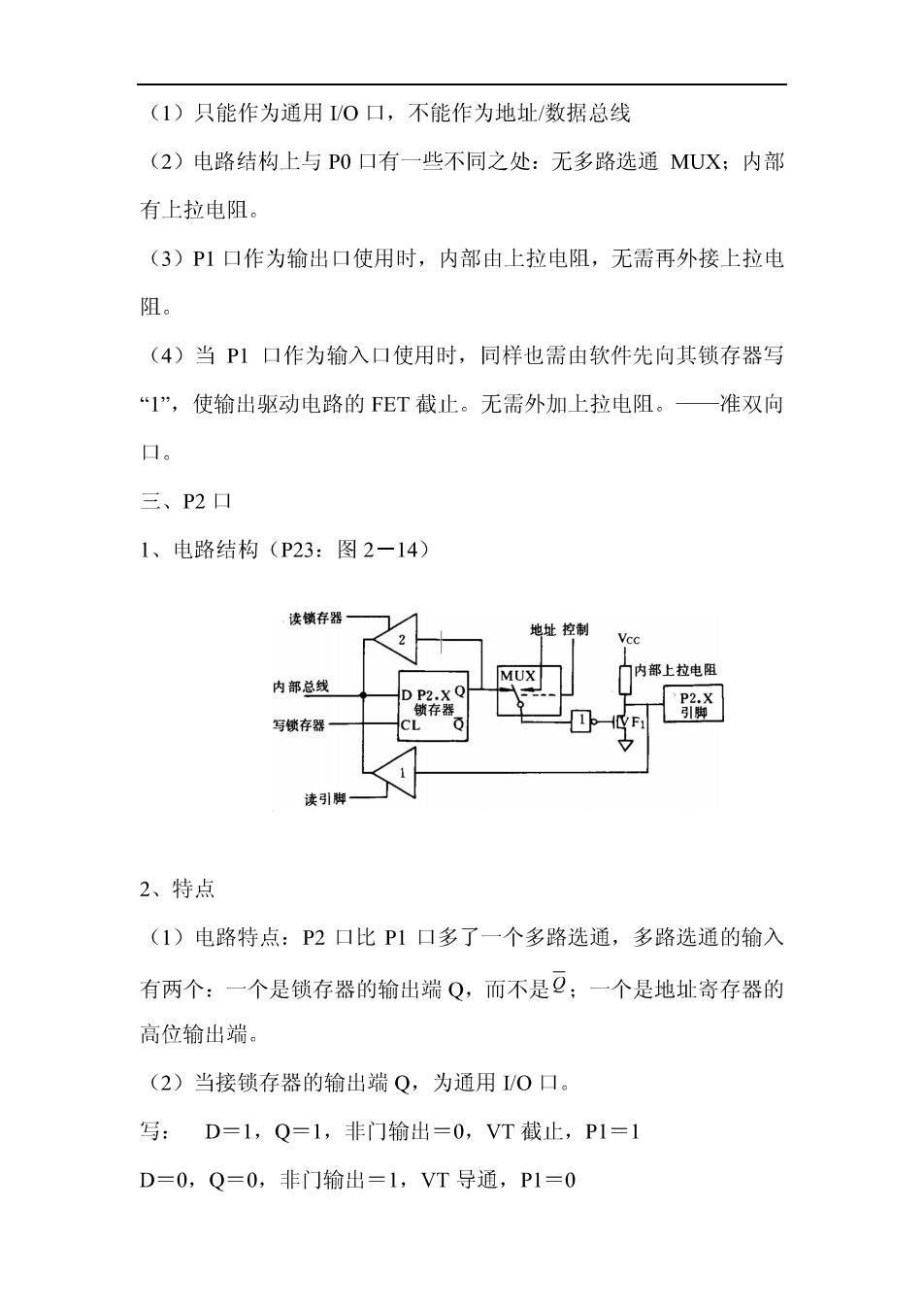

(1)只能作为通用/O口,不能作为地址/数据总线 (2)电路结构上与P0口有一些不同之处:无多路选通MUX;内部 有上拉电阻。 (3)P1口作为输出口使用时,内部由上拉电阻,无需再外接上拉电 阻。 (4)当P1口作为输入口使用时,同样也需由软件先向其锁存器写 “1”,使输出驱动电路的FET截止。无需外加上拉电阻。—准双向 口。 三、P2口 1、电路结构(P23:图2-14 读存器 地址控制 部上拉电阻 MU 内部总线 写存器 法引脚 2、特点 (1)电路特点:P2口比P1口多了一个多路选通,多路选通的输入 有两个:一个是锁存器的输出端Q,而不是:一个是地址寄存器的 高位输出端。 (2)当接锁存器的输出端Q,为通用I/0口。 写:D=1,Q=1,非门输出=0,VT截止,P1=1 D=0,Q=0,非门输出=1,VT导通,P1=0

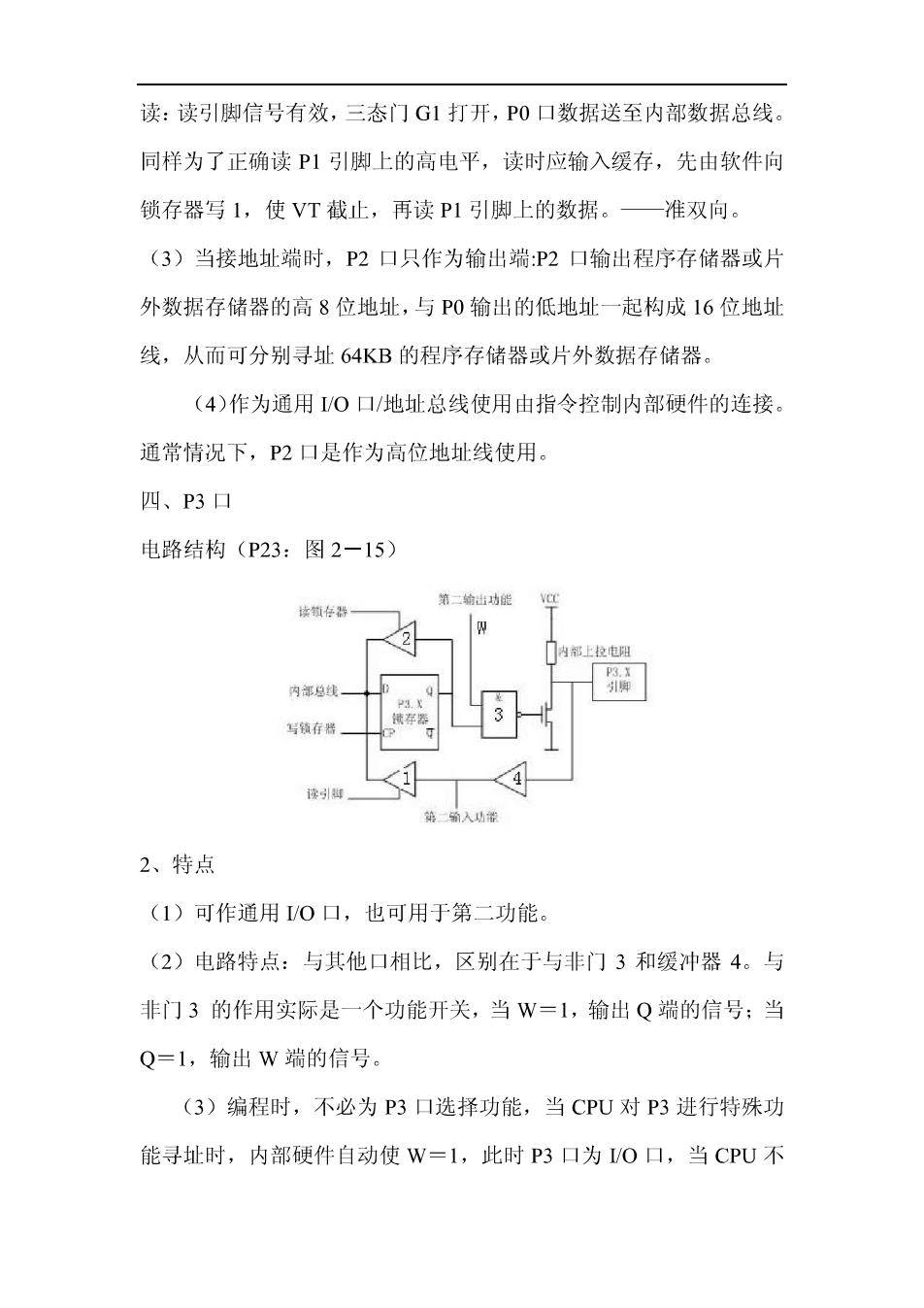

读:读引脚信号有效,三态门G1打开,P0口数据送至内部数据总线。 同样为了正确读P1引脚上的高电平,读时应输入缓存,先由软件向 锁存器写1,使VT截止,再读P1引脚上的数据。—准双向。 (3)当接地址端时,P2口只作为输出端:P2口输出程序存储器或片 外数据存储器的高8位地址,与P0输出的低地址一起构成16位地址 线,从而可分别寻址64KB的程序存储器或片外数据存储器。 (4)作为通用VO口/地址总线使用由指令控制内部硬件的连接。 通常情况下,P2口是作为高位地址线使用。 四、P3口 电路结构(P23:图2一15) 读葡存程 内部总 2、特点 (1)可作通用VO口,也可用于第二功能。 (2)电路特点:与其他口相比,区别在于与非门3和缓冲器4。与 非门3的作用实际是一个功能开关,当W=1,输出Q端的信号:当 Q=1,输出W端的信号。 (3)编程时,不必为P3口选择功能,当CPU对P3进行特殊功 能寻址时,内部硬件自动使W=1,此时P3口为IVO口,当CPU不

对P3进行特殊功能寻址时,内部硬件自动使Q=1,此时P3口为为 第二功能 (4)作通用I/O口使用时,原理与P2口一样,是一个准双向口。 写:DT1,Q=1,与非门输出=0,VT截止,P1=1 D=0,Q二0,与非门输出=1,VT导通,P1=0 读:读引脚信号有效,三态门G1打开,P0口数据送至内部数据总线。 同样为了正确读P1引脚上的高电平,读时应输入缓存,先由软件向 锁存器写1,使VT截止,再读P1引脚上的数据。一准双向。 (5)第二功能见前面所讲的P3口的第二功能。 P3口一般作第二功能使用 五、端口的使用 1、用途 (1)、P0口一般作为地址/数据线使用,输出片外存储器低8位地址 或内部的8位数据,输入8位数据到内部总线。时分复用,8个TTL 负载 (2)、P1口一般用于通用/O口使用,输入输出8位数据。4个 TTL负载 (3)、P2口一般用于输出片外存储器高8位地址,4个TTL负载 (4)、P3口一般用于第二功能。4个TTL负载 2、并行端口在使用时应注意的几个问题 (1)“拉电流”还是“灌电流”-与大电流负载的连接 使用灌电流的方式与电流较大的负载直接连接时,端口可以吸 收约20mA的电流而保证端口电平不高于0.45V(见下左图)