第8章 81选择题 1、6264芯片是(B) (A)EEPROM (B)RAM (C)FLASH ROM (D)EPROM 2、用MCS-51用串行扩展并行O口时,串行接口工作方式选择(A) (A)方式0(B)方式1(C)方式2(D)方式3 3、使用8255可以扩展出的IV0口线是(B) (A)16根(B)24根(C)22根(D)32根 4、当8031外出扩程序存储器8KB时,需使用EPROM2716(C) (A)2片(B)3片(C)4片(D)5片 5、某种存储器芯片是8KB*4/片,那么它的地址线根线是(C) (A)11根(B)12根(C)13根(D)14根 6、MCS-51外扩ROM,RAM和I/O口时,它的数据总线是(A) (A)P0(B)P1(C)P2(D)P3 7、当使用快速外部设备时,最好使用的输入输出方式是(C) (A)中断(B)条件传送(C)DMA(D)无条件传送 8、MCS51的中断源全部编程为同级时,优先级最高的是(D) (A)INT1(B)T(C)串行接口(D)INTO 9、MCS-51的并行VO口信息有两种读取方法:一种是读引脚,还有一种是(A) (A)读锁存器具(B)读数据库(C)读A累加器具(D)读CPU 10、MCS-51的并行I/O口读-改.写操作,是针对该口的(D) (A)引脚(B)片选信号(C)地址线(D)内部锁存器 8-2判断题1、MCS-51外扩I/O口与外RAM是统一编址的。(对) 2、使用8751且EA=1时,仍可外扩64KB的程序存储器。(错)60KB 3、8155的复位引脚可与89C51的复位引脚直接相连。(对) 4、片内RAM与外部设备统一编址时,需要专门的输入输出指令。(错)统一编址的 特点正是无需专门的输入输出指令

第 8 章 8-1 选择题 1、6264 芯片是(B) (A) EEPROM (B)RAM(C)FLASH ROM (D)EPROM 2、用 MCS-51 用串行扩展并行 I/O 口时,串行接口工作方式选择(A) (A) 方式 0 (B)方式 1 (C)方式 2 (D)方式 3 3、使用 8255 可以扩展出的 I/O 口线是(B) (A) 16 根 (B)24 根 (C)22 根 (D)32 根 4、当 8031 外出扩程序存储器 8KB 时,需使用 EPROM 2716(C) (A) 2 片 (B)3 片 (C)4 片 (D)5 片 5、某种存储器芯片是 8KB*4/片,那么它的地址线根线是(C) (A) 11 根 (B)12 根 (C)13 根 (D)14 根 6、MCS-51 外扩 ROM,RAM 和 I/O 口时,它的数据总线是(A) (A) P0 (B)P1 (C)P2 (D)P3 7、当使用快速外部设备时,最好使用的输入/输出方式是(C) (A)中断 (B)条件传送 (C)DMA (D)无条件传送 8、MCS-51 的中断源全部编程为同级时,优先级最高的是(D) (A) INT1 (B)TI (C)串行接口 (D)INT0 9、MCS-51 的并行 I/O 口信息有两种读取方法:一种是读引脚,还有一种是(A) (A)读锁存器具 (B)读数据库 (C)读 A 累加器具 (D)读 CPU 10、MCS-51 的并行 I/O 口读-改-写操作,是针对该口的(D) (A)引脚 (B)片选信号 (C)地址线 (D)内部锁存器 8-2 判断题 1、MCS-51 外扩 I/O 口与外 RAM 是统一编址的。(对) 2、使用 8751 且 EA=1 时,仍可外扩 64KB 的程序存储器。(错)60KB 3、8155 的复位引脚可与 89C51 的复位引脚直接相连。(对) 4、片内 RAM 与外部设备统一编址时,需要专门的输入/输出指令。(错)统一编址的 特点正是无需专门的输入输出指令

5、8031片内有程序存储器和数据存储器。(错)无程序存储器 6、EPROM的地址线为11条时,能访问的存储空间有4K。(错)2K 7、8255A内部有3个8位并行口,即A口,B口,C口。(对) 8、8155芯片内具有256B的静态RAM2个8位和1个6位的可编程并行V0口,1个14位定时期等常用部件 及地址锁存器。(对) 9、在单片机应用系统中,外部设备与外部数据存储器传送数据时,使用MOV指令。(错)用MOVX指令 10、为了消除按键的抖动,常用的方法有硬件和软件两种方法。(对) 8-3简答题 18031的扩展储存器系统中,为什么P0口要接一个8位锁存器,而P2口却不接? 答:这是因为P0口是扩展储存器系统的多路低8位地址和数据总线,在访问外部存储器时,PO口分时用作输出外 部储存器低8位地址和传送数据,为了在整个访问外部存储器期间,对外部存储器存在若有效的低8位地址信号, 所以PO口需要外接一个地址锁存器。A正信号就是用来把P0口输出的地址字节锁存在这个外接的锁存器中,再从 锁存器输出外部存储器的低8位地址。而P2口只用作扩展存储器系统的高8位地址线,并在整个访问外部存储器 期间不变,所以不必外接地址锁存器。 2在8031扩展系统中,外部程序存储器和数据存储器共用16位地址线和8位数据线,为什么两个存储空间不会 发生冲突? 答:这是因为外部程序存储器和外部数据存储器所使用的控制信号不同。对外部程序存储器的选读通是用PSEV控 制线,而对外部数据存储器的读/写控制是用RD和WR读、写控制线,所以不会发生地址冲突。 38031单片机需要外接程序存储器,实际上它还有多少条0线可以用?当使用外部存储器时,还剩下多少条 V0线可用? 答:8031系统必须外接程序促成器,原则上说,P0和P2口要用作数据和地址总线,所以只有P1和P3口可用作VO 口,共16条IO线。在使用外部存储器时,除了占用PO和P2口外,还需要用P3口RD(P3.7)和WR(P3.6)两 条控制线,所以这种情况下就只剩下14条1/0线可用了。 4试将8031单片机外接一片2716 EPROM和一片6116RAM组成一个应用系统,请画出硬件连线图,并指出扩 展存储器的地址范围。 答:2716是2K×8位的EPROM,6116是2K×8位的静态RAM,两者都仅需要1根地址线。由于没有规定地址 范围,故可按最简单的方式来连接,即省去地址译码器,程序存储器的地址必须从0开始,基本地址为0000一07FH 数据存储器的地址为0OOOH一O7FFH。控制线的连接为/PSEN控制EPROM的读出,RD和/WR控制RAM的读写, 两个芯片的片选端都固定接地,连线图如图所示

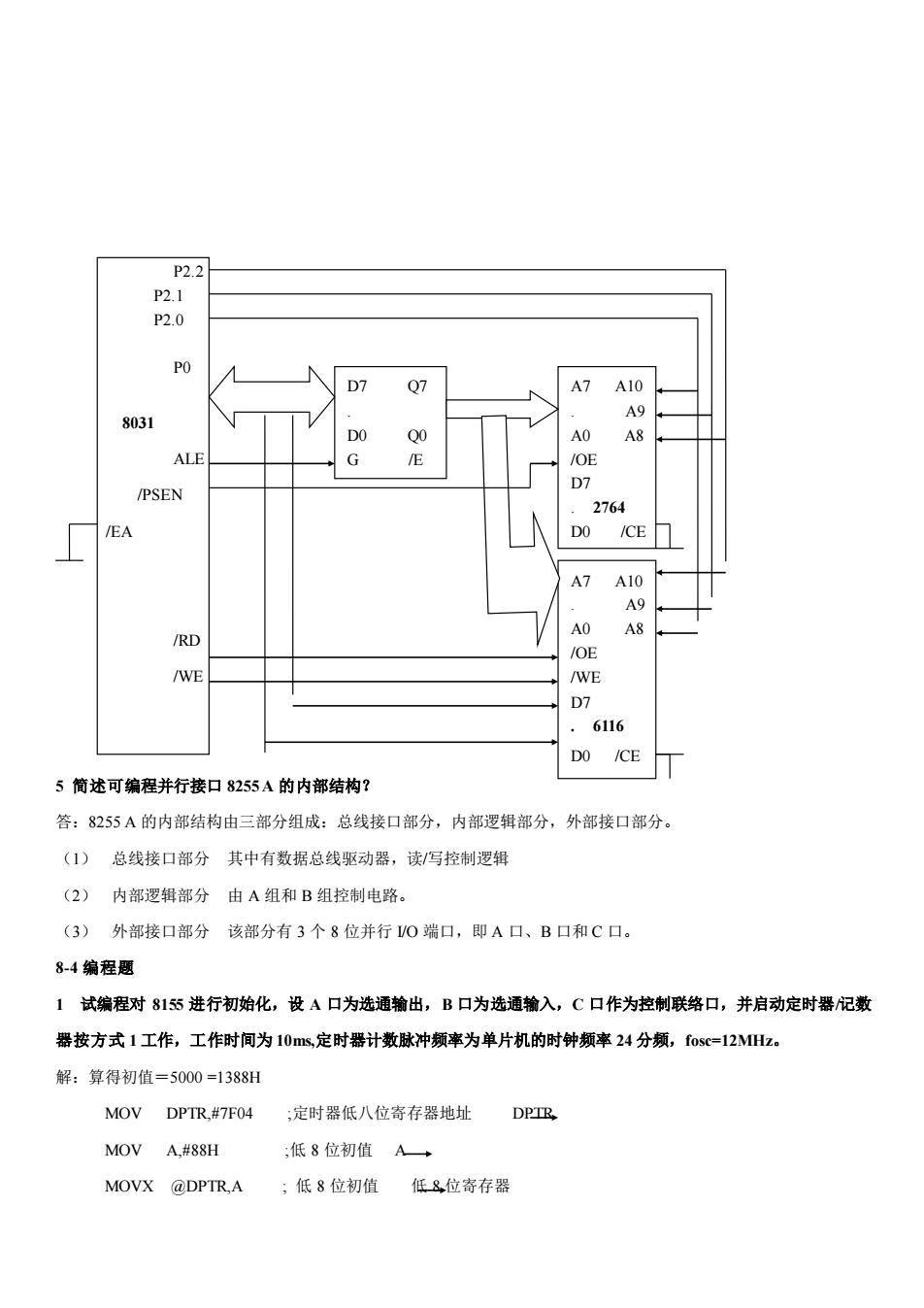

5、8031 片内有程序存储器和数据存储器。(错)无程序存储器 6、EPROM 的地址线为 11 条时,能访问的存储空间有 4K。(错)2K. 7、8255A 内部有 3 个 8 位并行口,即 A 口,B 口,C 口。(对) 8、8155 芯片内具有 256B 的静态 RAM,2 个 8 位和 1 个 6 位的可编程并行 I/O 口,1 个 14 位定时期等常用部件 及地址锁存器。(对) 9、在单片机应用系统中,外部设备与外部数据存储器传送数据时,使用 MOV 指令。(错)用 MOVX 指令。 10、为了消除按键的抖动,常用的方法有硬件和软件两种方法。(对) 8-3 简答题 1 8031 的扩展储存器系统中,为什么 P0 口要接一个 8 位锁存器,而 P2 口却不接? 答:这是因为 P0 口是扩展储存器系统的多路低 8 位地址和数据总线,在访问外部存储器时,P0 口分时用作输出外 部储存器低 8 位地址和传送数据,为了在整个访问外部存储器期间,对外部存储器存在着有效的低 8 位地址信号, 所以 P0 口需要外接一个地址锁存器。ALE 信号就是用来把 P0 口输出的地址字节锁存在这个外接的锁存器中,再从 锁存器输出外部存储器的低 8 位地址。而 P2 口只用作扩展存储器系统的高 8 位地址线,并在整个访问外部存储器 期间不变,所以不必外接地址锁存器。 2 在 8031 扩展系统中,外部程序存储器和数据存储器共用 16 位地址线和 8 位数据线,为什么两个存储空间不会 发生冲突? 答:这是因为外部程序存储器和外部数据存储器所使用的控制信号不同。对外部程序存储器的选读通是用 PSEN 控 制线,而对外部数据存储器的读/写控制是用 RD 和 WR 读、写控制线,所以不会发生地址冲突。 3 8031 单片机需要外接程序存储器,实际上它还有多少条 I/O 线可以用?当使用外部存储器时,还剩下多少条 I/O 线可用? 答:8031 系统必须外接程序促成器,原则上说,P0 和 P2 口要用作数据和地址总线,所以只有 P1 和 P3 口可用作 I/O 口,共 16 条 I/O 线。在使用外部存储器时,除了占用 P0 和 P2 口外,还需要用 P3 口 RD(P3.7)和 WR(P3.6)两 条控制线,所以这种情况下就只剩下 14 条 I/O 线可用了。 4 试将 8031 单片机外接一片 2716 EPROM 和一片 6116 RAM 组成一个应用系统,请画出硬件连线图,并指出扩 展存储器的地址范围。 答:2716 是 2K×8 位的 EPROM,6116 是 2K×8 位的静态 RAM,两者都仅需要 11 根地址线。由于没有规定地址 范围,故可按最简单的方式来连接,即省去地址译码器,程序存储器的地址必须从0开始,基本地址为0000H—07FFH。 数据存储器的地址为 0000H—07FFH。控制线的连接为/PSEN 控制 EPROM 的读出,/RD 和/WR 控制 RAM 的读写, 两个芯片的片选端都固定接地,连线图如图所示

P2.2 P2.0 Q7 A7A10 8031 A9 4A0 A8 2764 DO /CE A7 A10 /RD A0 /OE /WE /WE D7 6116 DO CE 5简述可编程并行接口8255A的内部结构? 答:8255A的内部结构由三部分组成:总线接口部分,内部逻辑部分,外部接口部分。 (1)总线接口部分其中有数据总线驱动器,读/写控制逻辑 (2)内部逻辑部分由A组和B组控制电路。 (3)外部接口部分该部分有3个8位并行V0端口,即A口、B口和C口。 84编程题 1试编程对8155进行初始化,设A口为迹通输出,B口为选通输入,C口作为控制联络口,并启动定时器记数 器按方式1工作,工作时间为10s,定时器计数脉冲颜率为单片机的时钟频率24分频,osc=12MHz, 解:算得初值=5000=1388H MOV DPTR,#7F04 ;定时器低八位寄存器地址DPTB MOV A.#88H :低8位初值A→ MOVX @DPTR,A ;低8位初值低8位寄存器

A7 A10 . A9 A0 A8 /OE /WE D7 . 6116 D0 /CE P2.2 P2.1 P2.0 P0 8031 ALE /PSEN /EA /RD /WE 5 简述可编程并行接口 8255 A 的内部结构? 答:8255 A 的内部结构由三部分组成:总线接口部分,内部逻辑部分,外部接口部分。 (1) 总线接口部分 其中有数据总线驱动器,读/写控制逻辑 (2) 内部逻辑部分 由 A 组和 B 组控制电路。 (3) 外部接口部分 该部分有 3 个 8 位并行 I/O 端口,即 A 口、B 口和 C 口。 8-4 编程题 1 试编程对 8155 进行初始化,设 A 口为选通输出,B 口为选通输入,C 口作为控制联络口,并启动定时器/记数 器按方式 1 工作,工作时间为 10ms,定时器计数脉冲频率为单片机的时钟频率 24 分频,fosc=12MHz。 解:算得初值=5000 =1388H MOV DPTR,#7F04 ;定时器低八位寄存器地址 DPTR MOV A,#88H ;低 8 位初值 A MOVX @DPTR,A ; 低 8 位初值 低 8 位寄存器 A7 A10 . A9 A0 A8 /OE D7 . 2764 D0 /CE EEEDDEE /CEE D7 Q7 . D0 Q0 G /E

INC DPTR :DPTR指向定时器高8位 MOV A.#13H :高8位初值 A MOVX@DPTR,A:高8位初值 高8位寄存器 MOV DPTR,#7F00H:8155命令寄存器地址 MOV A.0C5H :命令字A一 MOVX@DPTR.A;命令字命今寄存器 2设单片机采用8051,未扩展片外ROM,片外RAM采用一片6116,编程将其片内ROM从0100H单元 开始的10B得内容依次外接到片外RAM从100H单元开始得10B中去。 解:MOVR2,#00H ;源数据缓冲器地址偏移量00州A一→ MOV R3,#0AH :字节长度R3 MOV DPTR,#0100H ;源数据缓冲区首地址 DPTR, MOV A.R2 :源地址偏移量 A MOVC A.@A+DPTR :传送一个数据 MOVX @DPTR.A INC DPTR ;源地址(目的地址)加1 DJNZ R3.LI :数据全部传送完?没传送完,转L1继续传送 SJMP :结束 3831扩展8255A,将PA口设置成输入方式,PB口设置成输出方式,PC口设置成输出方式,给出初始化程序。 解:根据愿目要求,A口输入,B口输出,二者均采用工作方式0,则控制字为98H。编程如下: MOV A,#98H 方式控制字 A MOV DPTR,#7FFFH :选通控制寄存器 MOVX @TPTR.A :方式控制字送入8255A MOV DPTR#7FFCH MOVX A.@DPTR 读PA口数掘 MOV DPTR,#7FFDH MOVX @DPTR,A :送PB口数据

INC DPTR ;DPTR 指向定时器高 8 位 MOV A,#13H ;高 8 位初值 A MOVX @DPTR,A ;高 8 位初值 高 8 位寄存器 MOV DPTR,#7F00H ;8155 命令寄存器地址 DPTR MOV A,0C5H ;命令字 A MOVX @DPTR,A ;命令字 命令寄存器 2 设单片机采用 8051,未扩展片外 ROM,片外 RAM 采用一片 6116,编程将其片内 ROM 从 0100H 单元 开始的 10B 得内容依次外接到片外 RAM 从 100H 单元开始得 10B 中去。 解: MOV R2,#00H ;源数据缓冲器地址偏移量 00H A MOV R3,#0AH ;字节长度 R3 MOV DPTR,#0100H ;源数据缓冲区首地址 DPTR MOV A,R2 ;源地址偏移量 A MOVC A,@A+DPTR ;传送一个数据 MOVX @DPTR,A INC DPTR ;源地址(目的地址)加 1 DJNZ R3,L1 ;数据全部传送完?没传送完,转 L1 继续传送 SJMP $ ;结束 3 8031 扩展 8255A,将 PA 口设置成输入方式,PB 口设置成输出方式,PC 口设置成输出方式,给出初始化程序。 解: 根据题目要求,A 口输入,B 口输出,二者均采用工作方式 0,则控制字为 98H。编程如下: MOV A,#98H ;方式控制字 A MOV DPTR,#7FFFH ;选通控制寄存器 MOVX @TPTR,A ;方式控制字送入 8255A MOV DPTR,#7FFCH MOVX A,@DPTR ;读 PA 口数据 MOV DPTR,#7FFDH ; MOVX @DPTR,A ;送 PB 口数据

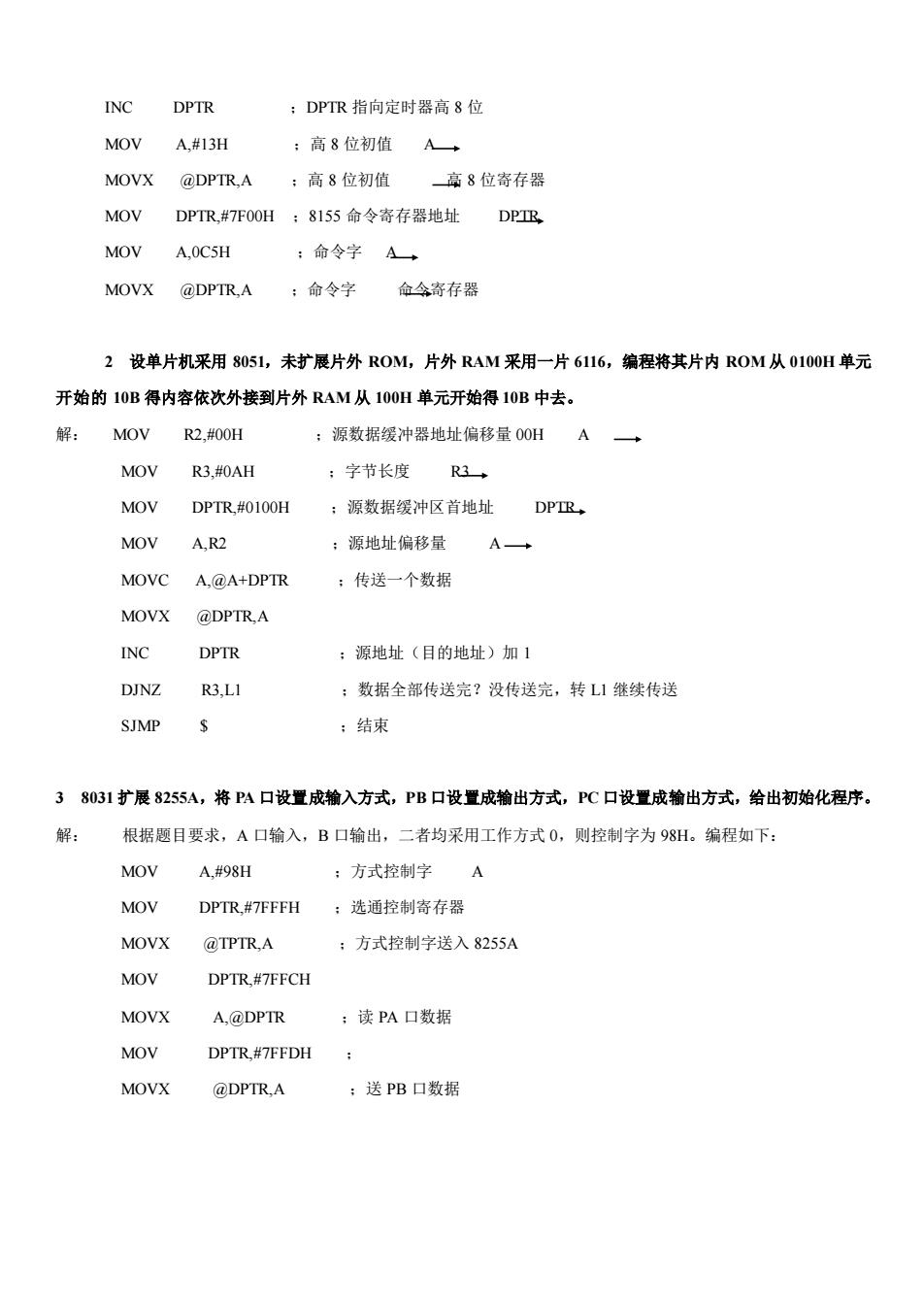

4设计一个2×2行列式盘电路并编写键盘扫描子程序, 解: (1)2×2行列式键盘电路如图所示。 8989 5V P1.7 P1.6 P1.1 P1.0 89C51 (2)键盘扫描子程序: KEY1:ACALL KSI :调用判断有无键按下子程序 JNZ LKI :有键按下,转LKI AJMP ;无键按下,返回 LKI: ACALL TI2MS :调延时12ms子程疗 ACALL KSI :查有无键按下 JNZ LK2 :若有,则为键确实按下,转逐列扫描 AJMP KEYI :无键按下,返回 LK2: MOV R4,#O0H;首列号R4一 MOVR2,FEH:首列扫描字R2→ LK4: MOV A.R2 :列扫描字P十 MOV PI,A ;使第一列线为0 MOV A,P1 :读入行状态 JB ACC.0,LONE:第0行无键按下,转查第一行 MOV A,#00:第0行有键按下,该行首健号#00A一 AJMP LKP 转求键号 LONE:JB ACC.1,NEXT;第一行无键按下,转查下一列

4 设计一个 2×2 行列式键盘电路并编写键盘扫描子程序。 解: (1)2×2 行列式键盘电路如图所示。 (2)键盘扫描子程序: KEY1: ACALL KS1 ;调用判断有无键按下子程序 JNZ LK1 ;有键按下,转 LK1 AJMP KEY1 ;无键按下,返回 LK1: ACALL T12MS ;调延时 12ms 子程序 ACALL KS1 ;查有无键按下 JNZ LK2 ;若有,则为键确实按下,转逐列扫描 AJMP KEY1 ;无键按下,返回 LK2: MOV R4,#00H ;首列号 R4 MOV R2,#FEH ;首列扫描字 R2 LK4: MOV A,R2 ;列扫描字 P1 口 MOV P1,A ;使第一列线为 0 MOV A,P1 ;读入行状态 JB ACC.0,LONE;第 0 行无键按下,转查第一行 MOV A,#00H ;第 0 行有键按下,该行首键号#00H A AJMP LKP ;转求键号 LONE: JB ACC.1,NEXT ;第一行无键按下,转查下一列 P1.7 P1.6 P1.1 P1.0 89C51 5V

MOV A402 :第一行有键按下,该行首键号#02A一 LKP: ADD A.R4 :健号=首行号十列号 PUSH ACC :键号进栈保护 LK3: ACALL KS1 :等待键释放 JNZ LK3 未释放,等特 POP AC :健释放,健号 A→ RET :键扫描结束 NEXT INC R4 :列号加1,指向下一列 MOV A.R2 :列扫描字 A→ JNB ACC.1,KND:判断2列全扫描完?扫描完,转KND RL A :没扫描完,扫描字左移一位,形成下一列扫描字 MOV R2,A :扫描字 R2→ AJMP LK4 ;扫描下一列 AJMP KEYI :全扫描完,返回 MOV A.#FCH :全扫描字1I11100B A→ MOV P1,A :全扫描字 所行行 MOV A.PI ;读取列值 CPL A ;取正逻辑,高电平表示有键按下 ANL A.#0COH 屏蔽低6位,取高2位 RET :出口状态(A)=0,有键按下 5婴求将存放在8031单片机内部RAM中30H-33H单元的4字节数据,按十六进制(8位)从做到右显示,试 编制程序。 ORG1000H:指向显示缓冲区 MOVR0,#30H:显示字节数 MOV R2,#04 初始显示位置(最高位 MOV P1,#08H :取1B SDLAY: MOV A,@RO :备份 MOV B.A ;截取字节高位 ANL A.#OFOH :装入P1.4-P1.7 ORL P1,A :准备显示右一位

MOV A,#02 ;第一行有键按下,该行首键号#02 A LKP: ADD A,R4 ;键号=首行号+列号 PUSH ACC ;键号进栈保护 LK3: ACALL KS1 ;等待键释放 JNZ LK3 ;未释放,等待 POP AC ;键释放,键号 A RET ;键扫描结束 NEXT: INC R4 ;列号加 1,指向下一列 MOV A,R2 ;列扫描字 A JNB ACC.1,KND ;判断 2 列全扫描完?扫描完,转 KND RL A ;没扫描完,扫描字左移一位,形成下一列扫描字 MOV R2,A ;扫描字 R2 AJMP LK4 ;扫描下一列 AJMP KEY1 ;全扫描完,返回 MOV A,#FCH ;全扫描字 11111100B A MOV P1,A ;全扫描字 所有行 MOV A,P1 ;读取列值 CPL A ;取正逻辑,高电平表示有键按下 ANL A,#0C0H ;屏蔽低 6 位,取高 2 位 RET ;出口状态(A)!=0,有键按下 5 要求将存放在 8031 单片机内部 RAM 中 30H—33H 单元的 4 字节数据,按十六进制(8 位)从做到右显示,试 编制程序。 ORG 1000H ;指向显示缓冲区 MOV R0,#30H ;显示字节数 MOV R2,#04 ;初始显示位置(最高位) MOV P1,#08H ;取 1B SDLAY: MOV A,@R0 ;备份 MOV B,A ;截取字节高位 ANL A,#0F0H ;装入 P1.4—P1.7 ORL P1,A ;准备显示右一位

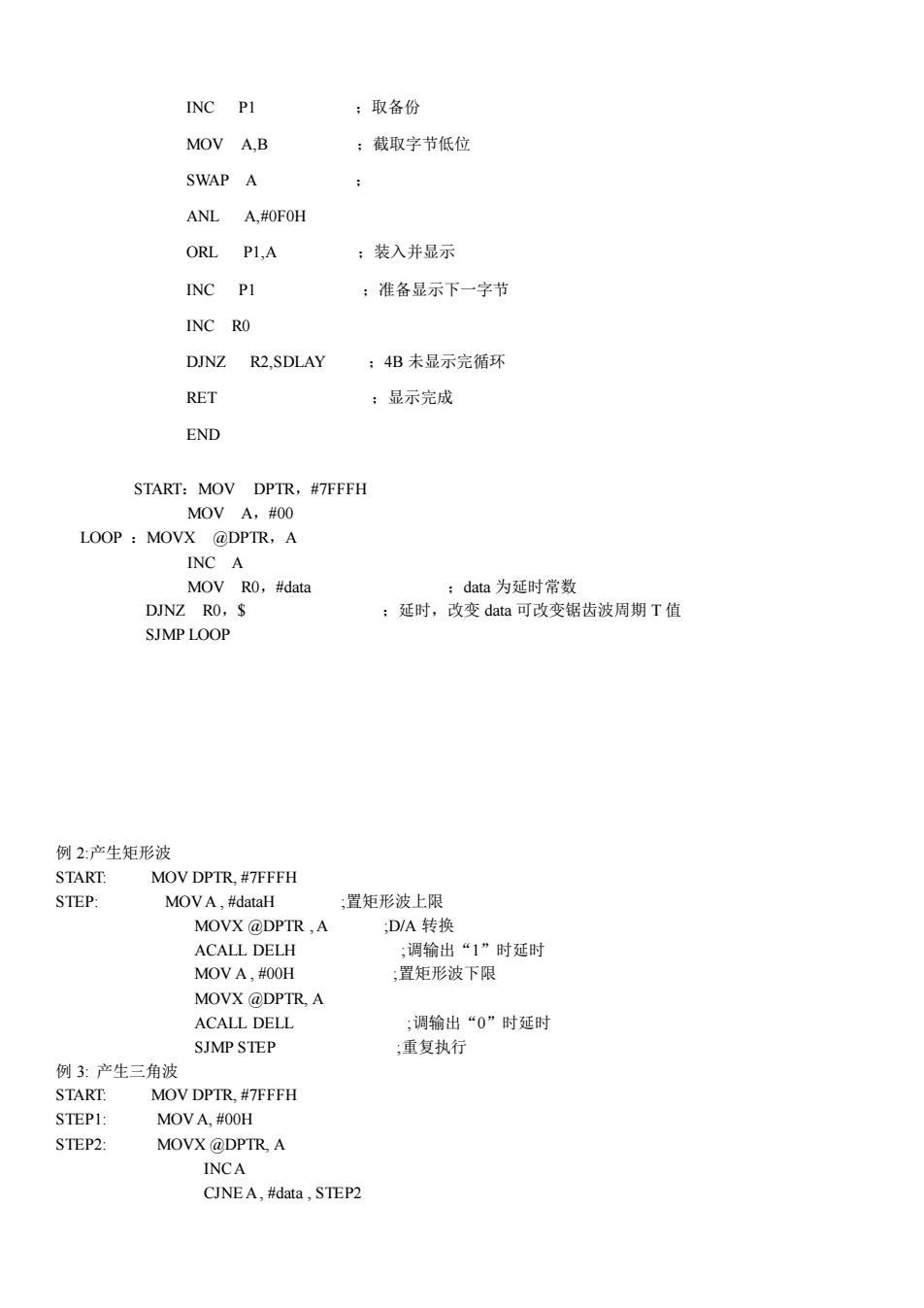

INC PI :取备份 MOV A.B :截取字节低位 SWAP A ANL A.#0FOH ORL PI.A :装入并显示 INC PI :准备显示下一字节 INC RO DJNZ R2,SDLAY 4B未显示完循环 RET :显示完成 END START:MOV DPTR,#7FFFH MOV A.#00 LOOP MOVX @DPTR.A INC A MOV RO,#data :data为延时常数 DJNZ RO,$ :延时,改变data可改变锯齿波周期T值 SJMPLOOP 例2:产生矩形波 START: MOV DPTR,#7FFFH STEP: MOVA #dataH :置矩形波上限 MOVX @DPTR,A DA转换 ACALL DELH :调输出“1”时延时 MOV A,#0OH :置矩形波下限 MOVX ODPTR A ACALL DELL ;调输出“0”时延时 SJMP STEP :重复执行 例3:产生三角波 START MOV DPTR,#7FFFH STEP1: MOVA.#00H STEP2: MOVX @DPTR.A

INC P1 ;取备份 MOV A,B ;截取字节低位 SWAP A ; ANL A,#0F0H ORL P1,A ;装入并显示 INC P1 ;准备显示下一字节 INC R0 DJNZ R2,SDLAY ;4B 未显示完循环 RET ;显示完成 END START:MOV DPTR,#7FFFH MOV A,#00 LOOP :MOVX @DPTR,A INC A MOV R0,#data ;data 为延时常数 DJNZ R0,$ ;延时,改变 data 可改变锯齿波周期 T 值 SJMP LOOP 例 2:产生矩形波 START: MOV DPTR, #7FFFH STEP: MOV A , #dataH ;置矩形波上限 MOVX @DPTR , A ;D/A 转换 ACALL DELH ;调输出“1”时延时 MOV A , #00H ;置矩形波下限 MOVX @DPTR, A ACALL DELL ;调输出“0”时延时 SJMP STEP ;重复执行 例 3: 产生三角波 START: MOV DPTR, #7FFFH STEP1: MOV A, #00H STEP2: MOVX @DPTR, A INC A CJNE A , #data , STEP2

STEP3:DECA MOVX @DPTR,A CJNEA,#01H,STEP3

STEP3: DEC A MOVX @DPTR , A CJNE A , #01H , STEP3 AJMP STEP1