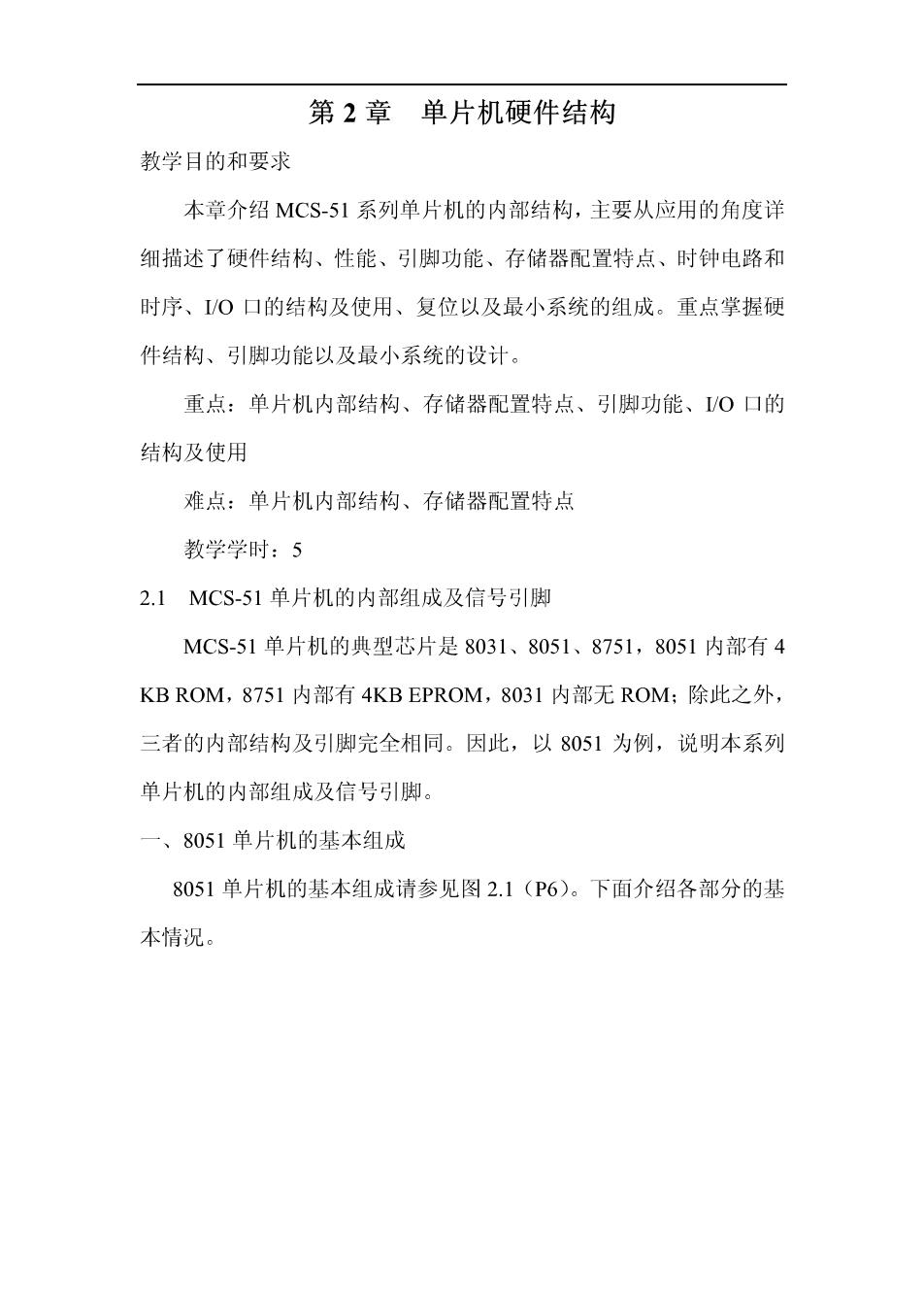

第2章单片机硬件结构 教学目的和要求 本章介绍MCS-51系列单片机的内部结构,主要从应用的角度详 细描述了硬件结构、性能、引脚功能、存储器配置特点、时钟电路和 时序、VO口的结构及使用、复位以及最小系统的组成。重点掌握硬 件结构、引脚功能以及最小系统的设计。 重点:单片机内部结构、存储器配置特点、引脚功能、VO口的 结构及使用 难点:单片机内部结构、存储器配置特点 教学学时:5 2.1MCS-51单片机的内部组成及信号引脚 MCS-51单片机的典型芯片是8031、8051、8751,8051内部有4 KB ROM,8751内部有4 KB EPROM,8031内部无ROM:除此之外, 三者的内部结构及引脚完全相同。因此,以8051为例,说明本系列 单片机的内部组成及信号引脚。 一、8051单片机的基本组成 8051单片机的基本组成请参见图2.1(P6)。下面介绍各部分的基 本情况

说明:计算机有两种结构:(单片机采用哈佛结构) 哈佛结构—程序存储器与数据存储器分开,相互独立: 普林斯顿—程序存储器与数据存储器合而为一,地址空间统 编址。 1)中央处理器(CPU)(8位) 中央处理器是单片机的核心,完成运算和控制功能。MCS-51的 CPU能处理8位二进制数或代码。 2)内部数据存储器(内部RAM)(128B) 8051芯片中共有256个RAM单元(byte),但其中后128单元 被专用寄存器占用,能作为寄存器供用户使用的只是前128单元,用 于存放可读写的数据。因此通常所说的内部数据存储器就是指前128 单元,简称内部RAM。 3)内部程序存储器(内部ROM) 8051共有4KB掩膜ROM,用于存放程序、原始数据或表格, 因此,称之为程序存储器,简称内部ROM。 说明:外部数据存储器可扩展到64KB: 外部程序存储器可扩展到64KB

4)定时/计数器 8051共有两个16位的可编程定时/计数器,以实现定时或计数功 能,并以其定时或计数结果对计算机进行控制。 5)并行IV0口 MCS-51共有4个8位的VO口(P0、P1、P2、P3,共32根线), 每个口既可以作为输入又可以作为输出,以实现数据的并行输入输 出。 6串行口 MCS-51单片机有一个全双工的串行口(2线),以实现单片机之 间或单片机与其它设备之间的串行数据传送。该串行口功能较强,既 可作为全双工异步通信收发器使用,也可作为同步移位器使用。 )中断控制系统 MCS-51单片机的中断功能较强,以满足控制应用的需要。8051 共有5个中断源,即外中断两个,定时/计数中断两个,串行中断一 个。全部中断分为高级和低级共两个优先级别。 8)时钟电路 MCS-51芯片的内部有时钟电路,但石英晶体和微调电容需外接。 时钟电路为单片机产生时钟脉冲序列。系统允许的晶振频率一般为6 MHz和12MHz。指令周期大部分位Ius;少数位2us。 二、MCS-51单片机系列 MCS-51单片机系列共有十几种芯片,如表所示。 子系列片内ROM形式 片内片内 址0特性 中断各 ROM RAM 花成KB 源)个 注 掩膜EPRO 计数 并行 串行 ROM M

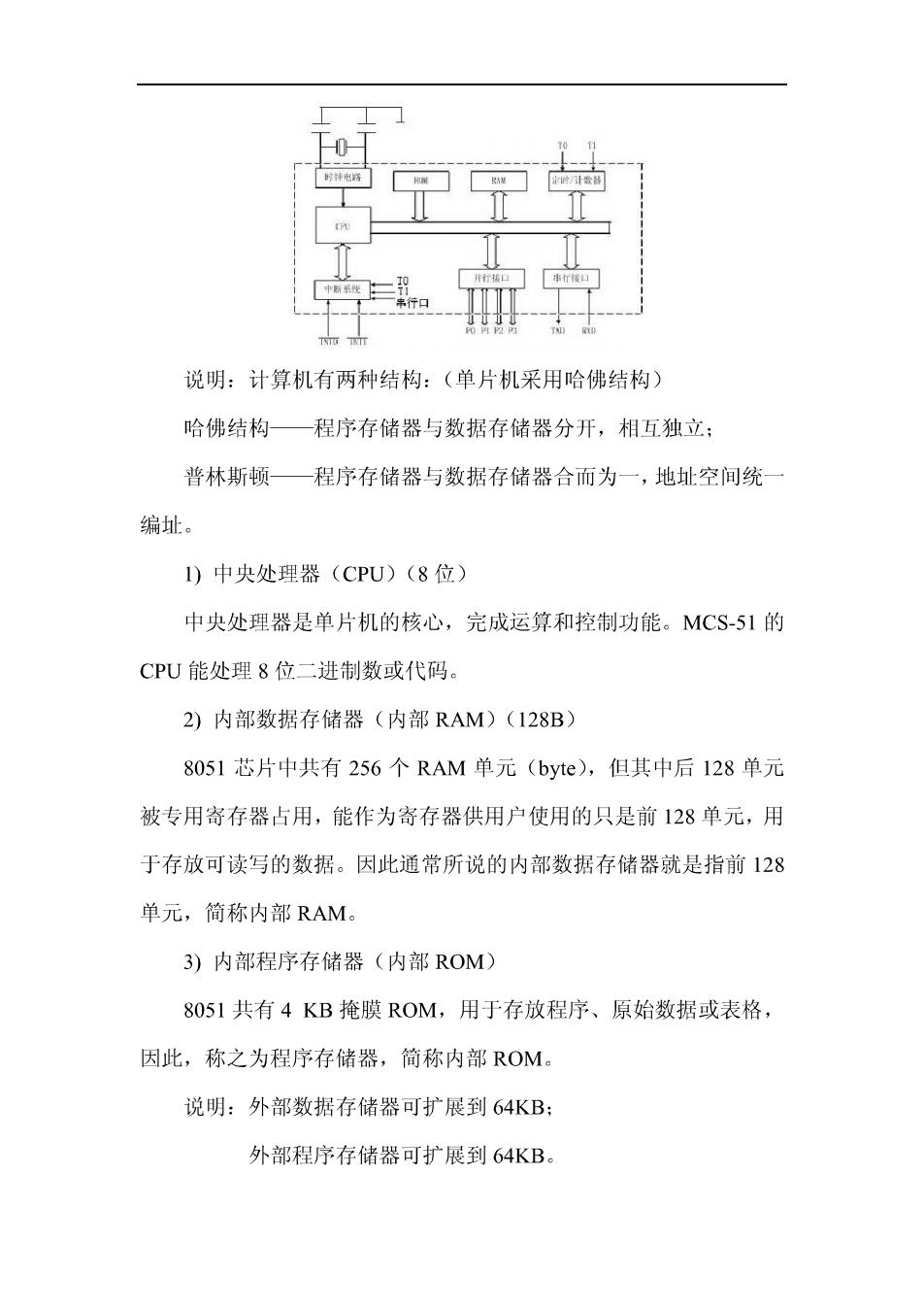

51了系8031805187514KB128B2×642×164×8 5 DIP 40 列 80c3180C5187C514KB128B2×642×164×8 52了系8032 8052 87528KB256B 2×643×16 4×8 80C3280C5287C528KB256B2×643×16 4×8 6 89Cs1 FLASH 4KB 128B2×642×168×4 5 89C2051 FLASH 2KB 128B2×642×1615 DP20脚 1.51子系列和52子系列 MCS-51系列又分为51和52两个子系列,并以芯片型号的最末 位数字作为标志。其中,51子系列是基本型,而52子系列则属增强 型。52子系列功能增强的具体方面,从表1.1所列内容中可以看出: (I)片内ROM从4KB增加到8KB。 (2)片内RAM从128B增加到256B。 (3)定时/计数器从2个增加到3个。 (4)中断源从5个增加到6个。 2.单片机芯片半导体工艺 MCS-51系列单片机采用两种半导体工艺生产。一种是HMOS工 艺,即高速度、高密度、短沟道MOS工艺。另外一种是CHMOS工 艺,即互补金屈氧化物的HMOS工艺。表2.1中,芯片型号中带有字 母“C的,为CHMOS芯片,其余均为一般的HMOS芯片。 CHMOS是CMOS和HMOS的结合,除保持了HMOS高速度和 高密度的特点之外,还具有CMOS低功耗的特点。例如8051的功耗 为630mW,而80C51的功耗只有120mW。在使携式、手提式或野 外作业仪器设备上,低功耗是非常有意义的,因此,在这些产品中必 须使用CHMOS的单片机芯片。 3.片内ROM存储器配置形式 MCS-51单片机片内程序存储器有三种配置形式,即掩膜ROM

EPROM和无ROM。一般情况下,片内带掩膜型ROM适用于定型大 批量应用产品的生产:片内带EPROM适合于研制产品样机:外接 EPROM的方式适用于研制新产品。最近,Intel公司又推出片内带可 读写只读存储器EEPROM型以及Flash闪存的单片机,可以在线写 入程序。 三、MCS-51的信号引脚功能 HMOS的MCS-51均采用标准的40引脚双列直插式封装(DIP), CHMOS的MCS-51除采用DP封装外,还采用方形封装,方形封装 有44个引脚,标有NC的4个不连线。 1、信号引脚介绍 (1)输入、输出引脚P0、P1、P2、P3(共32根) MCS-51有4个8位双向并行I/0:P0、P1、P2、P3(共32根), 每位均由锁存器、输出驱动、输入缓冲和控制电路组成。P0口位3 态双向口,负载能力8个TTL电路(每个100uA的输入电流),P1、 P2、P3为准双向口,(作为输入时,口锁存器必须值为1)负载能力 4个TTL电路。 在实际中,只有P1口提供给用户使用:P0口在访问外部存储器 时由ALE控制,分时作为数据总线和地址总线的低8位:P2口作 地址总线的高8位,P3口作特殊功能使用。 (2)电源引脚 VSS(20):接地。 VCC(40):接+5V电源。 (3)时钟电路引脚(祁伟24图)

MCS一51单片机内有一个由反向放大器构成的振荡电路。 XTAL1(19)为振荡电路的输入断,XTAL2(18)为振荡电路的输出 断。单片机可工作于以下两种时钟方式。 ①内部时钟方式:利用片内振荡电路,在XTAL2(18)和XTAL1 (19)的引脚上外接电容和石英晶体组成并联谐振电路。(通常电容 选20一50pE,晶振频率1.2一12MHz,为了保证电路的稳定性晶振和电 容应靠近单片机) ②外部时钟方式:将外部时钟信号加到XTAL2(18),XTAL1(19) 接地。(X1为振荡电路的输入端,无输入时接地,X2为振荡电路的 输出端,是内部需要时钟电路的输入端,当采用外部时钟时当然要接 在需要时钟电路的输入断)外部时钟方式用于多片单片机同时工作时 以便同步。 (4)控制信号引脚 ①RST/NPD(9)复位/备用电源 RST:复位信号输入断,高电平有效。当输入持续两个机器周期 (24个时钟周期)的高电平时即为有效,就可完成单片机的复位初 始化操作。一般在此引脚和地(VSS20)之间接一个1K的下拉电阻, 与+5V电源之间接一个22uF的电容,来完成复位。常见的复位电路 P10图2-3。 第二功能PD:备用电源引入。当电源发生故障,电压降低到下 限值时,备用电源经此端向内部RAM提供电压,以保护内部RAM 中的信息不丢失。备用电源一般由555(C℃755)电路引入。P11图2 -4

②ALE/PROG:(Address Latch Enable/programming30)地址锁存 控制信号。在系统扩展后,访问外部存储器时,ALE用于控制把P0 口输出的低8位地址锁存起来,以实现低位地址和数据的隔离。此外, 由于ALE是以晶振1/6的固定频率输出的正脉冲,(可以检测芯片的 好坏)因此,可作为外部时钟或外部定时脉冲使用。其负载功能8个 TTL电路。 第二功能PROG:对有EPROM的单片机(8751),在固化程序时, 作为编程脉 冲的输入端。 PSEN :(Program store enable29)外部程序存储器读选通信号, 低电平有效。 在从外部ROM/EPROM读取指令时,每个机器周期两次有效。 其负载功能8个TTL电路 注意:在访问内部ROM或外部RAM时,该信号不激励。 1 EA/VPP(Enable address /Voltage pulse of programming 31):程序存储器片内、片外控制信号。当信号为低电平时,对ROM 的读操作限定在外部程序存储器;当信号为高电平时,对ROM的读 操作是从内部程序存储器开始,并可延至外部程序存储器。 注意:对片内无ROM的8031、8032,需外扩EPROM,此, 接地。 第二功能VPP:在对8751片内EPROM固化程序时,此引脚施加 高达12一21V的编程电压。 说明:有内部EPROM的单片机芯片(例如8751),为写入程序

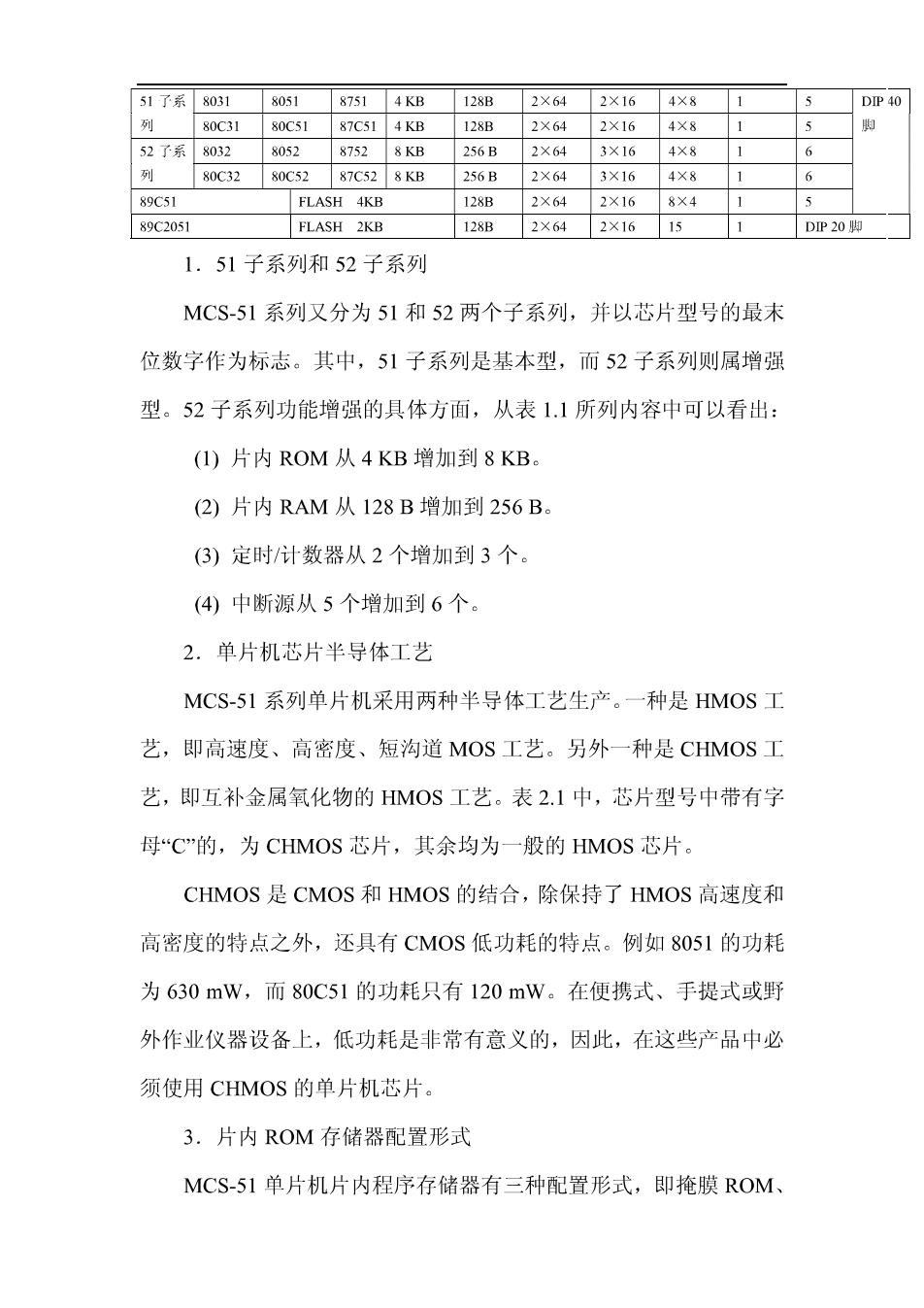

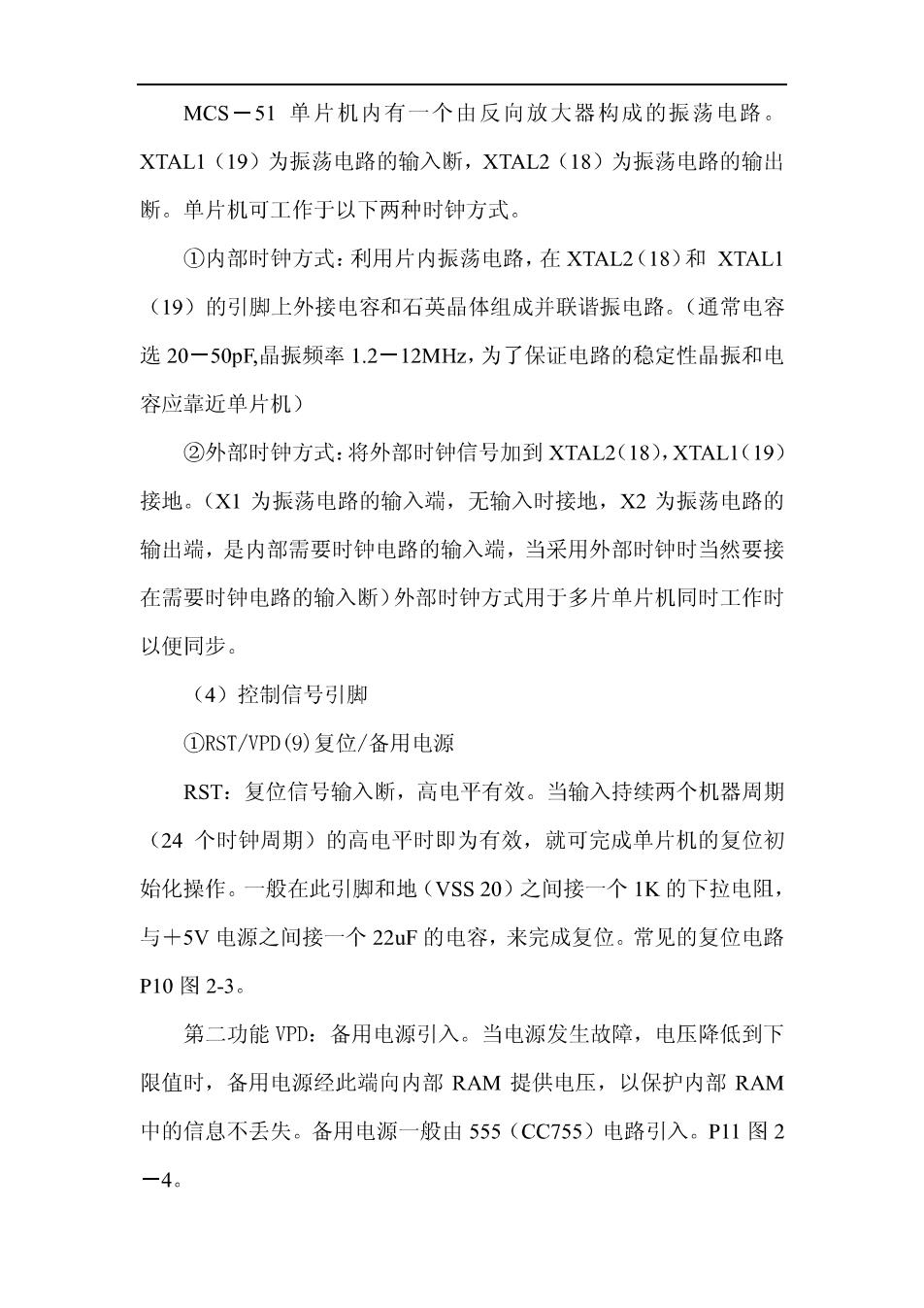

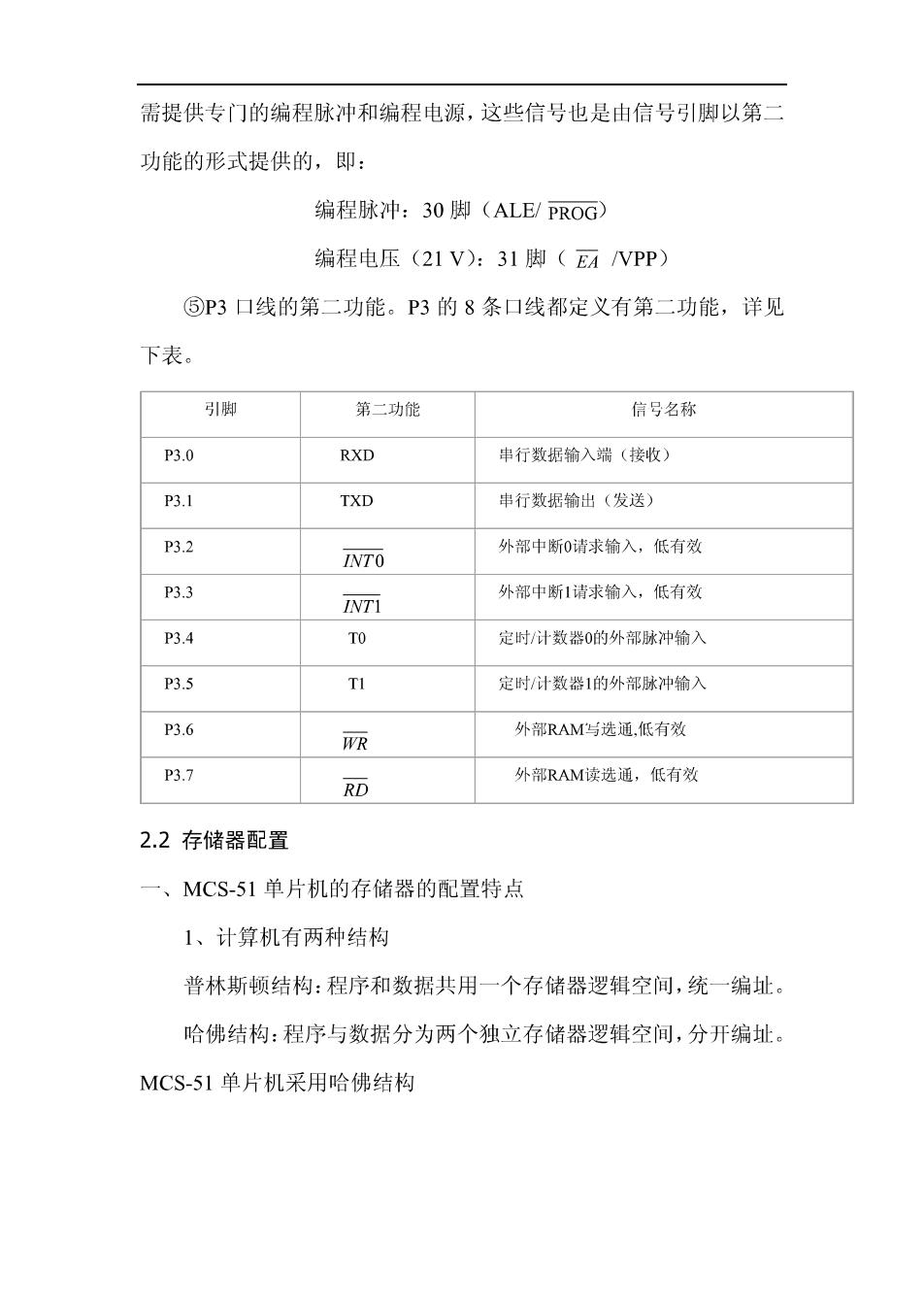

需提供专门的编程脉冲和编程电源,这些信号也是由信号引脚以第二 功能的形式提供的,即: 编程脉冲:30脚(ALE/PROG) 编程电压(21V):31脚(EA /VPP) ⑤P3口线的第二功能。P3的8条口线都定义有第二功能,详见 下表。 引脚 第二功能 信号名称 P3.0 RXD 申行数据输入端(接收) P3.1 TXD 串行数据输出(发送) P3.2 INTO 外部中断0请求输入,低有效 P3.3 INTI 外部中断1请求输入,低有效 P3.4 0 定时/计数器0的外部脉冲输入 p3.5 定时/计数器1的外部冲输入 P3.6 WR 外部RAM写选通,低有效 P3.7 外部RAM读选通,低有效 RD 2.2存储器配置 一、MCS-51单片机的存储器的配置特点 1、计算机有两种结构 普林斯顿结构:程序和数据共用一个存储器逻辑空间,统一编址。 哈佛结构:程序与数据分为两个独立存储器逻辑空间,分开编址。 MCS-51单片机采用哈佛结构

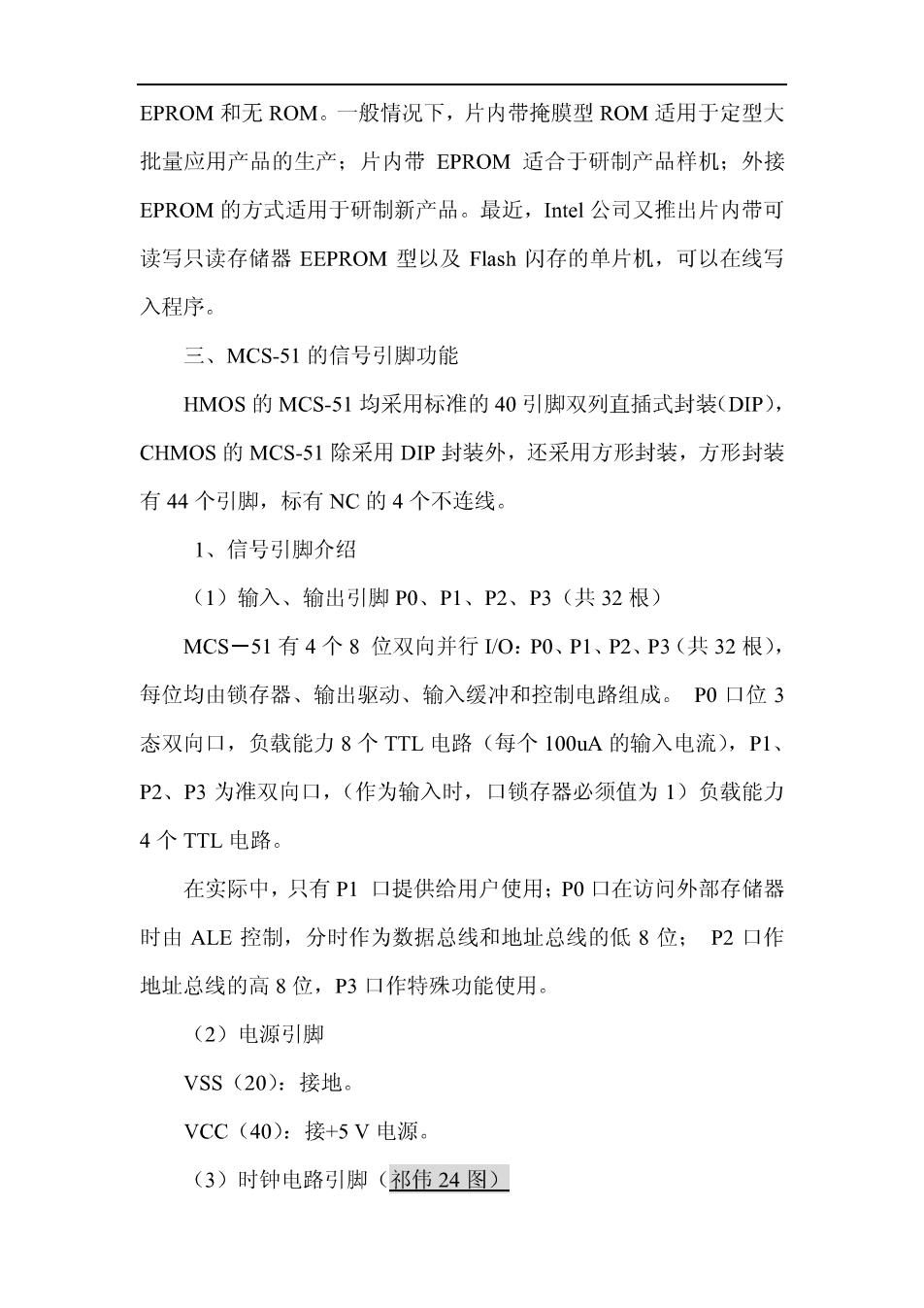

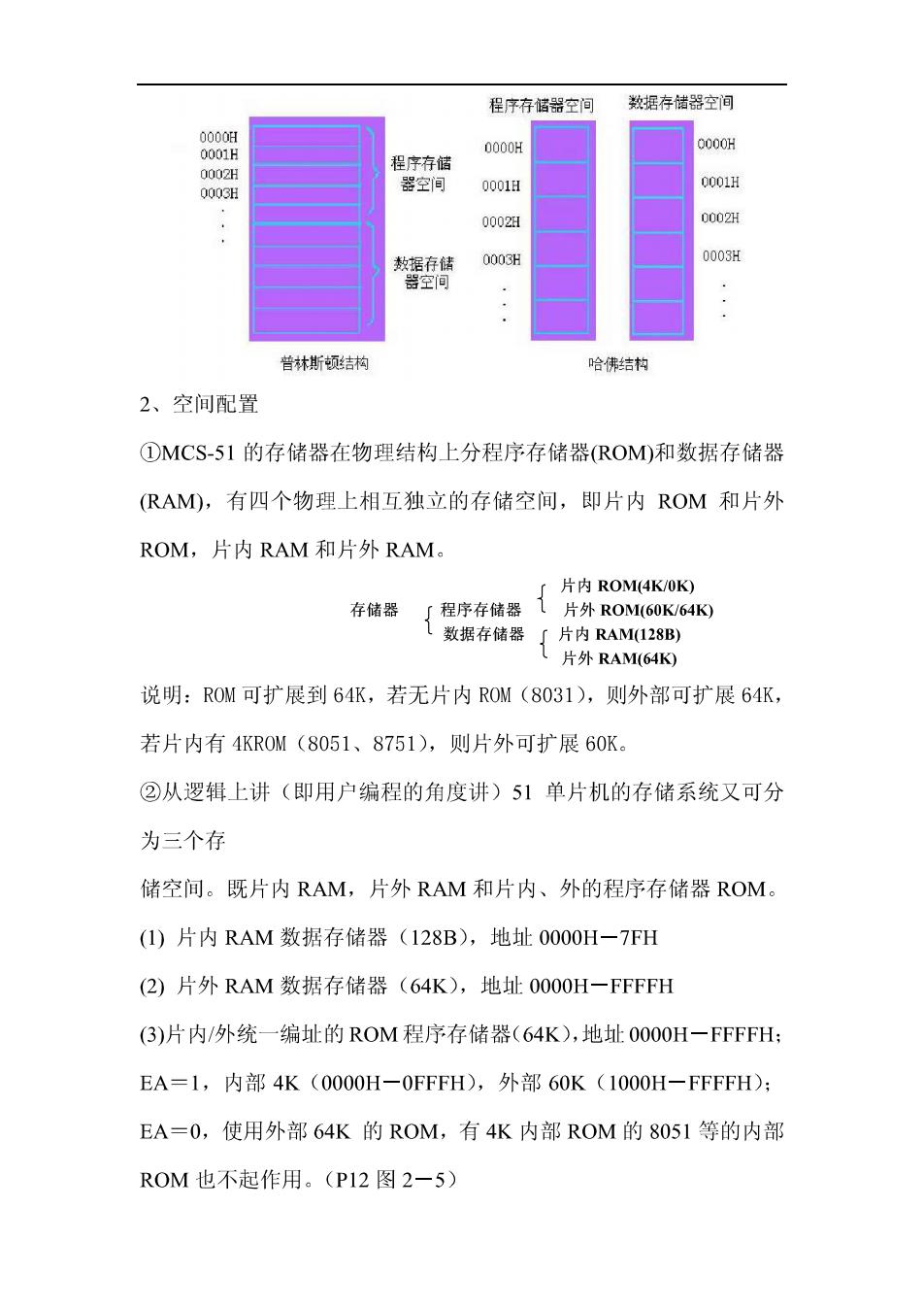

程序存器空间 熟据存储器空间 0000 0001 00001 0000H 001日 001 002 002 003 0003H 普林斯领结村 哈佛结构 2、空间配置 ①MCS-51的存储器在物理结构上分程序存储器(ROM)和数据存储器 (RAM0,有四个物理上相互独立的存储空间,即片内ROM和片外 ROM,片内RAM和片外RAM a时有保器{有纳o闲 数据存储器了片内RAM(128B) 片外RAM64K 说明:ROM可扩展到64K,若无片内ROM(8031),则外部可扩展64K 若片内有4KROM(8051、8751),则片外可扩展60K。 ②从逻辑上讲(即用户编程的角度讲)51单片机的存储系统又可分 为三个存 储空间。既片内RAM,片外RAM和片内、外的程序存储器ROM。 (1)片内RAM数据存储器(128B),地址0000H-7FH (2)片外RAM数据存储器(64K),地址0000H一FFFFH (3)片内/外统一编址的ROM程序存储器(64K),地址0000H一FFFFH: EA=1,内部4K(0000H-0FFFH),外部60K(1000H一FFFFH): EA=0,使用外部64K的ROM,有4K内部ROM的8051等的内部 ROM也不起作用。(P12图2一5)

PPPFH 程房 储器 1000 器 0000 0000H 外平烟 程流存储器 ③地址编址上 (1)片内RAM数据存储器统一编址,使用MOV指令 (2)片外RAM数据存储器统一编址,使用MOVX指令 (3)片内/外统一编址的ROM程序存储器,使用MOVC指令 二、程序存储器(ROM)Read Only Memory 1、ROM的分类 ROM按生产工艺分,又可以分为以下几种: (1)掩膜ROM:其存储的信息在制造过程中采用一道掩膜工艺生成, 一旦出厂,信息就不可改变。 (2)可编程只读存储器PROM:其存储的信息可由用户通过特殊手 段一次性写入,但只能写入一次。 (3)可擦除只读存储器:其存储的信息用户可以多次擦除,并可用 专用的编程器重新写入新的信息。可擦除只读存储器又可分为紫外线 擦除的EPROM、电擦除的EEPROM和Flash ROM