Hardware and I/control methods ●Polling(轮询方式) ●Interrupts(中断方式) ●Direct Memory Access(DMA方式) oI/O hardware summary Application I/O Interface Block and Character Devices ●Network Devices ●Clocks and Timers ●Blocking(阻塞)and Nonblocking(非阻塞)l/O ③Kernel I/O Subsystem 1/O Scheduling ● Buffering(缓冲机制) Caching,Spooling device reservation o Error Handling ●l/O Protection Kernel Data Structures Transforming I/O Requests to Hardware Operations Performance 6小结 陈香兰xlanchen@ustc.edu.cn http:/作taf.u01174O1i:Operating System操作系统原理 May22,20193/54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 提纲1 I/O Hardware and I/O control methods Polling (轮询方式) Interrupts (中断方式) Direct Memory Access (DMA方式) I/O hardware summary 2 Application I/O Interface Block and Character Devices Network Devices Clocks and Timers Blocking (阻塞) and Nonblocking (非阻塞) I/O 3 Kernel I/O Subsystem I/O Scheduling Buffering (缓冲机制) Caching, Spooling & device reservation Error Handling I/O Protection Kernel Data Structures 4 Transforming I/O Requests to Hardware Operations 5 Performance 6 小结 陈香兰 xlanchen@ustc.edu.cn http://staff.ustc.edu.cn/~xlanchen (Computer Application Laboratory, CS, USTC @ Hefei Embedded System Laboratory, CS, USTC @ Suzhou) 0117401: Operating System 操作系统原理与设计 May 22, 2019 3 / 54

Overview o The role of OS in I/O is to manage and control I/O operations and I/O devices connected to the computer. Challenge:I/O devices vary widely. oHOW:a combination of HW and SW techniques. Chapter Objectives To explore the structure of an OS's I/O subsystem. To discuss the principles of I/O HW and its complexity. o To provide details of the performance aspects of I/O HW and SW. 口1回年走1,2月Q0 陈香兰xlanchen@ustc.edu.cn http:/staf仟.u011740i:Operating System操作系统原理 May22,20194/54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Overview The role of OS in I/O is to manage and control I/O operations and I/O devices connected to the computer. Challenge: I/O devices vary widely. HOW: a combination of HW and SW techniques. Chapter Objectives To explore the structure of an OS’s I/O subsystem. To discuss the principles of I/O HW and its complexity. To provide details of the performance aspects of I/O HW and SW. 陈香兰 xlanchen@ustc.edu.cn http://staff.ustc.edu.cn/~xlanchen (Computer Application Laboratory, CS, USTC @ Hefei Embedded System Laboratory, CS, USTC @ Suzhou) 0117401: Operating System 操作系统原理与设计 May 22, 2019 4 / 54

Outline 1/O Hardware and I/O control methods ●Polling(轮询方式) o Interrupts(中断方式) ●Direct Memory Access(DMA方式) o I/O hardware summary 口1⊙生年12月0C 陈话兰xlanchen@ustc.edu:cn http/staff.u0117401 Operating System操作系统原理斐 May22,20195/54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Outline 1 I/O Hardware and I/O control methods Polling (轮询方式) Interrupts (中断方式) Direct Memory Access (DMA方式) I/O hardware summary 陈香兰 xlanchen@ustc.edu.cn http://staff.ustc.edu.cn/~xlanchen (Computer Application Laboratory, CS, USTC @ Hefei Embedded System Laboratory, CS, USTC @ Suzhou) 0117401: Operating System 操作系统原理与设计 May 22, 2019 5 / 54

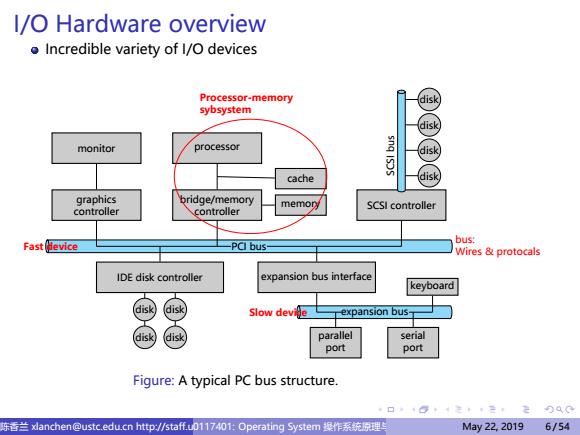

I/O Hardware overview o Incredible variety of I/O devices Processor-memory disk sybsystem disk monitor processor snq ISS disk cache disk graphics bridge/memory memon SCSI controller controller controller Fastevice bus: PCI bus Wires protocals IDE disk controller expansion bus interface keyboard disk Slow devige -expansion bus disk parallel serial port port Figure:A typical PC bus structure. 陈话兰xlanchen@ustc.edu:cn http:/staff.u0117401.Operating System操作系统原理 May22,20196/54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . I/O Hardware overview Incredible variety of I/O devices PCI bus graphics controller monitor bridge/memory controller processor memory cache SCSI controller SCSI bus disk disk disk disk IDE disk controller disk disk disk disk expansion bus interface expansion bus parallel port serial port keyboard bus: Wires & protocals Fast device Slow device Processor-memory sybsystem Figure: A typical PC bus structure. 陈香兰 xlanchen@ustc.edu.cn http://staff.ustc.edu.cn/~xlanchen (Computer Application Laboratory, CS, USTC @ Hefei Embedded System Laboratory, CS, USTC @ Suzhou) 0117401: Operating System 操作系统原理与设计 May 22, 2019 6 / 54

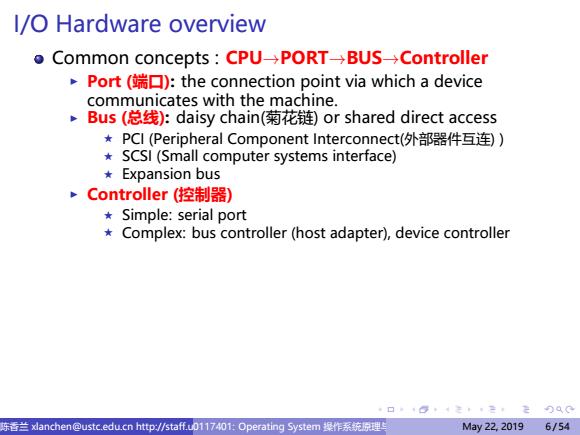

1/O Hardware overview o Common concepts:CPU→PoRT→BUS→Controller -Port(端▣):the connection point via which a device communicates with the machine. ,Bus(总线):daisy chain(菊花链)or shared direct access *PCI(Peripheral Component Interconnect(外部器件互连)) SCSI(Small computer systems interface) ★Expansion bus ~Controller(控制器) Simple:serial port Complex:bus controller (host adapter),device controller 口⊙注,1,2月00 陈适兰xlanchen@ustc.edu.cn http:/staf.u01174O1:Operating System操作系统原理斐 May22,20196/54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . I/O Hardware overview Common concepts : CPU→PORT→BUS→Controller ▶ Port (端口): the connection point via which a device communicates with the machine. ▶ Bus (总线): daisy chain(菊花链) or shared direct access ⋆ PCI (Peripheral Component Interconnect(外部器件互连) ) ⋆ SCSI (Small computer systems interface) ⋆ Expansion bus ▶ Controller (控制器) ⋆ Simple: serial port ⋆ Complex: bus controller (host adapter), device controller 陈香兰 xlanchen@ustc.edu.cn http://staff.ustc.edu.cn/~xlanchen (Computer Application Laboratory, CS, USTC @ Hefei Embedded System Laboratory, CS, USTC @ Suzhou) 0117401: Operating System 操作系统原理与设计 May 22, 2019 6 / 54

1/O Hardware overview o How can the processor command controller? Controller has one or more registers for data and control signals. The processor communicates with the controller by reading and writing bit patterns in the registers. o Two communication techniques: Direct l/O instructions Access the port address Each port typically contains of four registers,i.e.,status,control, data-in and data-out. Instructions:In,out ②Memory-mapped I/o Example:Oxa0000~Oxfffff are reserved to ISA graphics cards and BIOS routines Some systems use both techniques:PC as an example. 口18,走卡1,月00 陈话兰xlanchen@ustc.edu.cn http/staff.u0117401 Operating System操作系统原理斐 May22,20196/54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . I/O Hardware overview How can the processor command controller? ▶ Controller has one or more registers for data and control signals. ▶ The processor communicates with the controller by reading and writing bit patterns in the registers. Two communication techniques: 1 Direct I/O instructions ⋆ Access the port address ⋆ Each port typically contains of four registers, i.e., status, control, data-in and data-out. ⋆ Instructions: In, out 2 Memory-mapped I/O ⋆ Example: 0xa0000 ~ 0xfffff are reserved to ISA graphics cards and BIOS routines ▶ Some systems use both techniques: PC as an example. 陈香兰 xlanchen@ustc.edu.cn http://staff.ustc.edu.cn/~xlanchen (Computer Application Laboratory, CS, USTC @ Hefei Embedded System Laboratory, CS, USTC @ Suzhou) 0117401: Operating System 操作系统原理与设计 May 22, 2019 6 / 54

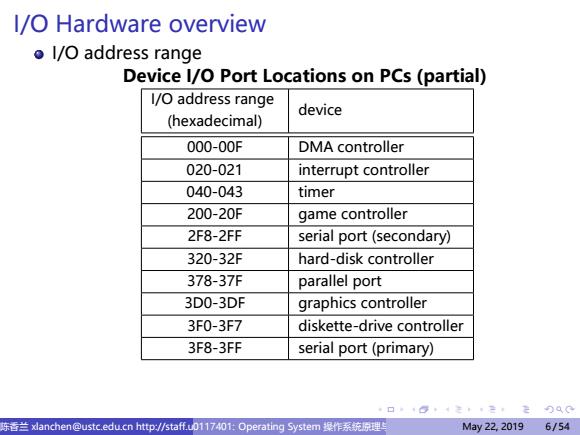

I/O Hardware overview 1/O address range Device l/O Port Locations on PCs(partial) I/O address range device (hexadecimal) 000-00F DMA controller 020-021 interrupt controller 040-043 timer 200-20F game controller 2F8-2FF serial port(secondary) 320-32F hard-disk controller 378-37F parallel port 3D0-3DF graphics controller 3F0-3F7 diskette-drive controller 3F8-3FF serial port(primary) 东香兰xlanchen@ustc,edu.cn http:/staff..u011740i:Operating System操作系统原理 May22,20196/54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . I/O Hardware overview I/O address range Device I/O Port Locations on PCs (partial) I/O address range device (hexadecimal) 000-00F DMA controller 020-021 interrupt controller 040-043 timer 200-20F game controller 2F8-2FF serial port (secondary) 320-32F hard-disk controller 378-37F parallel port 3D0-3DF graphics controller 3F0-3F7 diskette-drive controller 3F8-3FF serial port (primary) 陈香兰 xlanchen@ustc.edu.cn http://staff.ustc.edu.cn/~xlanchen (Computer Application Laboratory, CS, USTC @ Hefei Embedded System Laboratory, CS, USTC @ Suzhou) 0117401: Operating System 操作系统原理与设计 May 22, 2019 6 / 54

1/O Control Methods ●Polling(轮询方式) ②Interrupts(中断方式) ODMA(DMA方式) O(在汤书上:还有通道的概念) 口1⊙生年12月00 陈话兰xlanchen@ustc.edu.cn http/staff.u0117401 Operating System操作系统原理斐 May22,20197/54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . I/O Control Methods 1 Polling (轮询方式) 2 Interrupts (中断方式) 3 DMA (DMA方式) 4 (在汤书上:还有通道的概念) 陈香兰 xlanchen@ustc.edu.cn http://staff.ustc.edu.cn/~xlanchen (Computer Application Laboratory, CS, USTC @ Hefei Embedded System Laboratory, CS, USTC @ Suzhou) 0117401: Operating System 操作系统原理与设计 May 22, 2019 7 / 54

Outline I/O Hardware and I/O control methods ●Polling(轮询方式) o Interrupts(中断方式) Direct Memory Access(DMA方式 o 1/O hardware summary 口1⊙生年12月00 东香兰xlanchen@ustc,edu.cn http:/staff..u0117401:Operating System操作系统原理 May22,20198/54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Outline 1 I/O Hardware and I/O control methods Polling (轮询方式) Interrupts (中断方式) Direct Memory Access (DMA方式) I/O hardware summary 陈香兰 xlanchen@ustc.edu.cn http://staff.ustc.edu.cn/~xlanchen (Computer Application Laboratory, CS, USTC @ Hefei Embedded System Laboratory, CS, USTC @ Suzhou) 0117401: Operating System 操作系统原理与设计 May 22, 2019 8 / 54

Polling(轮询方式) o Need handshaking(握手) o State of device command-ready In command register 1:a command is available for the controller busy In status register *0:ready for the next command;1:busy ③Error To indicate whether an l/O is ok. 口1⊙生年12月0C 陈话兰xlanchen@ustc.edu.cn http/staff.u0117401 Operating System操作系统原理斐 May22,20199/54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Polling (轮询方式) Need handshaking (握手) State of device 1 command-ready ⋆ In command register ⋆ 1: a command is available for the controller 2 busy ⋆ In status register ⋆ 0: ready for the next command; 1: busy 3 Error ⋆ To indicate whether an I/O is ok. 陈香兰 xlanchen@ustc.edu.cn http://staff.ustc.edu.cn/~xlanchen (Computer Application Laboratory, CS, USTC @ Hefei Embedded System Laboratory, CS, USTC @ Suzhou) 0117401: Operating System 操作系统原理与设计 May 22, 2019 9 / 54