《并行计算:Parallel Computing》 结构 编程算法应用 §2.1并行计算机系统结构模型 (第一部分) 徐悦牲Yueshen Xu) ysxu@xidian.edu.cn 软件工程系 西安电子科技大学

§2.1 并行计算机系统结构模型 (第一部分) 徐悦甡(Yueshen Xu) ysxu@xidian.edu.cn 软件工程系 西安电子科技大学 《并行计算:Parallel Computing》 结构 编程 算法 应用

本节提纲 历些毛子代枝大等 XIDIAN UNIVERSITY ▣并行计算机体系结构分类 ■通用计算机体系结构 ■F引ynn的四种体系结构划分方法 从处理器的角度 ■并行计算机体系结构的具体实现 ■并行计算机体系结构多种实现的比较 ▣并行计算机访存模型 ■均匀存储访问与非均匀存储访问 ■高速缓存存储访问 从存储器的角度 ■ 非远程存储访问模型等 ■体系结构与访存模型的关系

并行计算机体系结构分类 通用计算机体系结构 Flynn的四种体系结构划分方法 并行计算机体系结构的具体实现 并行计算机体系结构多种实现的比较 从处理器的角度 并行计算机访存模型 均匀存储访问与非均匀存储访问 高速缓存存储访问 非远程存储访问模型等 体系结构与访存模型的关系 本节提纲 从存储器的角度

学习动机 历些荒子种枚大》 XIDIAN UNIVERSITY ▣为什么要学习并行计算机体系结构 ■知识体系的完整性 >与其它学校的同类专业竞争 并行计算应用 >中科大,哈工大,南大 并行算法设计 ■职业发展的可能性 知识栈 并行与并发 >并行计算平台架构师 编程 >并行计算平台高级工程到师 并行计算机体系 结构 >并行计算机体系结构设计师 ■教学大纲的要求 >而且内容本身也很有趣

学习动机 为什么要学习并行计算机体系结构 并行计算机体系 结构 并行与并发 编程 并行算法设计 并行计算应用 知识栈 知识体系的完整性 ➢ 与其它学校的同类专业竞争 ➢ 中科大,哈工大,南大 职业发展的可能性 ➢ 并行计算平台架构师 ➢ 并行计算平台高级工程师 ➢ 并行计算机体系结构设计师 教学大纲的要求 ➢ 而且内容本身也很有趣

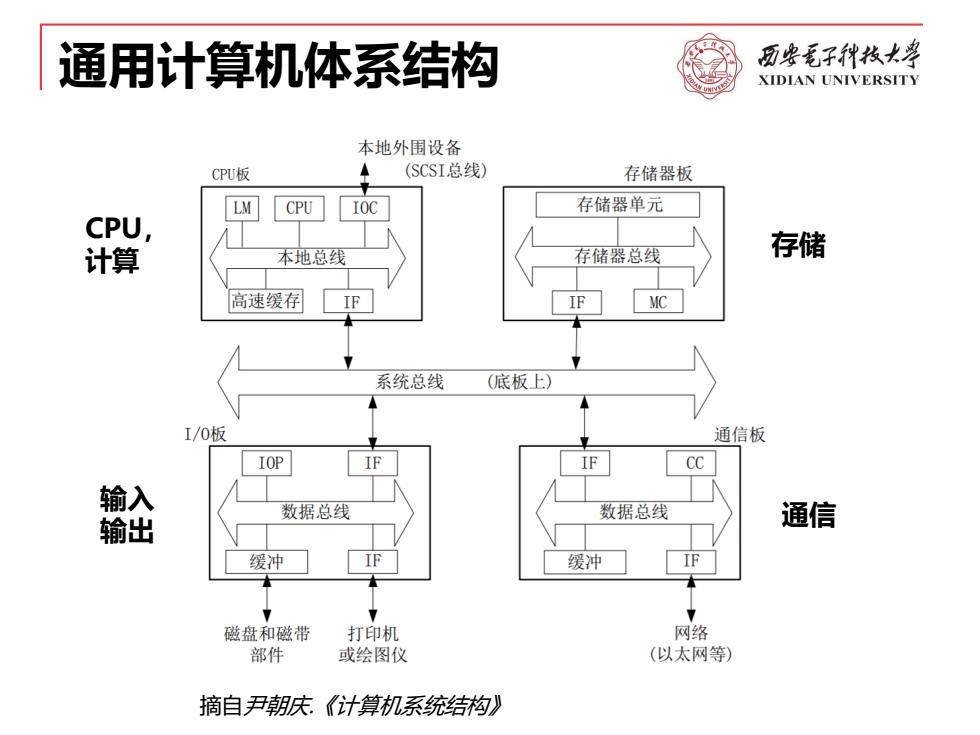

通用计算机体系结构 历些毛子代枝大等 XIDIAN UNIVERSITY 本地外围设备 CPU板 (SCSI总线) 存储器板 LM CPU 存储器单元 CPU, 计算 本地总线 存储器总线 存储 高速缓存 IF IF MC 系统总线 (底板上) I/0板 通信板 IOP CC 输入 数据总线 数据总线 输出 通信 缓冲 IF 缓冲 IF 磁盘和磁带 打印机 网络 部件 或绘图仪 (以太网等) 摘自尹潮庆.《计算机系统结构》

通用计算机体系结构 摘自尹朝庆.《计算机系统结构》 CPU, 计算 输入 输出 存储 通信

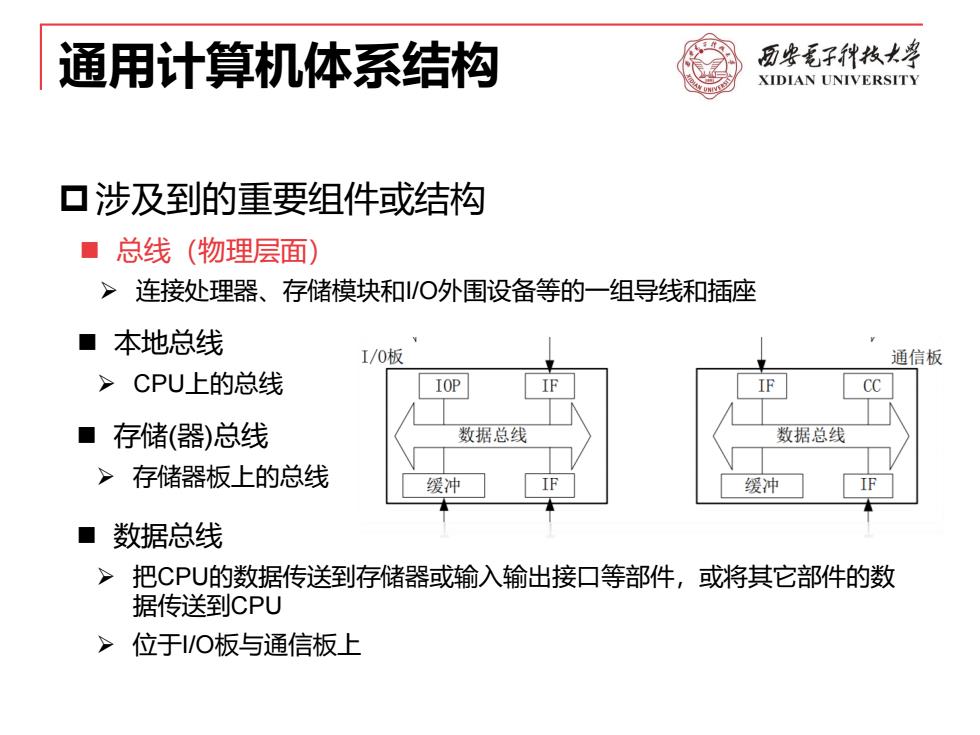

通用计算机体系结构 历些莞子种拔大多 XIDIAN UNIVERSITY ▣涉及到的重要组件或结构 ■总线(物理层面) >连接处理器、存储模块和/○外围设备等的一组导线和插座 ■本地总线 I/0板 通信板 >CPU上的总线 IOP IF IF CC ■存储(器)总线 数据总线 数据总线 >存储器板上的总线 缓冲 IF 缓冲 ■数据总线 > 把CPU的数据传送到存储器或输入输出接口等部件,或将其它部件的数 据传送到CPU 位于/O板与通信板上

通用计算机体系结构 涉及到的重要组件或结构 本地总线 ➢ CPU上的总线 总线(物理层面) ➢ 连接处理器、存储模块和I/O外围设备等的一组导线和插座 存储(器)总线 ➢ 存储器板上的总线 数据总线 ➢ 把CPU的数据传送到存储器或输入输出接口等部件,或将其它部件的数 据传送到CPU ➢ 位于I/O板与通信板上

通用计算机体系结构 历些毛子种枝大等 XIDIAN UNIVERSITY ■SCSl总线(Small Computer System Interface) NARROW SCSI WIDE SCSI WIDE SCSI DB 25 pin Very High Wido 68 pin connector > /O总线的一种,通用接口标准,用于与多种 类型的外设进行通信 ■各插入板上较通用的组件 >IOC:input/output controller,l/O控制器 >IOP:input//output processor,l/O处理器 NARROW SCS NARROW SCSI High Density 50-pin Contronic connector >IF:interface logic,专用逻辑接口 本地外围设备 >LM:local memory,局部存储器 CPU板 (SCSI总线) >MC:memory controller,存储器控制器 LM CPU >CC:communication controller,通信控 制器 本地总线 高速缓存

通用计算机体系结构 SCSI总线(Small Computer System Interface) ➢ I/O总线的一种,通用接口标准,用于与多种 类型的外设进行通信 各插入板上较通用的组件 ➢ IF:interface logic,专用逻辑接口 ➢ LM:local memory,局部存储器 ➢ MC:memory controller,存储器控制器 ➢ CC:communication controller,通信控 制器 ➢ IOC:input/output controller,I/O控制器 ➢ IOP:input/output processor,I/O处理器

并行计算机体系结构分类 历些毛子种枝大》 XIDIAN UNIVERSITY ▣Flynn指令流:机器执行的指令序列 数据流:由指令流调用的数据序列,包括输入数据和中间结果 SISD (Single instruction stream,single data stream),单指令流单数据流 SIMD(Single instruction stream,multiple Flynn data streams),单指令流多数据流 分类法 MISD(Multiple instruction streams,single data stream),多指令流单数据流 Michael J. MIMD(Multiple instruction streams Flynn multiple data streams),多指令流多数据流

并行计算机体系结构分类 Flynn分类法 分类依据:指令流和数据流的执行方式 Michael J. Flynn Flynn 分类法 SISD (Single instruction stream, single data stream),单指令流 单数据流 MIMD(Multiple instruction streams, multiple data streams ),多指令流 多数据流 SIMD(Single instruction stream, multiple data streams),单指令流 多数据流 MISD(Multiple instruction streams, single data stream),多指令流 单数据流 ➢ 指令流:机器执行的指令序列 ➢ 数据流:由指令流调用的数据序列,包括输入数据和中间结果

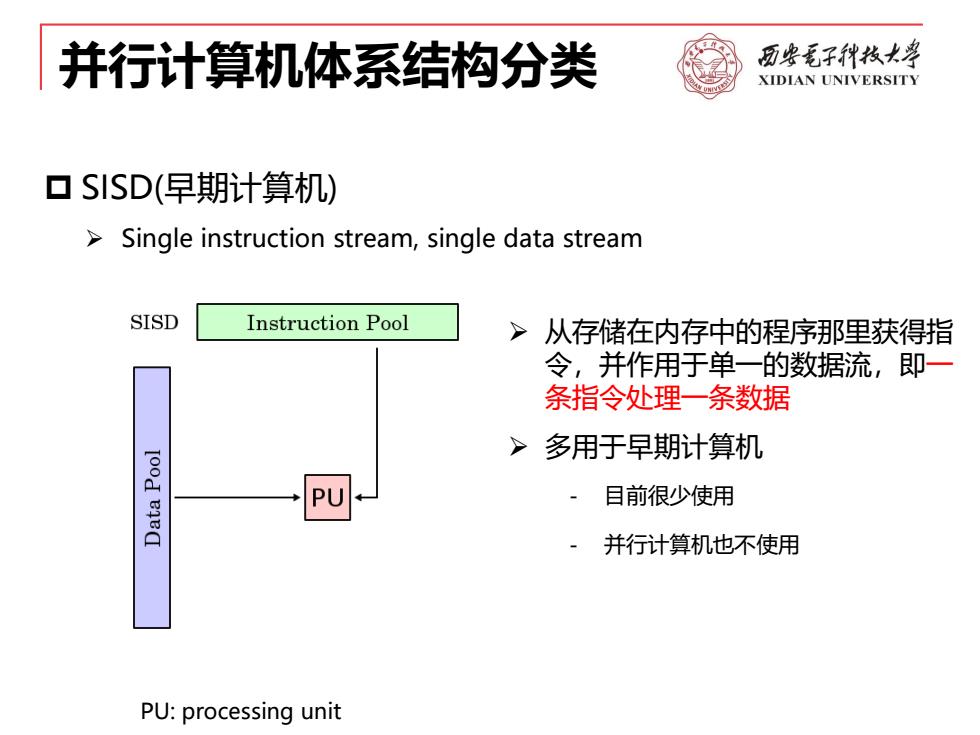

并行计算机体系结构分类 历些毛子种枝大” XIDIAN UNIVERSITY ▣SISD(早期计算机) >Single instruction stream,single data stream SISD Instruction Pool 从存储在内存中的程序那里获得指 令,并作用于单一的数据流,即一 条指令处理一条数据 > 多用于早期计算机 Iood 目前很少使用 ·并行计算机也不使用 PU:processing unit

并行计算机体系结构分类 SISD(早期计算机) ➢ Single instruction stream, single data stream ➢ 从存储在内存中的程序那里获得指 令,并作用于单一的数据流,即一 条指令处理一条数据 ➢ 多用于早期计算机 - 目前很少使用 - 并行计算机也不使用 PU: processing unit

并行计算机体系结构分类 历忠毛子代枚大兽 XIDIAN UNIVERSITY ▣ SIMD(单核计算机) >Single instruction stream,multiple data streams SIMD Instruction Pool 单条的指令流作用于多于一个的 数据流上,在单个时钟周期内处 理多个数据单元 >主要用于单核计算机 Iood BIEC ·不是并行计算机的主流模式 PU:processing unit

并行计算机体系结构分类 SIMD(单核计算机) ➢ Single instruction stream, multiple data streams ➢ 单条的指令流作用于多于一个的 数据流上,在单个时钟周期内处 理多个数据单元 ➢ 主要用于单核计算机 - 不是并行计算机的主流模式 PU: processing unit

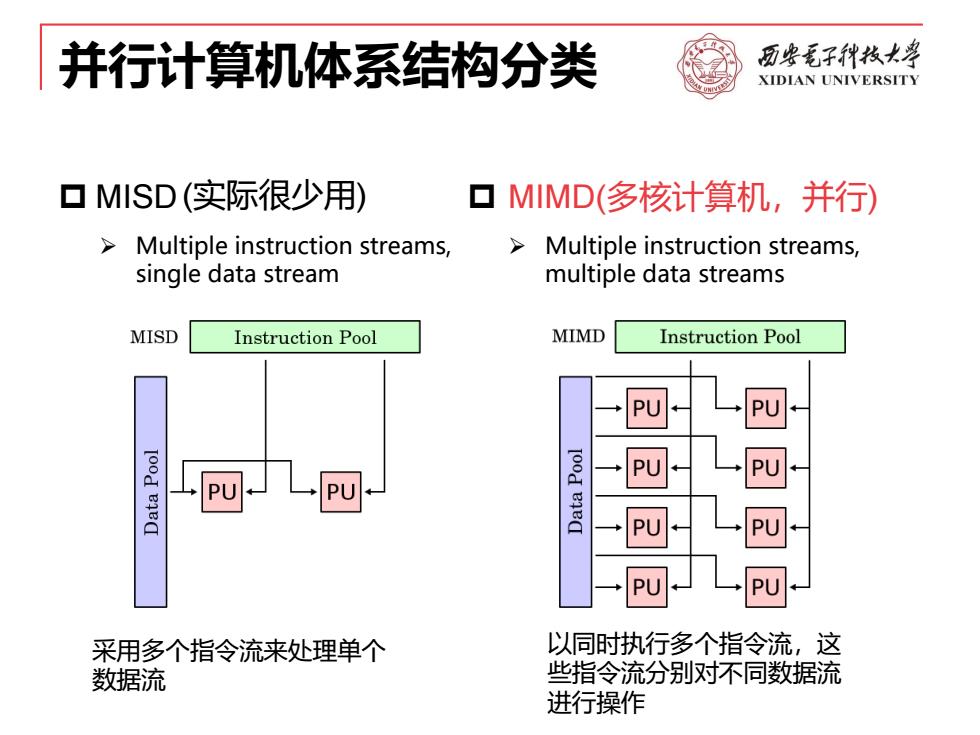

并行计算机体系结构分类 历些毛子种枝大等 XIDIAN UNIVERSITY 口MISD(实际很少用) 口MIMD(多核计算机,并行) Multiple instruction streams, Multiple instruction streams, single data stream multiple data streams MISD Instruction Pool MIMD Instruction Pool PU PU 采用多个指令流来处理单个 以同时执行多个指令流,这 数据流 些指令流分别对不同数据流 进行操作

并行计算机体系结构分类 MISD ➢ Multiple instruction streams, single data stream 采用多个指令流来处理单个 数据流 MIMD(多核计算机,并行) ➢ Multiple instruction streams, multiple data streams 以同时执行多个指令流,这 些指令流分别对不同数据流 进行操作 (实际很少用)