CHAPTER 8:MAIN MEMORY

CHAPTER 8: MAIN MEMORY

CHAPTER 8:MEmory mAnagement o Background o Swapping o Contiguous Memory allocation o Paging o Structure of the Page Table o Segmentation o Example:The Intel Pentium

CHAPTER 8: MEMORY MANAGEMENT Background Swapping Contiguous Memory Allocation Paging Structure of the Page Table Segmentation Example: The Intel Pentium

REVIEW o Memory Management ·Partition o fixed o variable ·Paging o http://wenku.baidu.com/course/study/77fldcccda38376ba flfae94#665ea0c7aa00b52acfc7ca94

REVIEW Memory Management Partition fixed variable Paging http://wenku.baidu.com/course/study/77f1dcccda38376ba f1fae94#665ea0c7aa00b52acfc7ca94

PAGING 0 Logical address space of a process can be noncontiguous;process is allocated physical memory whenever the latter is available o Divide physical memory into fixed-sized blocks called frames(size is power of 2,between 512 bytes and 8,192 bytes) o Divide logical memory into blocks of same size called pages o Keep track of all free frames o To run a program of size n pages,need to find n free frames and load program o Set up a page table to translate logical to physical addresses o Internal fragmentation

PAGING Logical address space of a process can be noncontiguous; process is allocated physical memory whenever the latter is available Divide physical memory into fixed-sized blocks called frames (size is power of 2, between 512 bytes and 8,192 bytes) Divide logical memory into blocks of same size called pages Keep track of all free frames To run a program of size n pages, need to find n free frames and load program Set up a page table to translate logical to physical addresses Internal fragmentation

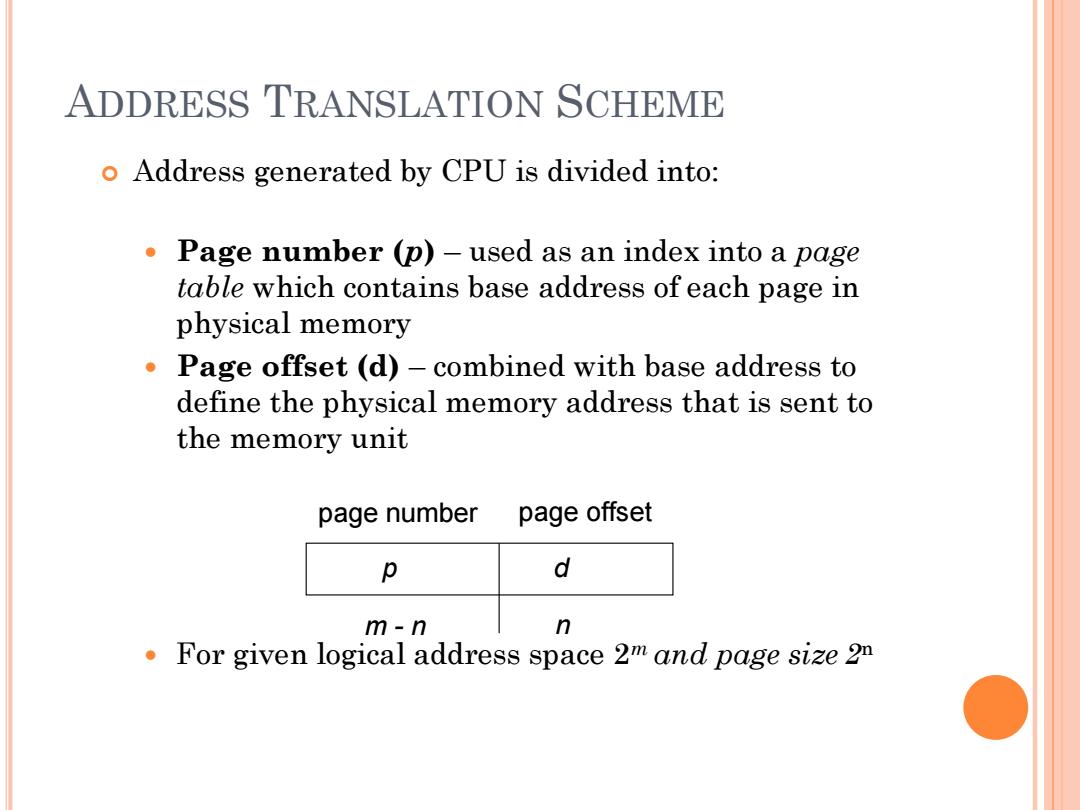

ADDRESS TRANSLATION SCHEME o Address generated by CPU is divided into: Page number (p)-used as an index into a page table which contains base address of each page in physical memory Page offset (d)-combined with base address to define the physical memory address that is sent to the memory unit page number page offset p d m-n n For given logical address space 2m and page size 2n

ADDRESS TRANSLATION SCHEME Address generated by CPU is divided into: Page number (p) – used as an index into a page table which contains base address of each page in physical memory Page offset (d) – combined with base address to define the physical memory address that is sent to the memory unit For given logical address space 2m and page size 2 n page number page offset p d m - n n

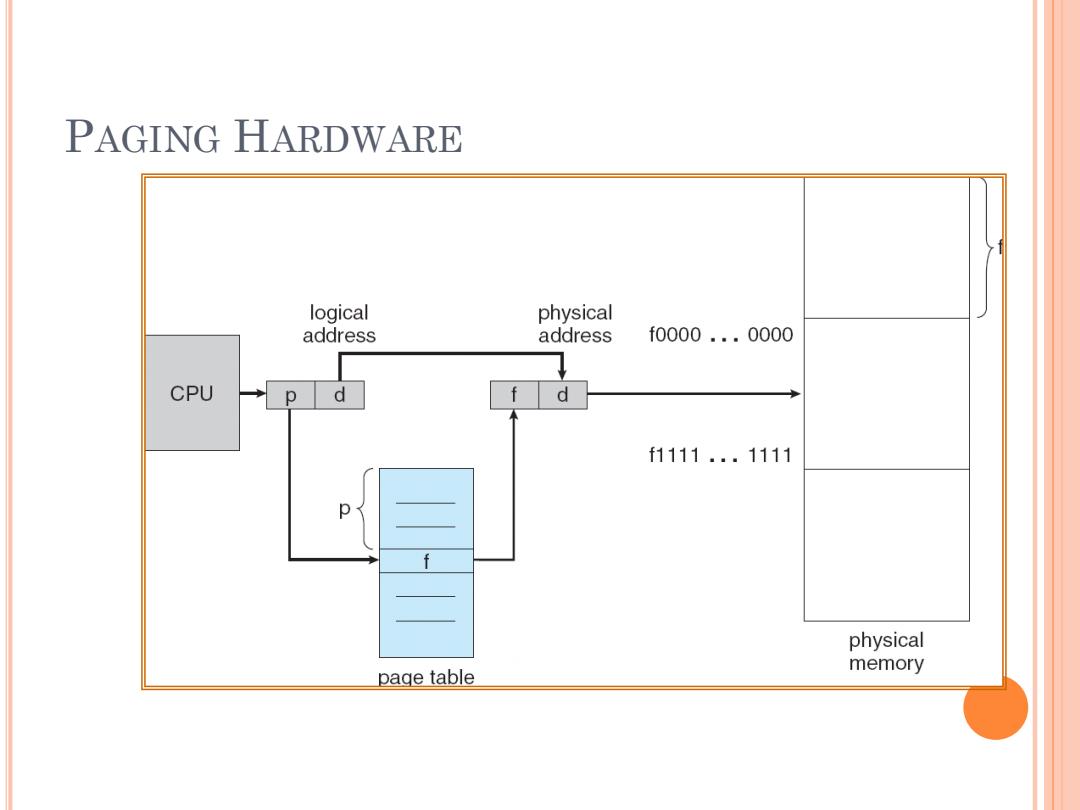

PAGING HARDWARE logical physical address address f0000...0000 CPU p d f d f1111..1111 p physical memory page table

PAGING HARDWARE

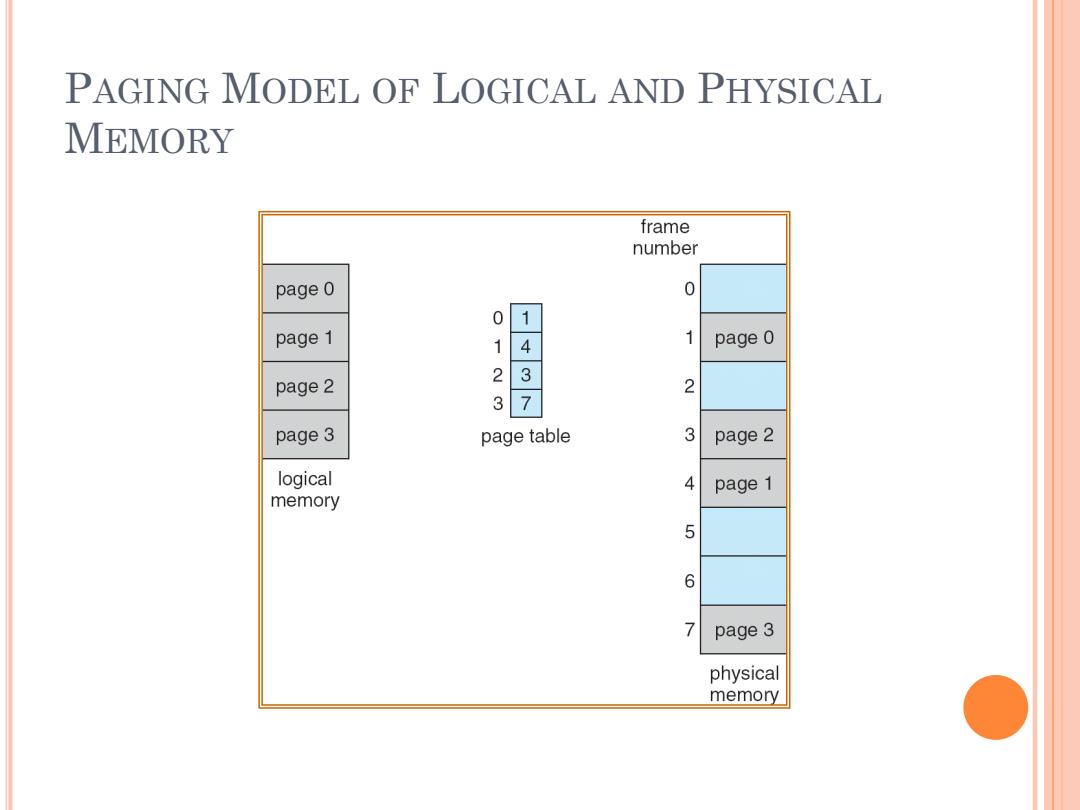

PAGING MODEL OF LOGICAL AND PHYSICAL MEMORY frame number page 0 0 page 1 1 4 1 page 0 page2 2 3 2 3 page 3 page table 3 page 2 logical 4 page 1 memory 5 6 7 page 3 physical memory

PAGING MODEL OF LOGICAL AND PHYSICAL MEMORY

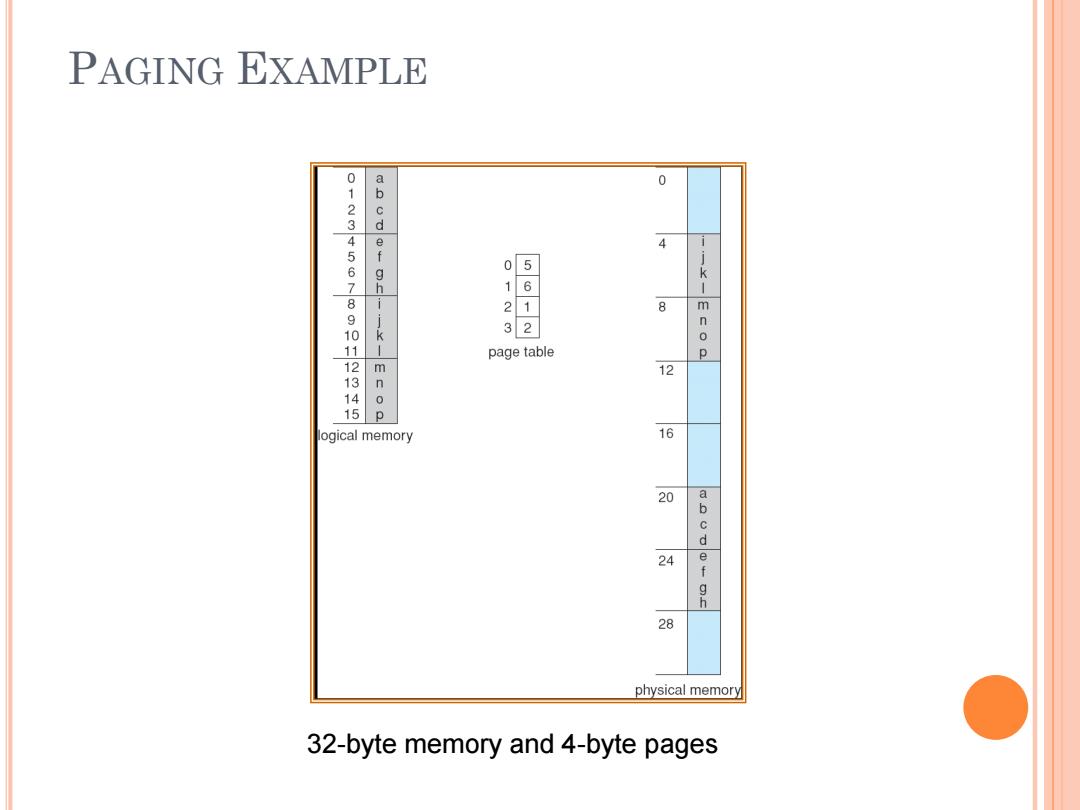

PAGING EXAMPLE 0 01234567 Q O 00-O 01 - 89101 据 8 m -X n page table p 2131415 m 12 n p ogical memory 16 20 24 f 28 physical memory 32-byte memory and 4-byte pages

PAGING EXAMPLE 32-byte memory and 4-byte pages

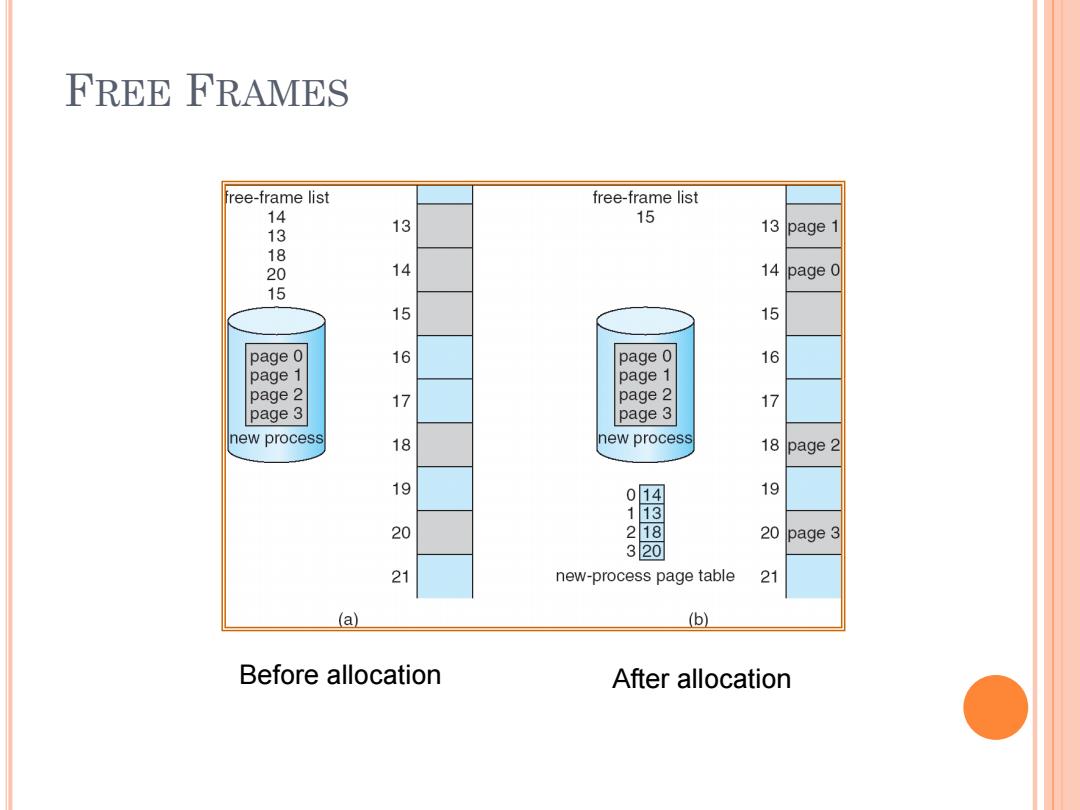

FREE FRAMES free-frame list free-frame list 14 15 13 13 13 page 1 18 14 14 page 0 15 15 15 page 0 16 page 0 16 page 1 page 1 page 2 17 page 2 17 page 3 page 3 new process 18 new process 18 page 2 19 014 19 113 20 218 20 Ipage 3 320 21 new-process page table 21 (a) (b) Before allocation After allocation

FREE FRAMES Before allocation After allocation

IMPLEMENTATION OF PAGE TABLE o Page table is kept in main memory o Page-table base register(PTBR)points to the page table o Page-table length register (PRLR)indicates size of the page table o In this scheme every data/instruction access requires two memory accesses.One for the page table and one for the data/instruction. o The two memory access problem can be solved by the use of a special fast-lookup hardware cache called associative memory or translation look-aside buffers (TLBs) 0 Some TLBs store address-space identifiers (ASIDs)in each TLB entry-uniquely identifies each process to provide address-space protection for that process

IMPLEMENTATION OF PAGE TABLE Page table is kept in main memory Page-table base register (PTBR) points to the page table Page-table length register (PRLR) indicates size of the page table In this scheme every data/instruction access requires two memory accesses. One for the page table and one for the data/instruction. The two memory access problem can be solved by the use of a special fast-lookup hardware cache called associative memory or translation look-aside buffers (TLBs) Some TLBs store address-space identifiers (ASIDs) in each TLB entry – uniquely identifies each process to provide address-space protection for that process