CHAPTER 8:MAIN MEMORY

CHAPTER 8: MAIN MEMORY

CHAPTER 8:MEmory mAnagement o Background o Swapping o Contiguous Memory allocation o Paging o Structure of the Page Table o Segmentation o Example:The Intel Pentium

CHAPTER 8: MEMORY MANAGEMENT Background Swapping Contiguous Memory Allocation Paging Structure of the Page Table Segmentation Example: The Intel Pentium

OBJECTIVES o To provide a detailed description of various ways of organizing memory hardware o To discuss various memory-management techniques,including paging and segmentation oTo provide a detailed description of the Intel Pentium,which supports both pure segmentation and segmentation with paging

OBJECTIVES To provide a detailed description of various ways of organizing memory hardware To discuss various memory-management techniques, including paging and segmentation To provide a detailed description of the Intel Pentium, which supports both pure segmentation and segmentation with paging

BACKGROUND o Program must be brought(from disk)into memory and placed within a process for it to be run o Main memory and registers are only storage CPU can access directly o Register access in one CPU clock (or less) o Main memory can take many cycles o Cache sits between main memory and CPU registers o Protection of memory required to ensure correct operation

BACKGROUND Program must be brought (from disk) into memory and placed within a process for it to be run Main memory and registers are only storage CPU can access directly Register access in one CPU clock (or less) Main memory can take many cycles Cache sits between main memory and CPU registers Protection of memory required to ensure correct operation

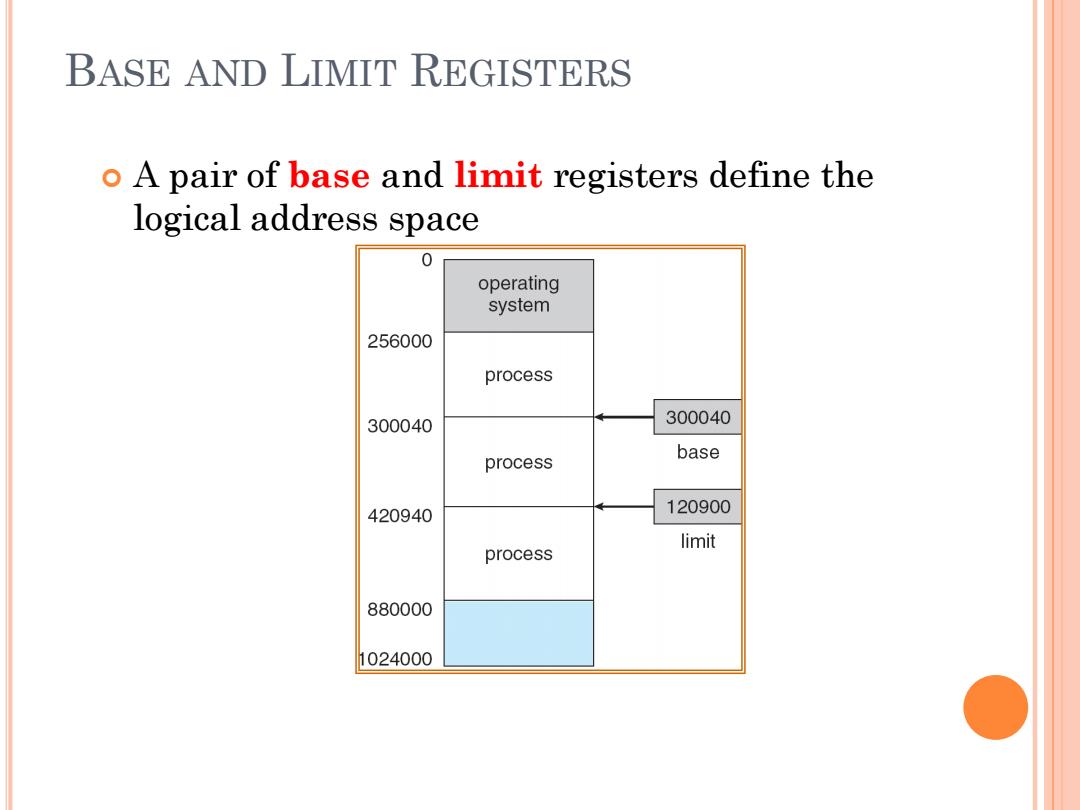

BASE AND LIMIT REGISTERS o A pair of base and limit registers define the logical address space 0 operating system 256000 process 300040 300040 base process 420940 120900 limit process 880000 1024000

BASE AND LIMIT REGISTERS A pair of base and limit registers define the logical address space

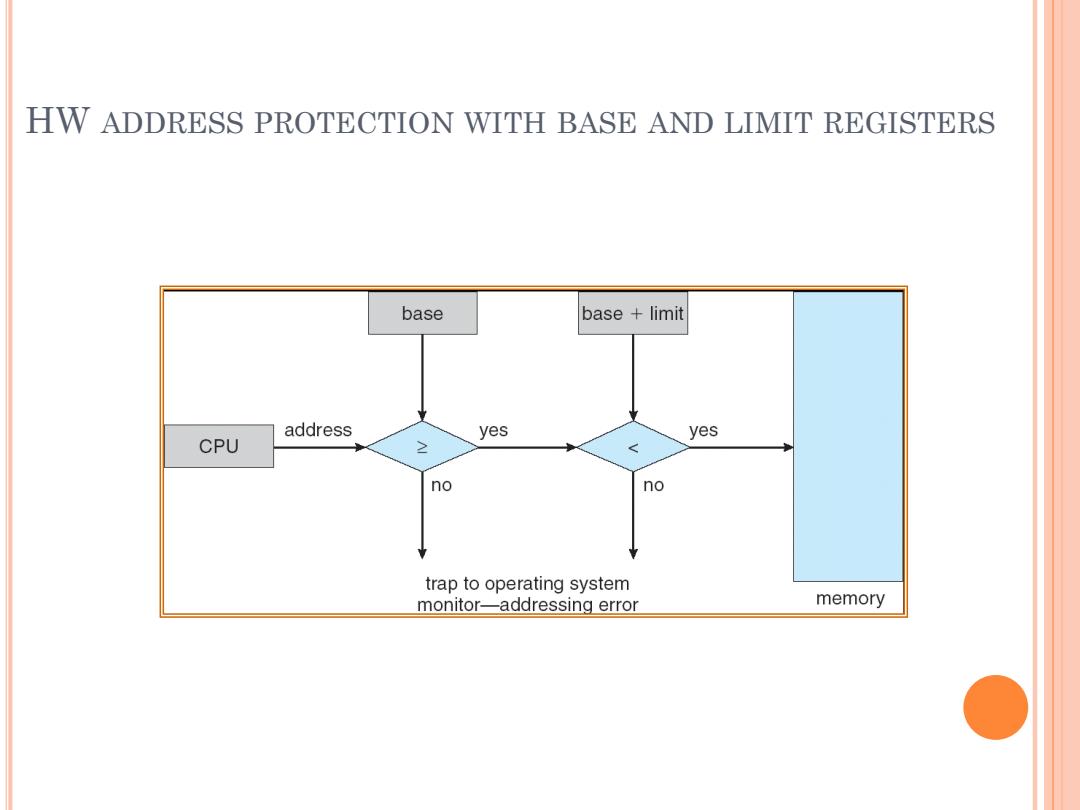

HW ADDRESS PROTECTION WITH BASE AND LIMIT REGISTERS base base limit address yes yes CPU no no trap to operating system monitor-addressing error memory

HW ADDRESS PROTECTION WITH BASE AND LIMIT REGISTERS

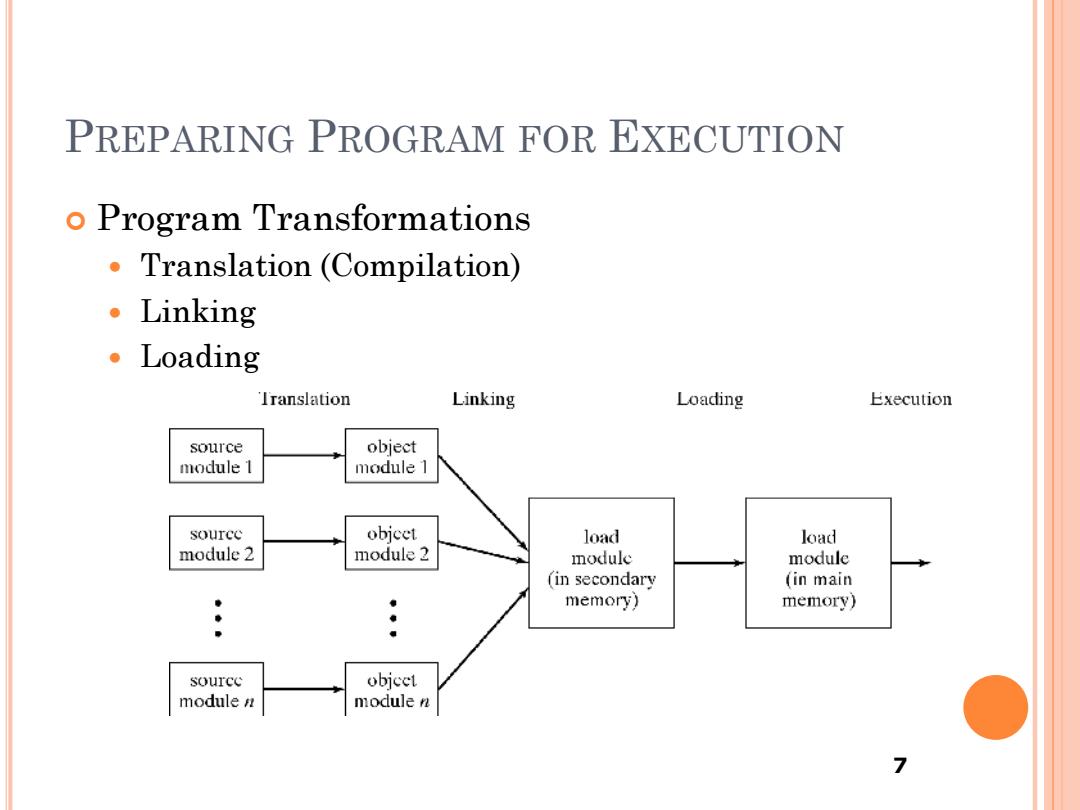

PREPARING PROGRAM FOR EXECUTION o Program Transformations Translation (Compilation) Linking 。Loading Iranslation Linking Loading Execution source object module 1 module 1 source objcet load load module 2 module 2 module module (in secondary (in main memory) memory) source objcet module n module n 7

PREPARING PROGRAM FOR EXECUTION Program Transformations Translation (Compilation) Linking Loading 7

PROGRAM TRANSFORMATIONS o Translation source written in symbolic programming language conversion of symbolic instructions into machine specific form o Linking complex systems made up by multiple modules resolving of external references to other modules conversion from logical addresses to physical memory locations o Loading transfer of code from disk to main memory 8

PROGRAM TRANSFORMATIONS Translation source written in symbolic programming language conversion of symbolic instructions into machine specific form Linking complex systems made up by multiple modules resolving of external references to other modules conversion from logical addresses to physical memory locations Loading transfer of code from disk to main memory 8

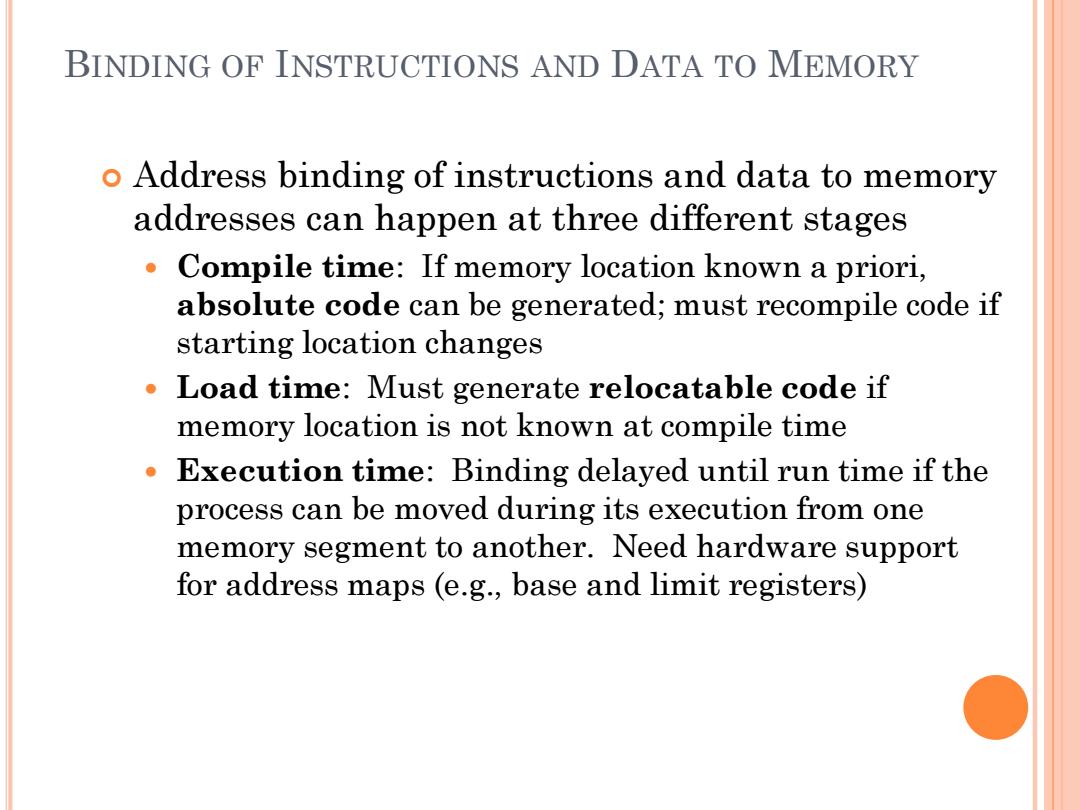

BINDING OF INSTRUCTIONS AND DATA TO MEMORY o Address binding of instructions and data to memory addresses can happen at three different stages 0 Compile time:If memory location known a priori, absolute code can be generated;must recompile code if starting location changes Load time:Must generate relocatable code if memory location is not known at compile time Execution time:Binding delayed until run time if the process can be moved during its execution from one memory segment to another.Need hardware support for address maps (e.g.,base and limit registers)

BINDING OF INSTRUCTIONS AND DATA TO MEMORY Address binding of instructions and data to memory addresses can happen at three different stages Compile time: If memory location known a priori, absolute code can be generated; must recompile code if starting location changes Load time: Must generate relocatable code if memory location is not known at compile time Execution time: Binding delayed until run time if the process can be moved during its execution from one memory segment to another. Need hardware support for address maps (e.g., base and limit registers)

MULTISTEP PROCESSING OF A USER PROGRAM source program compiler or compile assembler time object module other object modules linkage editor load load module time system library loader dynamically loaded system library in-memory binary executio dynamic linking time (run memory image time)

MULTISTEP PROCESSING OF A USER PROGRAM