第六章内存储器接口 ©知迟概述⑨ 第一节 内存储器件 第二节 地址译码 第三节 内存储器扩展技术 第四节 16位、32位及64位机存储器系统 不计算缺 退出

第六章 内存储器接口 第四节 16位、32位及64位机存储器系统 退 出 第一节 内存储器件 ☺ 知 识 概 述 ☺ 第二节 地址译码 第三节 内存储器扩展技术

第一节 内存储器件 6.1.1 内存储器概述 1.存储器有两种基本操作一读和写。 2.所有的存储芯片都设有地址引脚、数据引脚、读、写 控制脚及片选脚。 染讲算缺 退出

第一节 内存储器件 6.1.1 内存储器概述 退 出 1.存储器有两种基本操作—读和写。 2. 所有的存储芯片都设有地址引脚、数据引脚、读、写 控制脚及片选脚

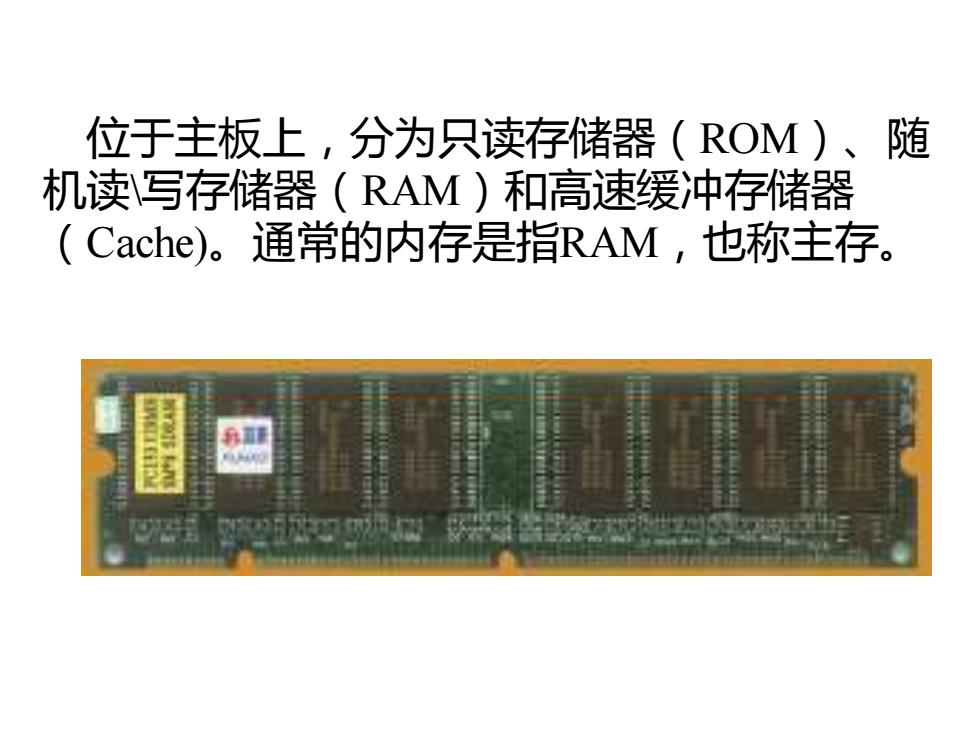

位于主板上,分为只读存储器(ROM)、随 机读写存储器(RAM)和高速缓冲存储器 (Cache)。通常的内存是指RAM,也称主存

内存储器 位于主板上,分为只读存储器(ROM)、随 机读\写存储器(RAM)和高速缓冲存储器 (Cache)。通常的内存是指RAM,也称主存

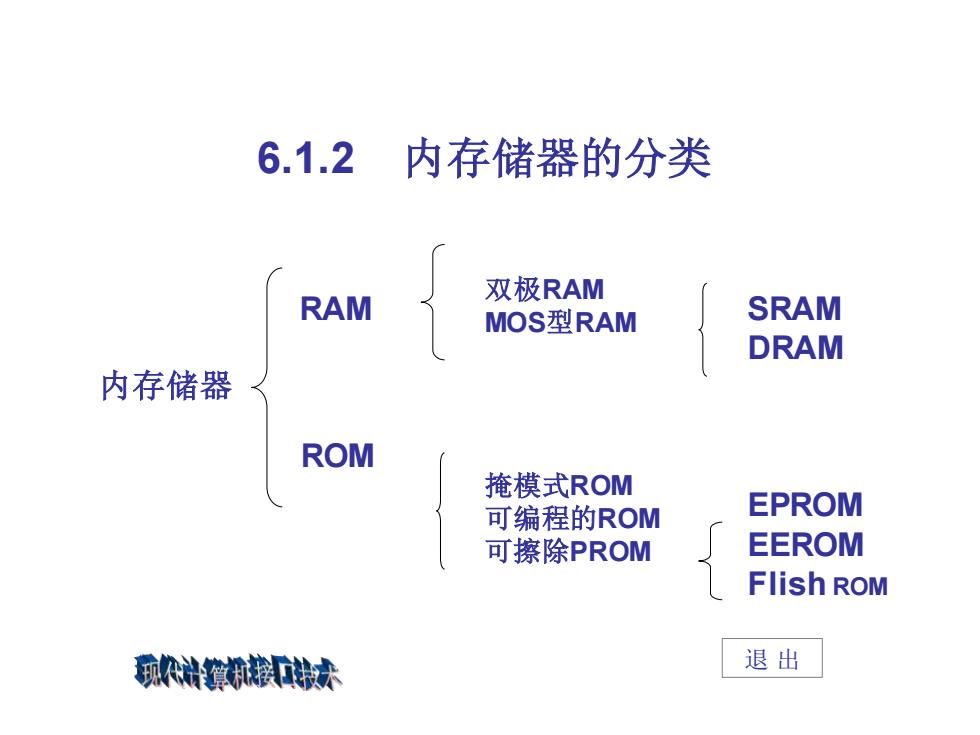

6.1.2 内存储器的分类 RAM 双极RAM MOS型RAM SRAM DRAM 内存储器 ROM 掩模式ROM 可编程的ROM EPROM 可擦除PROM EEROM Flish ROM 计算接式 退出

6.1.2 内存储器的分类 退 出 内存储器 RAM 双极RAM MOS型RAM 掩模式ROM 可编程的ROM 可擦除PROM ROM SRAM DRAM EPROM EEROM Flish ROM

一、随机存取存储器RAM 1.双极型RAM 双极型RAM的主要特点: 存取时间短,通常为几纳秒到几十纳秒: 其集成度低、功耗大,而且价格也较高。 2.MOS型RAM 用MOS器件构成的RAM又可分为SRAM和DRAM. 现不计算接缺 退出 6.1.2

6.1.2 一、随机存取存储器RAM 1. 双极型RAM 双极型RAM的主要特点: 存取时间短,通常为几纳秒到几十纳秒; 其集成度低、功耗大,而且价格也较高。 2. MOS型RAM 用MOS器件构成的RAM又可分为SRAM和DRAM。 退 出

二、只读存储器ROM 1.掩模式只读存储器ROM 这种芯片存储的信息稳定,成本最低。适用于存放一 些可批量生产的固定不变的程序或数据。 2.可一次编程ROM,PROM 用户可以一次写入,但再也无法改变它的内容。 3.可擦除的ROM 可擦除的PROM芯片因其擦除的方式不同可分为三类。 (1)一是通过是紫外线照射来擦除,这种用紫外线擦除 的PROM称为EPROM (2)另外一种是通过电的方法来擦除,这种PROM称为 EEPROM芯片内容擦除后仍可以重新对它进行编程,写 入新的内容。擦除和重新编程都可以多次进行。 (3)快速擦除,快闪flash ROM 染计算接款 退出 61.2

6.1.2 二、只读存储器ROM 1. 掩模式只读存储器 ROM 这种芯片存储的信息稳定,成本最低。适用于存放一 些可批量生产的固定不变的程序或数据。 2. 可一次编程ROM, PROM 用户可以一次写入,但再也无法改变它的内容。 3. 可擦除的ROM 可擦除的PROM芯片因其擦除的方式不同可分为三类。 (1)一是通过是紫外线照射来擦除,这种用紫外线擦除 的PROM称为EPROM (2)另外一种是通过电的方法来擦除,这种PROM称为 EEPROM芯片内容擦除后仍可以重新对它进行编程,写 入新的内容。擦除和重新编程都可以多次进行。 (3)快速擦除,快闪flash ROM 退 出

6.1.3存储器芯片的主要技术指标 1.存储容量 存储器芯片的存储容量用“存储单元个数×每存储单 元的位数”来表示。当计算机的内存确定后,、选用容量大 的芯片则可以少用几片,这样不仅使电路连接简单,而且 功耗也可以降低。 2.存取时间和存取周期 存取时间又称存储器访问时间,即启动一次存储器操 作(读或写)到完成该操作所需要的时间。CPU在读写存 储器时,其读写时间必须大于存储器芯片的额定存取时间。 如果不能满足这一点,微型机则无法正常工作。 存取周期是连续启动两次独立的存储器操作所需间隔 的最小时间。若令存取时间为A,存取周期为TC,则 者的关系为TC≥tA。 染计算来 退出

6.1.3 存储器芯片的主要技术指标 1. 存储容量 存储器芯片的存储容量用“存储单元个数×每存储单 元的位数”来表示。当计算机的内存确定后,选用容量大 的芯片则可以少用几片,这样不仅使电路连接简单,而且 功耗也可以降低。 2. 存取时间和存取周期 存取时间又称存储器访问时间,即启动一次存储器操 作(读或写)到完成该操作所需要的时间。CPU在读写存 储器时,其读写时间必须大于存储器芯片的额定存取时间。 如果不能满足这一点,微型机则无法正常工作。 存取周期是连续启动两次独立的存储器操作所需间隔 的最小时间。若令存取时间为tA,存取周期为TC,则二 者的关系为TC≥tA。 退 出

3.可靠性 目前所用的半导体存储器芯片的平均故障间隔时间约 为5×1061×108小时左右。 4.功耗 使用功耗低的存储器芯片构成存储系统,不仅可以减 少对电源容量的要求,而且还可以提高存储系统的可靠性。 朵清算接款 退出 6.1.3

6.1.3 3. 可靠性 目前所用的半导体存储器芯片的平均故障间隔时间约 为5×l06~l×108小时左右。 4. 功耗 使用功耗低的存储器芯片构成存储系统,不仅可以减 少对电源容量的要求,而且还可以提高存储系统的可靠性。 退 出

6.1.4随机存取存储器的存储元及外部特性 一、静态存储器 1.SRAM的存储元 静态RAM的基本存储电路(即存储元)一般是由6个 MOS管组成的双稳态电路,如图6.1所示。 2.SRAM的外部特性 6264芯片是一个8K×8bit的CMOS SRAM:芯片,其引 脚如图6.2所示。 A0A2:13根地址信号线。一个存储芯片上地址线的 多少决定了该芯片有多少个存储单元。通常这13根地址线 通常接到系统地址总线的低13位上,以便CPU能够寻址 芯片上的各个单元。 现计式 退出

6.1.4 随机存取存储器的存储元及外部特性 一、静态存储器 1. SRAM的存储元 静态RAM的基本存储电路(即存储元)一般是由6个 MOS管组成的双稳态电路,如图6.1所示。 2. SRAM的外部特性 6264芯片是一个8K×8bit的CMOS SRAM芯片,其引 脚如图6.2所示。 A0~Al2:13根地址信号线。一个存储芯片上地址线的 多少决定了该芯片有多少个存储单元。通常这13根地址线 通常接到系统地址总线的低13位上,以便CPU能够寻址 芯片上的各个单元。 退 出

D0~D7:8根双向数据线。对SRAM芯片来讲,数据线 的根数决定了芯片上每个存储单元的二进制位数。使用时, 这8根数据线与系统的数据总线相连。 CS1、CS2:片选信号线。 OE:输出允许信号。只有当为低电平时,CPU才能 够从芯片中读出数据,通常与系统总线的MEN相连。 WE:写允许信号。当WE为低电平时,允许数据写入 芯片,通常与系统总线的MEMW相连。 其它引脚:Vcc为+5V电源,GND是接地端,NC表示 空端。 染计算来 退出 6.1.4

6.1.4 D0~D7:8根双向数据线。对SRAM芯片来讲,数据线 的根数决定了芯片上每个存储单元的二进制位数。使用时, 这8根数据线与系统的数据总线相连。 CS1 、CS2:片选信号线。 OE:输出允许信号。只有当为低电平时,CPU才能 够从芯片中读出数据,通常与系统总线的MEMW相连。 WE:写允许信号。当WE为低电平时,允许数据写入 芯片,通常与系统总线的MEMW相连。 其它引脚:Vcc为+5V电源,GND是接地端,NC表示 空端。 退 出