并行处理技术(计算机系) 分布式与并行计算(人工智能学院) 课程介绍 任课教师:谢磊 教授、博士生导师

并行处理技术(计算机系) 分布式与并行计算(人工智能学院) 课程介绍 任课教师:谢磊 教授、博士生导师

主要内容: 一、课程简介 二、课程的定位与目标 三、课程的结构与内容 四、课程的教学形式 五、课程的考核形式 六、课程的参考书籍

一、课程简介 三、课程的结构与内容 主要内容: 二、课程的定位与目标 五、课程的考核形式 六、课程的参考书籍 四、课程的教学形式

课程简介-为何需要并行计算? How to run applications faster?

课程简介-为何需要并行计算? How to run applications faster?

课程简介-How to run applications faster? Three ways to improve performance -Work Harder -Work Smarter -Get Help

课程简介- How to run applications faster? • Three ways to improve performance – Work Harder – Work Smarter – Get Help

课程简介-Computer Analogy Faster hardware Optimized algorithms and Techniques Multiple computers to solve problem

课程简介- Computer Analogy • Faster hardware • Optimized algorithms and Techniques • Multiple computers to solve problem

课程简介-经典的并发模型:Pipeline(1) 组装

课程简介-经典的并发模型:Pipeline (1)

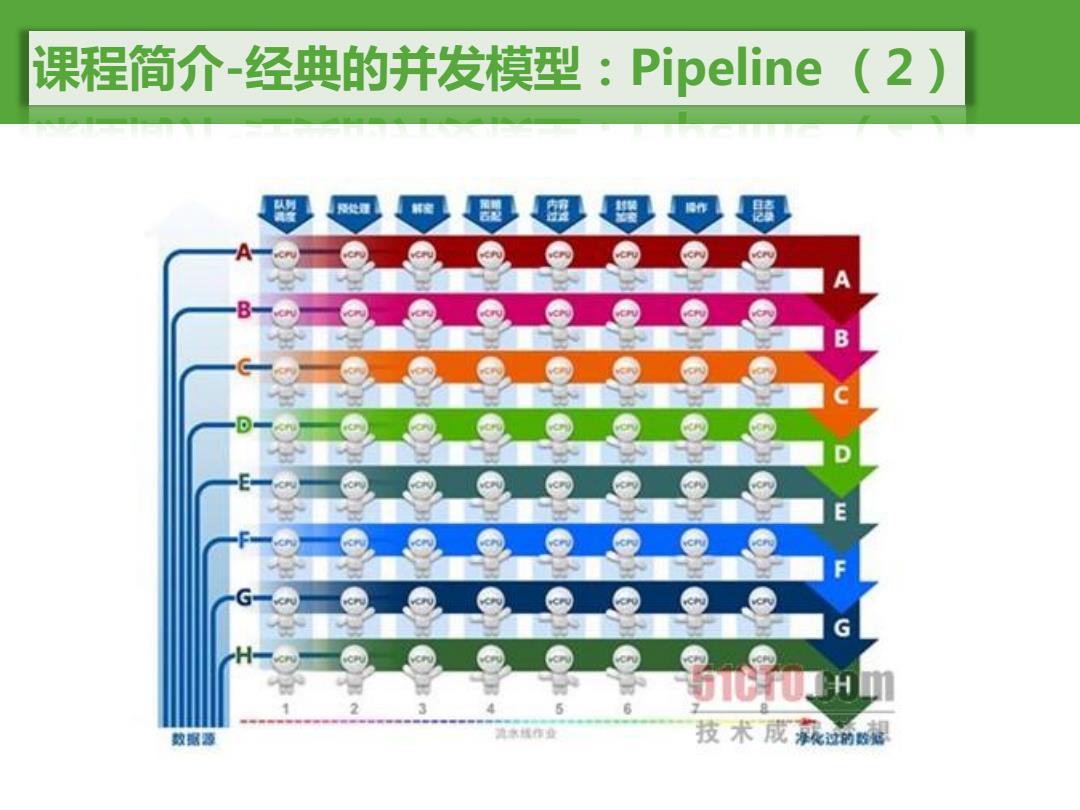

课程简介-经典的并发模型:Pipeline(2) 博n B 8 E G 数据源 汽来域作鱼 技术成就过的想

课程简介-经典的并发模型:Pipeline (2)

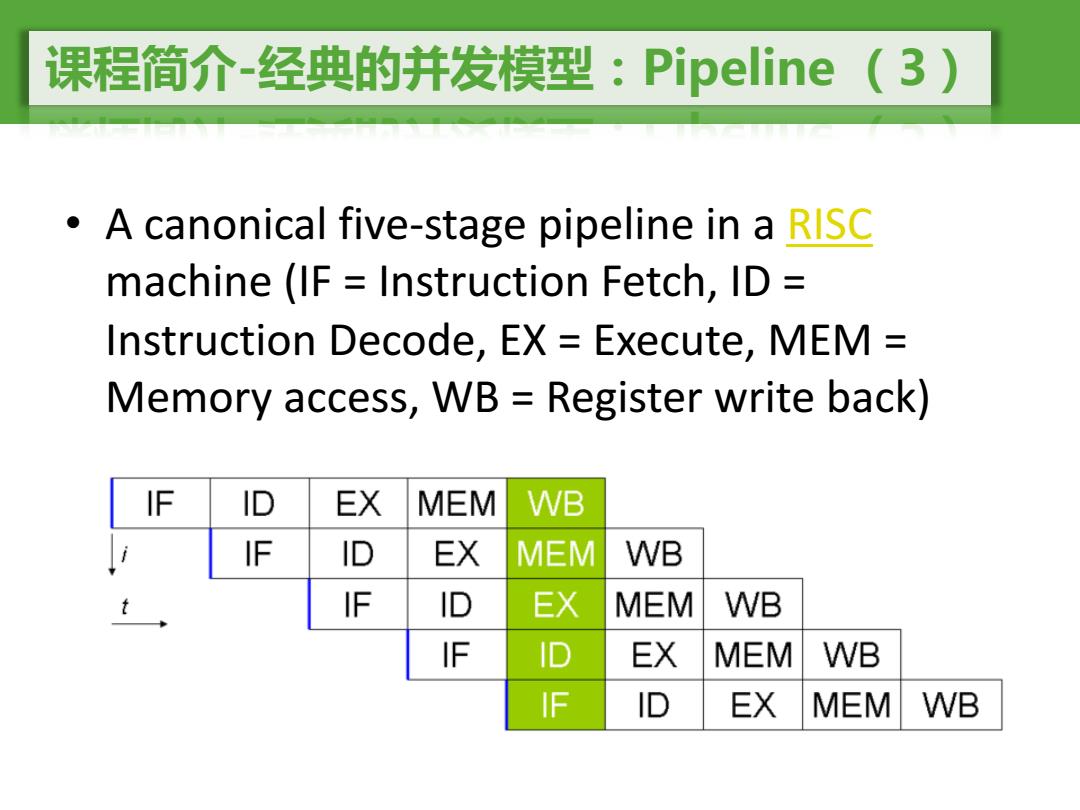

课程简介-经典的并发模型:Pipeline(3)》 A canonical five-stage pipeline in a RISC machine (IF Instruction Fetch,ID Instruction Decode,EX Execute,MEM Memory access,WB Register write back) IF ID EX MEM WB IF ID EX MEM WB IF ID EX MEM WB IF ID EX MEM WB IF ID EX MEM WB

课程简介-经典的并发模型:Pipeline (3) • A canonical five-stage pipeline in a RISC machine (IF = Instruction Fetch, ID = Instruction Decode, EX = Execute, MEM = Memory access, WB = Register write back)

课程简介-经典的并发模型:Pipeline(4) A five-stage pipelined superscalar processor, capable of issuing two instructions per cycle.It can have two instructions in each stage of the pipeline,for a total of up to 10 instructions (shown in green)being simultaneously executed

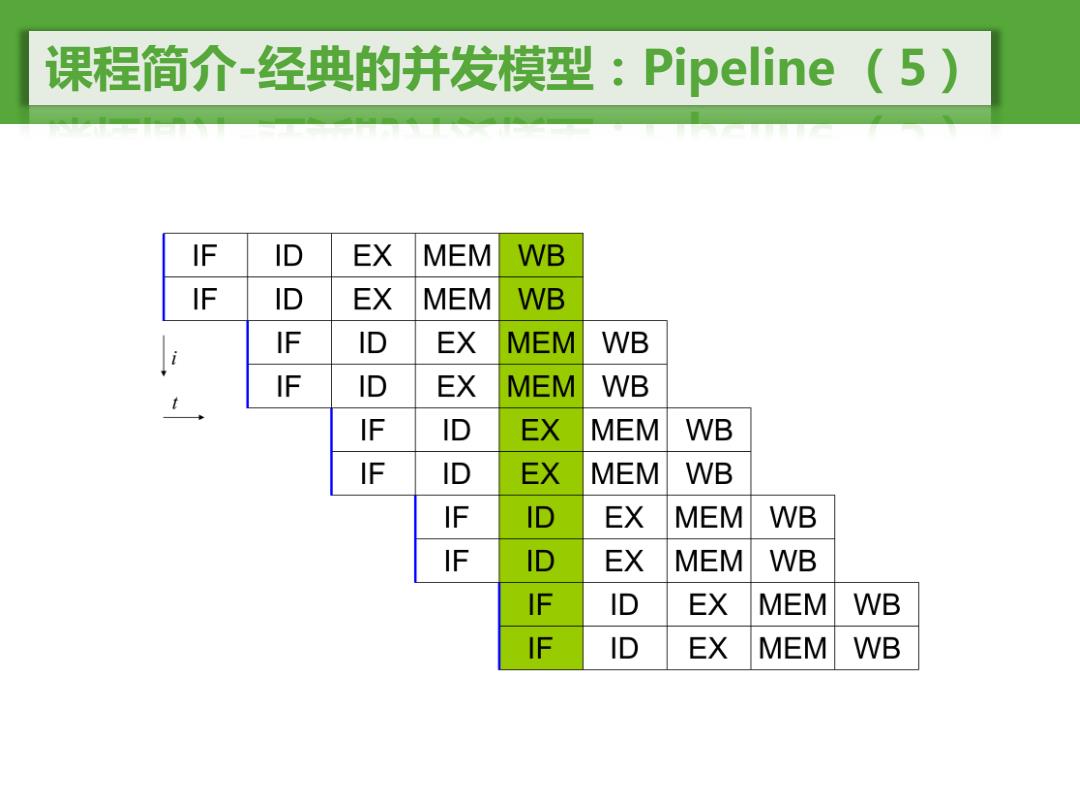

课程简介-经典的并发模型:Pipeline (4) • A five-stage pipelined superscalar processor, capable of issuing two instructions per cycle. It can have two instructions in each stage of the pipeline, for a total of up to 10 instructions (shown in green) being simultaneously executed

课程简介-经典的并发模型:Pipeline(5) IF ID EX MEM WB IF ID EX MEM WB IF ID EX MEM WB IF ID EX MEM WB IF ID EX MEM WB IF ID EX MEM WB IF ID EX MEM WB IF ID EX MEM WB IF ID EX MEM WB IF ID EX MEM WB

课程简介-经典的并发模型:Pipeline (5)