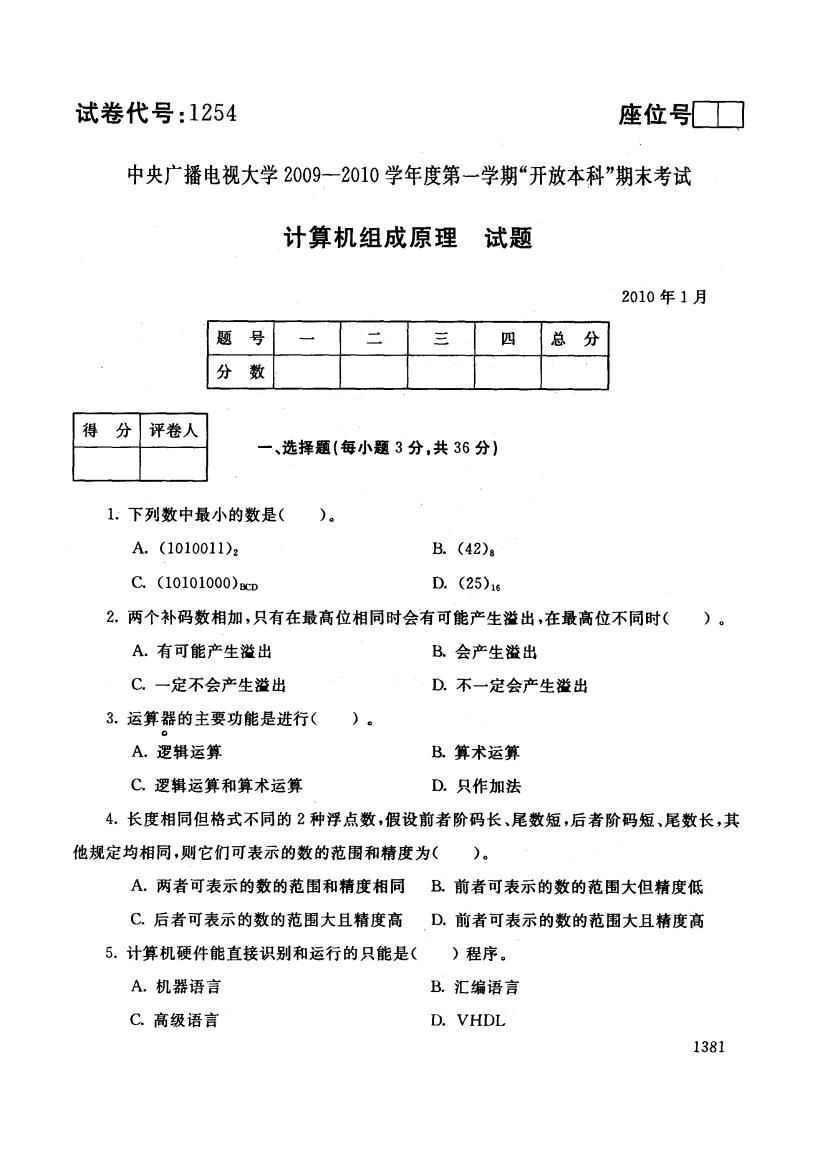

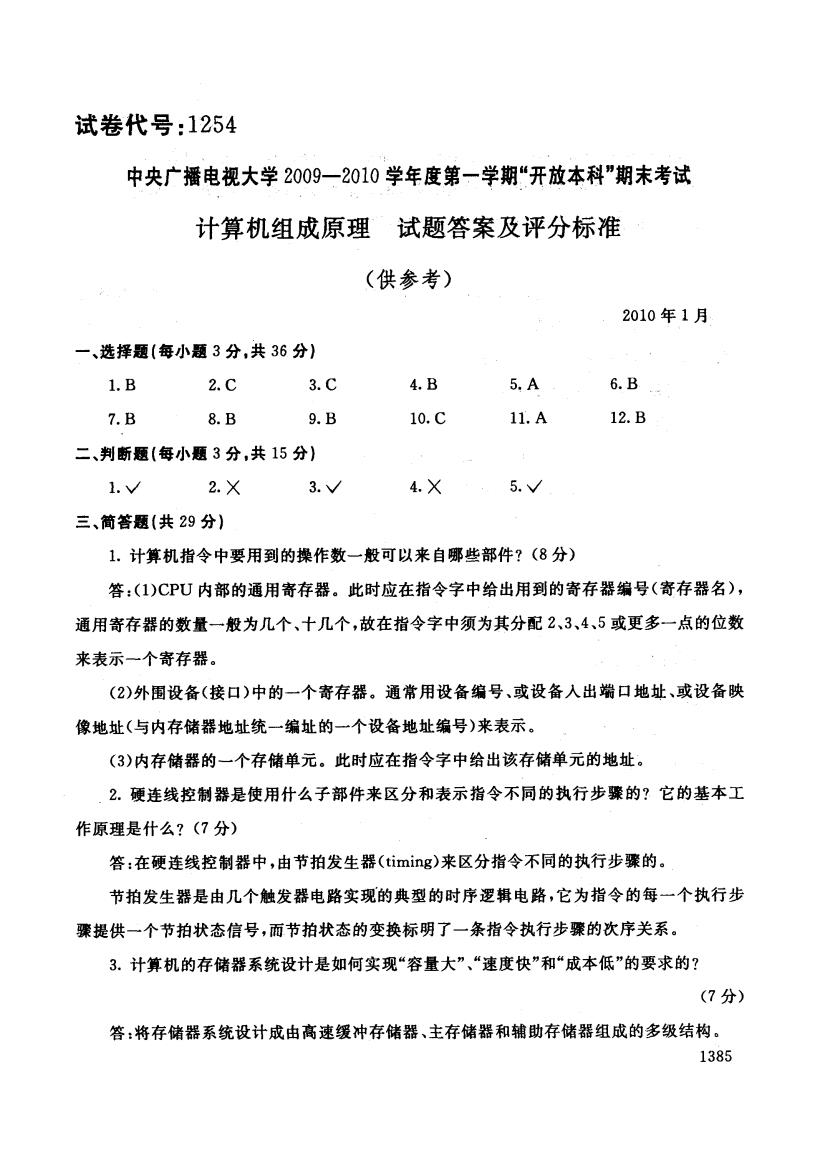

试卷代号:1254 座位■■ 中央广播电视大学2009一2010学年度第一学期“开放本科”期末考试 计算机组成原理 试题 2010年1月 题 号 三 四 总 分 分 数 得分 评卷人 一、选择题(每小题3分,共36分) 1.下列数中最小的数是( A.(1010011)2 B.(42)8 C.(10101000)cD D.(25)16 2.两个补码数相加,只有在最高位相同时会有可能产生滋出,在最高位不同时()。 A.有可能产生溢出 B.会产生溢出 C.一定不会产生溢出 D.不一定会产生滋出 3.运算器的主要功能是进行( 。 A.逻辑运算 B.算术运算 C.逻辑运算和算术运算 D.只作加法 4.长度相同但格式不同的2种浮点数,假设前者阶码长、尾数短,后者阶码短、尾数长,其 他规定均相同,则它们可表示的数的范围和精度为()。 A.两者可表示的数的范围和精度相同B.前者可表示的数的范围大但精度低 C.后者可表示的数的范围大且精度高D.前者可表示的数的范围大且精度高 5.计算机硬件能直接识别和运行的只能是( )程序。 A.机器语言 B.汇编语言 C.高级语言 D.VHDL 1381

试卷代号:1254 座位号巨二」 中央广播电视大学2009-2010学年度第一学期“开放本科”期末考试 计算机组成原理 试题 2010年 1月 题 号 四 总 分 分 数 得 分 评卷人 一、选择题《每小题 3分,共 36分) 1.下列数中最小的数是( )。 A. (1010011)2 B. (42)6 C. (10101000)BCD D. (25),6 2.两个补码数相加,只有在最高位相同时会有可能产生滋出,在最高位不同时( A.有可能产生滋出 B.会产生滋出 C.一定不会产生滋出 D.不一定会产生滋出 3.运算器的主要功能是进行( )。 A.逻辑运算 B.算术运算 C.逻辑运算和算术运算 D.只作加法 4.长度相同但格式不同的 2种浮点数,假设前者阶码长、尾数短,后者阶码短、尾数长,其 他规定均相同,则它们可表示的数的范围和精度为( )。 A.两者可表示的数的范围和精度相同 B.前者可表示的数的范围大但精度低 C.后者可表示的数的范围大且精度高 D.前者可表示的数的范围大且精度高 5.计算机硬件能直接识别和运行的只能是( )程序。 A.机器语言 B.汇编语言 C.高级语言 D. VHDL 1381

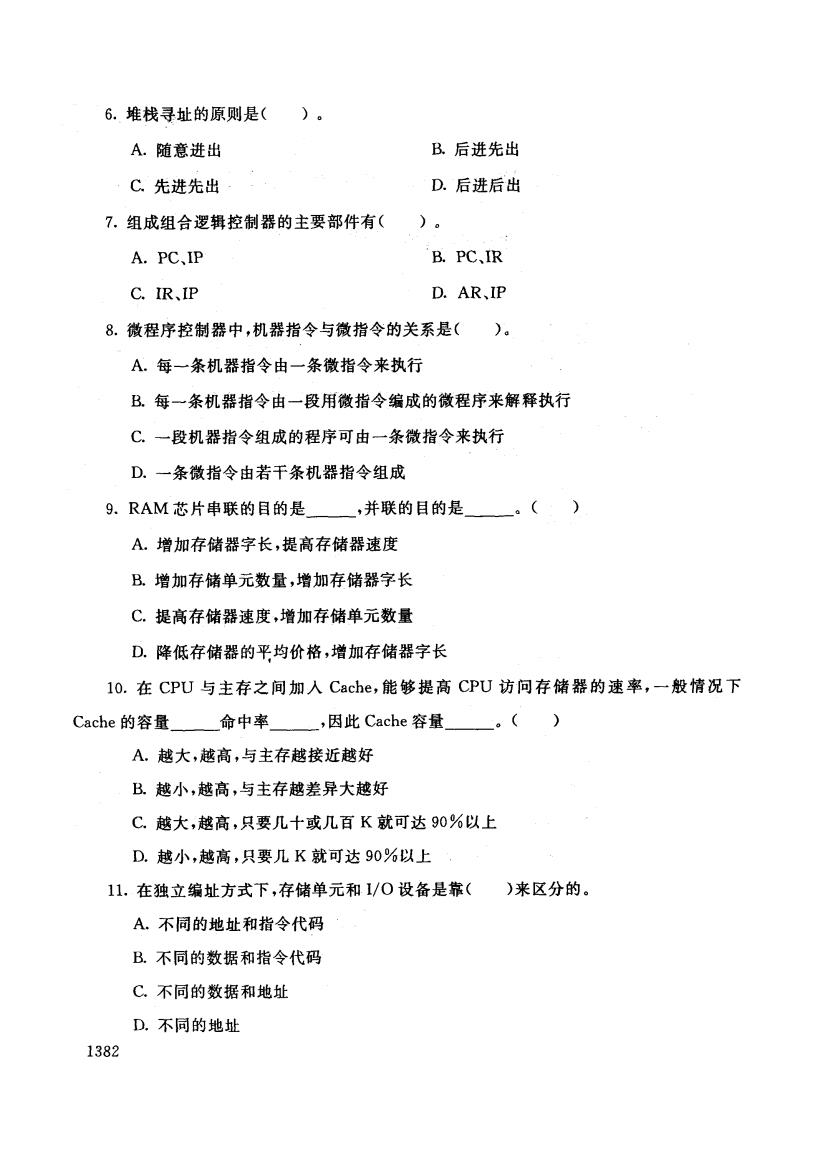

6.堆栈寻址的原则是()。 A.随意进出 B.后进先出 C.先进先出 D.后进后出 7.组成组合逻辑控制器的主要部件有()。 A.PC、IP B.PC、IR C.IR、IP D.AR、IP 8.微程序控制器中,机器指令与微指令的关系是()。 A.每一条机器指令由一条微指令来执行 B.每一条机器指令由一段用微指令编成的微程序来解释执行 C.一段机器指令组成的程序可由一条微指令来执行 D.一条微指令由若干条机器指令组成 9.RAM芯片串联的目的是,并联的目的是 。(· ) A.增加存储器字长,提高存储器速度 B.增加存储单元数量,增加存储器字长 C.提高存储器速度,增加存储单元数量 D.降低存储器的平均价格,增加存储器字长 10.在CPU与主存之间加人Cache,能够提高CPU访问存储器的速率,一般情况下 Cache的容量命中率,因此Cache容量 _。() A.越大,越高,与主存越接近越好 B.越小,越高,与主存越差异大越好 C.越大,越高,只要几十或几百K就可达90%以上 D.越小,越高,只要几K就可达90%以上 11.在独立编址方式下,存储单元和1/0设备是靠( )来区分的。 A.不同的地址和指令代码 B.不同的数据和指令代码 C.不同的数据和地址 D.不同的地址 1382

6.堆栈寻址的原则是( )。 A.随意进出 B.后进先出 C.先进先出 D.后进后出 7.组成组合逻辑控制器的主要部件有( )。 A. PC, IP B. PC,IR C. IR,IP D. AR, IP 8.微程序控制器中,机器指令与微指令的关系是( >a A.每一条机器指令由一条微指令来执行 B.每一条机器指令由一段用微指令编成的微程序来解释执行 C.一段机器指令组成的程序可由一条微指令来执行 D.一条微指令由若干条机器指令组成 9. RAM芯片串联的目的是_ ,并联的目的是_ 。( ) A.增加存储器字长,提高存储器速度 B.增加存储单元数量,增加存储器字长 C.提高存储器速度,增加存储单元数量 D.降低存储器的平均价格,增加存储器字长 10.在 CPU与主存之间加人 Cache,能够提高 CPU 访问存储器的速率,一般情况下 Cache的容量— 命中率_ ,因此Cache容量_ 。( ) A.越大,越高,与主存越接近越好 B.越小,越高,与主存越差异大越好 C,越大,越高,只要几十或几百 K就可达 90 以上 D.越小,越高,只要几 K就可达 90%以上 11.在独立编址方式下,存储单元和 I/O设备是靠( )来区分的。 A.不同的地址和指令代码 B.不同的数据和指令代码 C.不同的数据和地址 D.不同的地址 1382

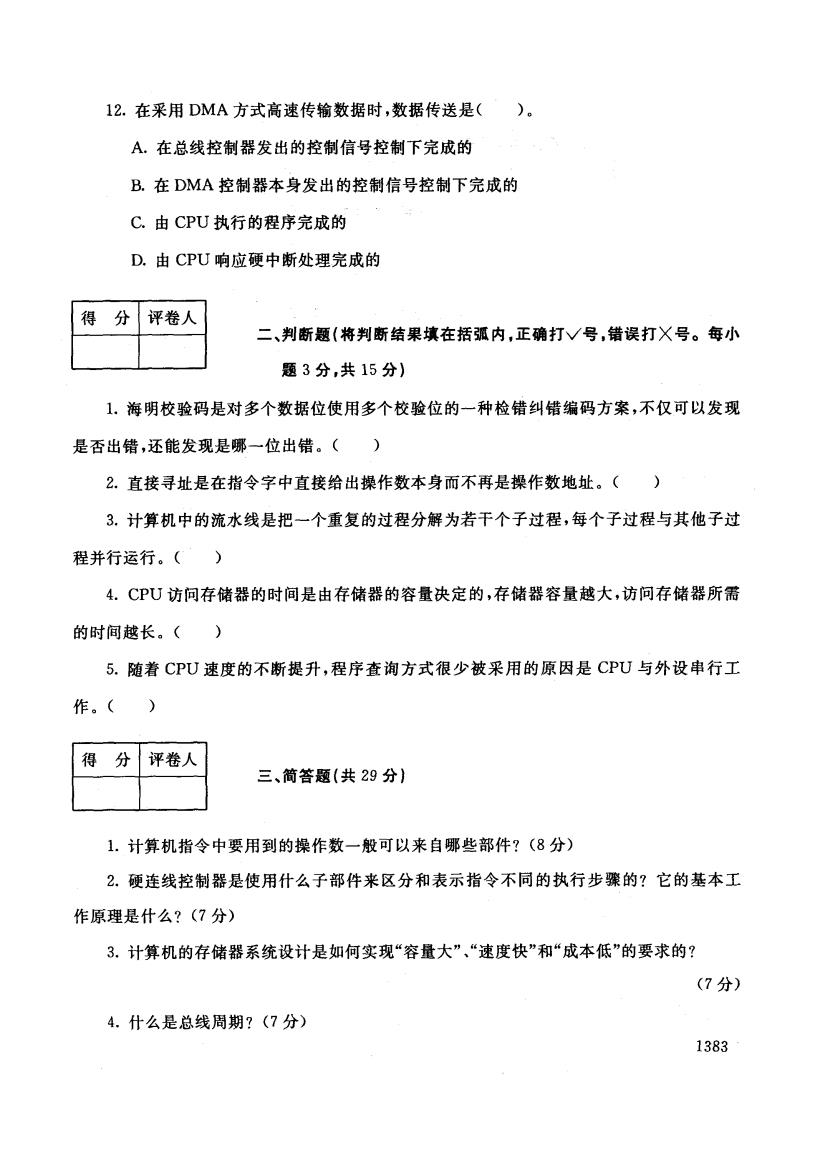

12.在采用DMA方式高速传输数据时,数据传送是( A.在总线控制器发出的控制信号控制下完成的 B.在DMA控制器本身发出的控制信号控制下完成的 C.由CPU执行的程序完成的 D.由CPU响应硬中断处理完成的 得 分 评卷人 二、判断题(将判断结果填在括弧内,正确打√号,错误打X号。每小 题3分,共15分) 1.海明校验码是对多个数据位使用多个校验位的一种检错纠错编码方案,不仅可以发现 是否出错,还能发现是哪一位出错。() 2.直接寻址是在指令字中直接给出操作数本身而不再是操作数地址。() 3.计算机中的流水线是把一个重复的过程分解为若干个子过程,每个子过程与其他子过 程并行运行。() 4.CPU访问存储器的时间是由存储器的容量决定的,存储器容量越大,访问存储器所需 的时间越长。() 5.随着CPU速度的不断提升,程序查询方式很少被采用的原因是CPU与外设串行工 作。( ) 得 分 评卷人 三、简答题(共29分) 1.计算机指令中要用到的操作数一般可以来自哪些部件?(8分) 2.硬连线控制器是使用什么子部件来区分和表示指令不同的执行步骤的?它的基本工 作原理是什么?(7分) 3.计算机的存储器系统设计是如何实现“容量大”、“速度快”和“成本低”的要求的? (7分) 4.什么是总线周期?(7分) 1383

12.在采用 DMA方式高速传输数据时,数据传送是( A.在总线控制器发出的控制信号控制下完成的 B.在DMA控制器本身发出的控制信号控制下完成的 C.由CPU执行的程序完成的 D.由CPU响应硬中断处理完成的 得 分 评卷人 二、判断题 (将判断结果填在括弧内.正确打v号 ,错误打X号。每小 题 3分,共 15分) 1.海明校验码是对多个数据位使用多个校验位的一种检错纠错编码方案,不仅可以发现 是否出错,还能发现是哪一位出错。 2.直接寻址是在指令字中直接给出操作数本身而不再是操作数地址。( ) 3.计算机中的流水线是把一个重复的过程分解为若干个子过程,每个子过程与其他子过 程并行运行 。 4. CPU访问存储器的时间是由存储器的容量决定的,存储器容量越大,访问存储器所需 的时间越长。( 5.随着 CPU速度的不断提升,程序查询方式很少被采用的原因是 CPU与外设串行工 作 。( 得 分 评卷人 三、简答题(共 29分) 1.计算机指令中要用到的操作数一般可以来自哪些部件?(8分) 2.硬连线控制器是使用什么子部件来区分和表示指令不同的执行步骤的?它的基本工 作原理是什么?(7分) 3.计算机的存储器系统设计是如何实现“容量大”、“速度快”和“成本低”的要求的? (7分) 4.什么是总线周期?(7分) 1383

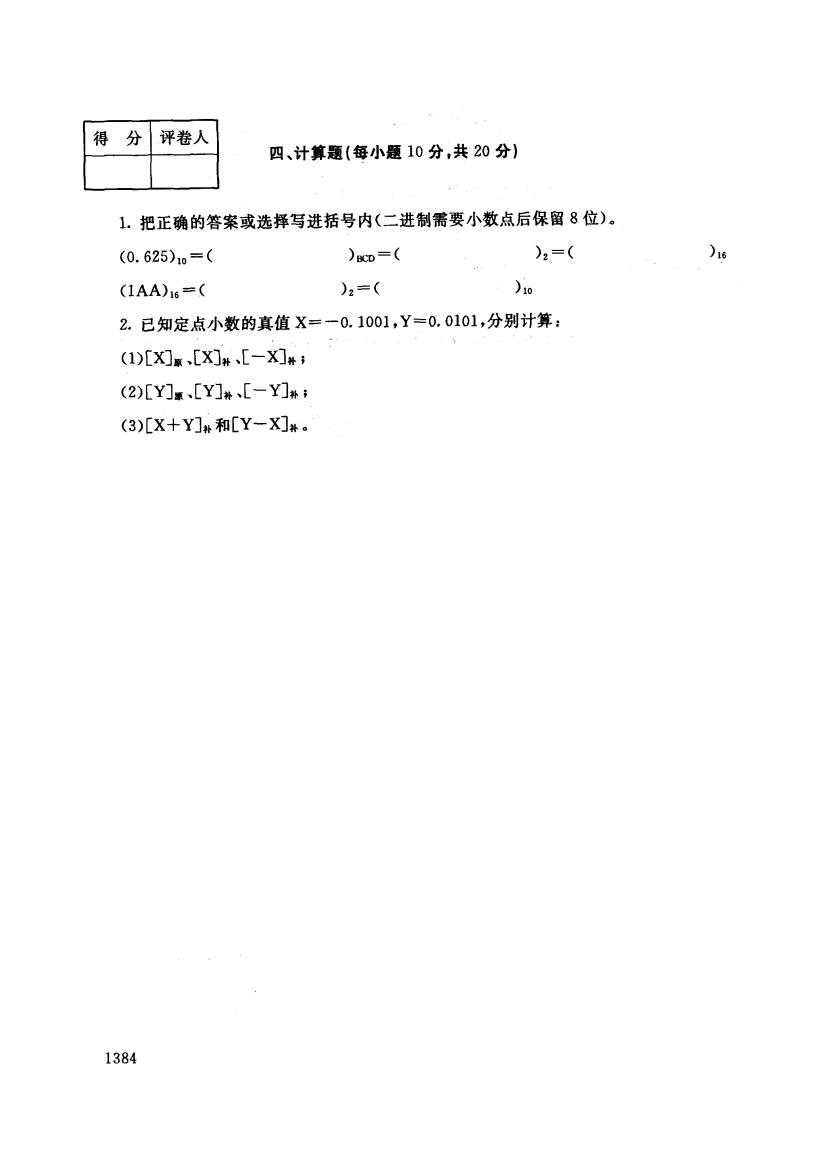

得分 评卷人 四、计算题(每小题10分,共20分) 1.把正确的答案或选择写进括号内(二进制需要小数点后保留8位)。 (0.625)10=( )cD=( )2=( )16 (1AA)16=( )2=( )0 2.已知定点小数的真值X=一0.1001,Y=0.0101,分别计算: (1)[X]原、[X]#、[-X]#; (2)[Y]原、[Y]#、[-Y]#; (3)[X+Y]#和[Y-X]#。 1384

得 分 评卷人 四、计算题(每小题 10分,共 20分) 1.把正确的答案或选择写进括号内(二进制需要小数点后保留8位)。 (0.625),0=( ) BCD =( )2=( (lAA),6二( )z=( ),。 2.已知定点小数的真值X=-0. 1001, Y=O. 0101,分别计算: (1)仁习原、[X〕补汇一X]补; (2)[Y]w "[Y]*、[一Y]#; (3)[X+Y〕补和〔Y- X]# o 1384

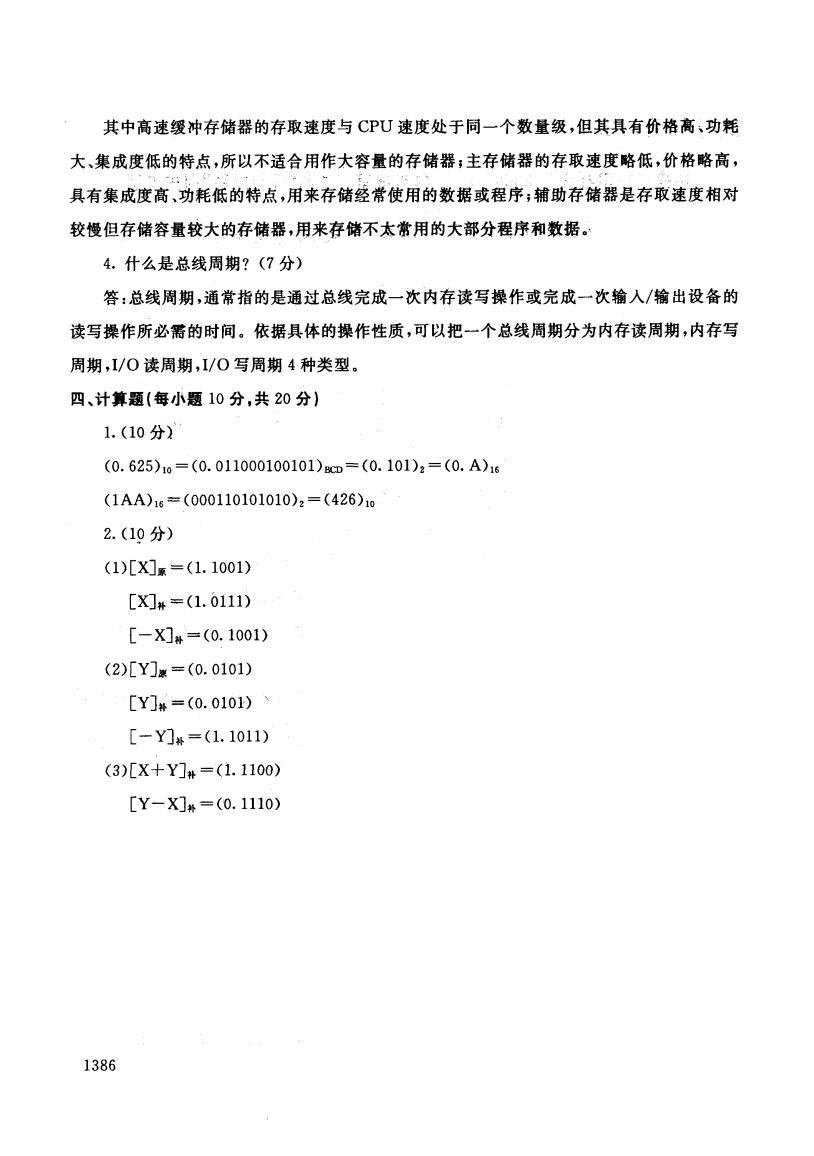

试卷代号:1254 中央广播电视大学2009一2010学年度第一学期“开放本科”期末考试 计算机组成原理 试题答案及评分标准 (供参考) 2010年1月 一、选择题(每小题3分,共36分) 1.B 2.C 3.C 4.B 5,A 6.B 7.B 8.B 9.B 10.C 11.A 12.B 二、判断题(每小题3分,共15分) 1. 2.X 3./ 4.X 5./ 三、简答题(共29分) 1.计算机指令中要用到的操作数一般可以来自哪些部件?(8分) 答:(1)CPU内部的通用寄存器。此时应在指令字中给出用到的寄存器编号(寄存器名), 通用寄存器的数量一般为几个、十几个,故在指令字中须为其分配2、3、4、5或更多一点的位数 来表示一个寄存器。 (2)外围设备(接口)中的一个寄存器。通常用设备编号、或设备入出端口地址、或设备映 像地址(与内存储器地址统一编址的一个设备地址编号)来表示。 (3)内存储器的一个存储单元。此时应在指令字中给出该存储单元的地址。 2.硬连线控制器是使用什么子部件来区分和表示指令不同的执行步骤的?它的基本工 作原理是什么?(7分) 答:在硬连线控制器中,由节拍发生器((timing)来区分指令不同的执行步骤的。 节拍发生器是由几个触发器电路实现的典型的时序逻辑电路,它为指令的每一个执行步 骤提供一个节拍状态信号,而节拍状态的变换标明了一条指令执行步骤的次序关系。 3.计算机的存储器系统设计是如何实现“容量大”、“速度快”和“成本低”的要求的? (7分) 答:将存储器系统设计成由高速缓冲存储器、主存储器和辅助存储器组成的多级结构。 1385

试卷代号:1254 中央广播电视大学2009-2010学年度第一学期“开放本科”期末考试 计算机组成原理 试题答案及评分标准 (供参考) 2010年 1月 一、选择题(每小题 3分.共 36分) 1. B 2. C 3. C 4. B 5. A 6.B _ 7.B 8.B 9.B 10.C 11.A 12.B 二、判断题 【每小题 3分,共 15分》 1.侧 2. )( 3.了 4. )( 5.丫 三、简答题(共 29分) 1.计算机指令中要用到的操作数一般可以来自哪些部件?(8分) 答:(1 )CPU内部的通用寄存器。此时应在指令字中给出用到的寄存器编号(寄存器名), 通用寄存器的数量一般为几个、十几个,故在指令字中须为其分配 2,3,4,5或更多一点的位数 来表示一个寄存器。 (2)外围设备(接口)中的一个寄存器。通常用设备编号、或设备人出端口地址、或设备映 像地址(与内存储器地址统一编址的一个设备地址编号)来表示。 (3)内存储器的一个存储单元。此时应在指令字中给出该存储单元的地址。 2.硬连线控制器是使用什么子部件来区分和表示指令不同的执行步骤的?它的基本工 作原理是什么?(7分) 答:在硬连线控制器中,由节拍发生器(timing)来区分指令不同的执行步骤的。 节拍发生器是由几个触发器电路实现的典型的时序逻辑电路,它为指令的每一个执行步 骤提供一个节拍状态信号,而节拍状态的变换标明了一条指令执行步骤的次序关系。 3.计算机的存储器系统设计是如何实现“容量大”、“速度快”和“成本低”的要求的? (7分) 答:将存储器系统设计成由高速缓冲存储器、主存储器和辅助存储器组成的多级结构。 1385

其中高速缓冲存储器的存取速度与CPU速度处于同一个数量级,但其具有价格高、功耗 大、集成度低的特点,所以不适合用作大容量的存储器:主存储器的存取速度略低,价格略高, 具有集成度高、功耗低的特点,用来存储经常使用的数据或程序;辅助存储器是存取速度相对 较慢但存储容量较大的存储器,用来存储不太常用的大部分程序和数据。 4.什么是总线周期?(7分) 答:总线周期,通常指的是通过总线完成一次内存读写操作或完成一次输人/输出设备的 读写操作所必需的时间。依据具体的操作性质,可以把一个总线周期分为内存读周期,内存写 周期,I/0读周期,I/O写周期4种类型。 四、计算题(每小题10分,共20分)】 1.(10分) (0.625)10=(0.011000100101)co=(0.101)2=(0.A)16 (1AA)16=(000110101010)2=(426)10 2.(10分) (1)[X]原=(1.1001) [X]#=(1.0111) [-X]#=(0.1001) (2)[Y]g=(0.0101) [Y]#=(0.0101) A [-Y]4=(1.1011) (3)[X+Y]#=(1.1100) [Y-X]=(0.1110) 1386

其中高速缓冲存储器的存取速度与CPU速度处于同一个数量级,但其具有价格高、功耗 大、集成度低的特点,所以不适合用作大容量的存储器;主存储器的存取速度略低,价格略高, 具有集成度高、劝耗低的特扁用来荐储痉常使用的数据或程序;辅助存储器是存敢速度相对 较慢但存储容量较大的存储器,用来存储不太常用的大部分程序和数据。, 4.什么是总线周期?(7分) 答:总线周期,通常指的是通过总线完成一次内存读写操作或完成一次输人/输出设备的 读写操作所必需的时间。依据具体的操作性质,可以把一个总线周期分为内存读周期,内存写 周期,1/O读周期,1/O写周期 4种类型。 四、计算题(每小题 10分,共20分) 1. (1。分)气几 (0.625),0=(0.011000100101),D=(0. 101)2=(0. A),, (lAA)s”(000110101010)2=(426),0 2.(1p分) (1)[X]原=(1.1001) [X〕补二(1.0111) 〔一X]#一(0.1001) (2)仁Y]m = (0. [Y]#=(0. 0101) 0101) [一Y〕补=(1.1011) (3)[X+Y]* =(1. [Y一X]二=(0. 1100) 1110) 1386