第9章C55x的硬件扩展 9.1硬件设计概述 9.2DSP系统的基本电路设计 ■9.3外部程序存储器扩展 ■9.4外部数据存储器扩展 9.5C55x与A/D和D/A转换器的接▣ 3

第9章 C55x的硬件扩展 ◼9.1 硬件设计概述 ◼9.2 DSP系统的基本电路设计 ◼9.3 外部程序存储器扩展 ◼9.4 外部数据存储器扩展 ◼9.5 C55x与A/D和D/A转换器的接口 3

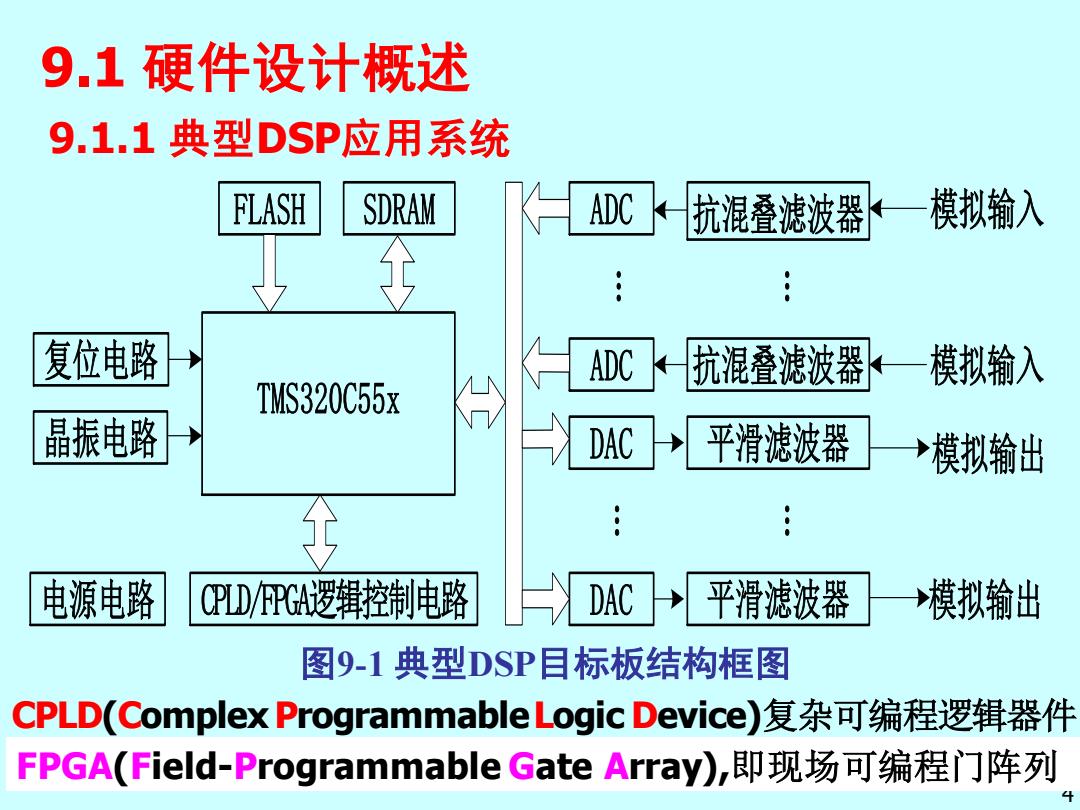

9.1硬件设计概述 9.1.1典型DSP应用系统 FLASH SDRAM ADC 抗混叠滤波器 一模拟输入 : 复位电路 ADC 抗混叠滤波器 模拟输入 TMS320C55x 晶振电路 DAC 平滑滤波器 →模拟输出 : 电源电路 CPID/PGA逻辑控制电路 DAC →平滑滤波器 >模拟输出 图9-1典型DSP目标板结构框图 CPLD(Complex Programmable Logic Device)复杂可编程逻辑器件 FPGA(Field-Programmable Gate Array),即现场可编程门阵列

9.1 硬件设计概述 TMS320C55x FLASH SDRAM 复位电路 电源电路 晶振电路 ADC ADC DAC DAC 抗混叠滤波器 抗混叠滤波器 平滑滤波器 CPLD/FPGA逻辑控制电路 平滑滤波器 … … … … 模拟输入 模拟输入 模拟输出 模拟输出 9.1.1 典型DSP应用系统 图9-1 典型DSP目标板结构框图 4 FPGA(Field-Programmable Gate Array),即现场可编程门阵列 CPLD(Complex Programmable Logic Device)复杂可编程逻辑器件

9.1.2DSP系统硬件设计流程 确定硬件实施方案 器件的选择 原理图设计 PCB设计 硬件调试 图9-2DSP系统硬件设计流程图 5

9.1.2 DSP系统硬件设计流程 确定硬件实施方案 原理图设计 器件的选择 PCB设计 硬件调试 图9-2 DSP系统硬件设计流程图 5

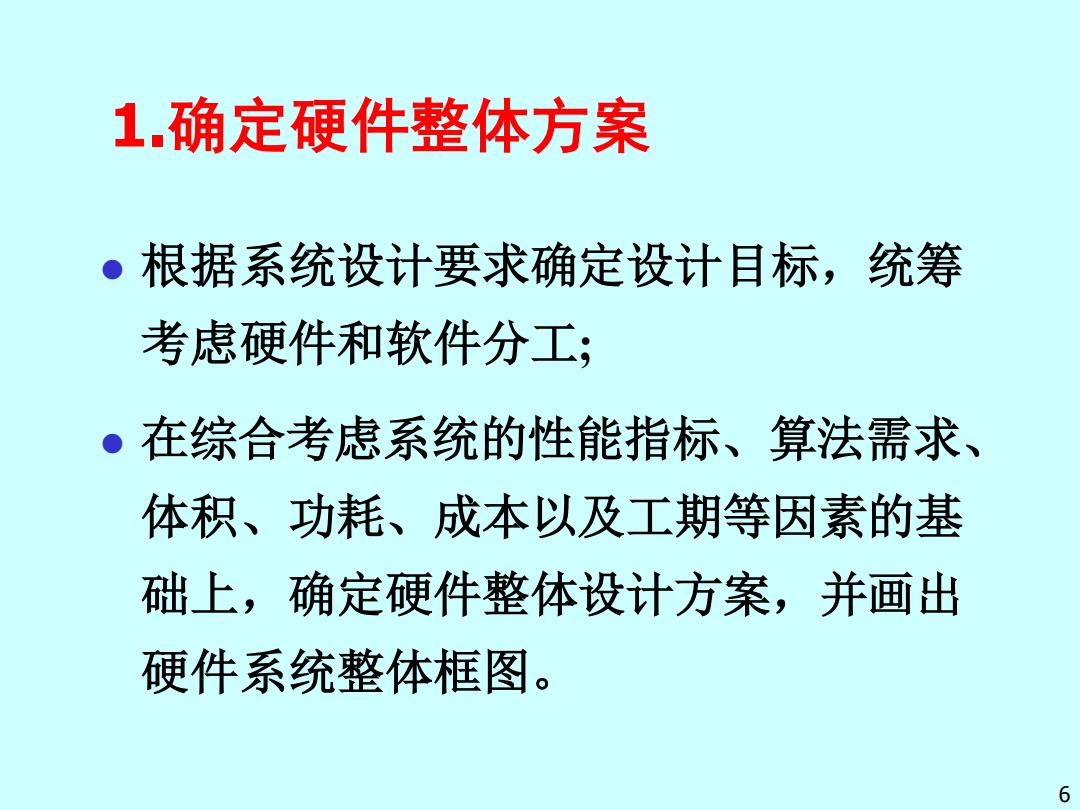

1.确定硬件整体方案 ·根据系统设计要求确定设计目标,统筹 考虑硬件和软件分工; ·在综合考虑系统的性能指标、算法需求、 体积、功耗、成本以及工期等因素的基 础上,确定硬件整体设计方案,并画出 硬件系统整体框图。 6

1.确定硬件整体方案 ⚫ 根据系统设计要求确定设计目标,统筹 考虑硬件和软件分工; ⚫ 在综合考虑系统的性能指标、算法需求、 体积、功耗、成本以及工期等因素的基 础上,确定硬件整体设计方案,并画出 硬件系统整体框图。 6

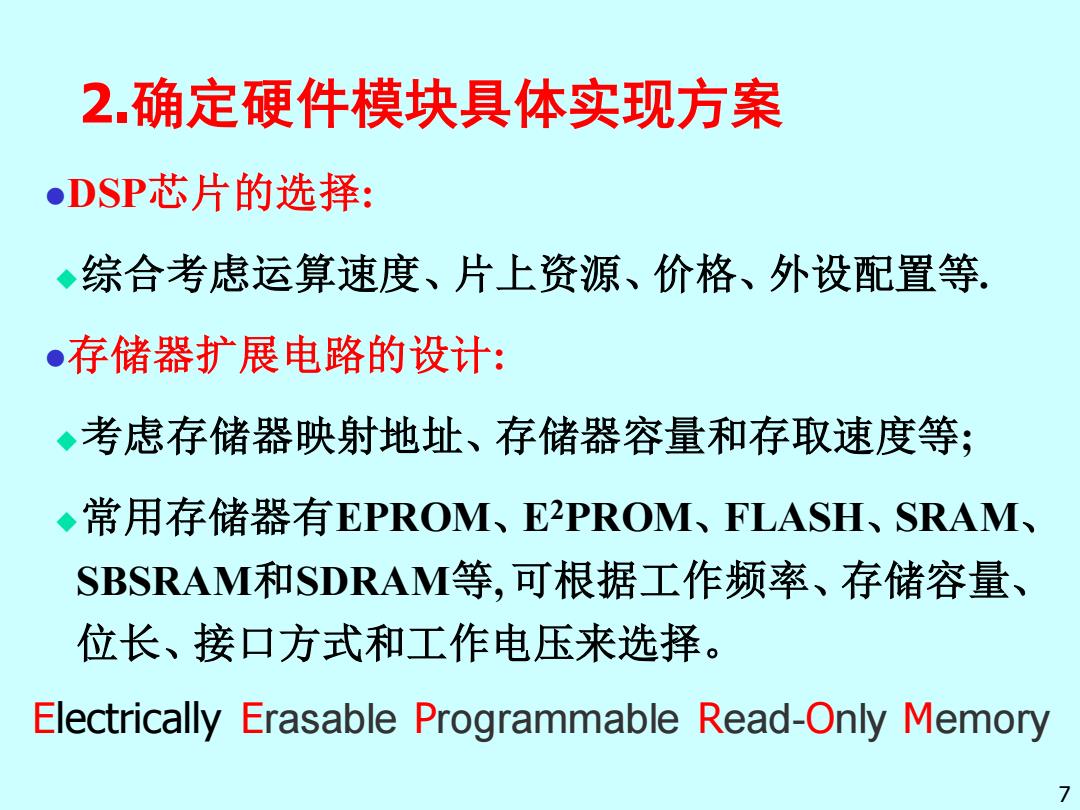

2.确定硬件模块具体实现方案 DSP芯片的选择: ◆综合考虑运算速度、片上资源、价格、外设配置等。 ●存储器扩展电路的设计: ◆考虑存储器映射地址、存储器容量和存取速度等; ◆常用存储器有EPROM、E2PROM、FLASH、SRAM、 SBSRAM和SDRAM等,可根据工作频率、存储容量、 位长、接口方式和工作电压来选择。 Electrically Erasable Programmable Read-Only Memory

2.确定硬件模块具体实现方案 ⚫DSP芯片的选择: ◆综合考虑运算速度、片上资源、价格、外设配置等. ⚫存储器扩展电路的设计: ◆考虑存储器映射地址、存储器容量和存取速度等; ◆常用存储器有EPROM、E2PROM、FLASH、SRAM、 SBSRAM和SDRAM等, 可根据工作频率、存储容量、 位长、接口方式和工作电压来选择。 7 Electrically Erasable Programmable Read-Only Memory

。模拟数字混合电路的设计: ◆根据设计要求,综合考虑转换速度、精度、通道 数以及是否要求片上自带采样器、多路选择器、 基准电源等因素,来选择ADC、DAC的型号。 ●逻辑控制电路的设计: ◆包括译码、状态控制、同步控制等; 系统的逻辑控制通常采用可编程逻辑器件(CPLD ◆ 或FPGA)来实现。 8

⚫ 模拟数字混合电路的设计: 8 ◆ 根据设计要求, 综合考虑转换速度、精度、通道 数以及是否要求片上自带采样器、多路选择器、 基准电源等因素, 来选择ADC、DAC的型号。 ⚫ 逻辑控制电路的设计: ◆ 包括译码、状态控制、同步控制等; ◆ 系统的逻辑控制通常采用可编程逻辑器件(CPLD 或FPGA)来实现

。通信接口的设计: ◆主要根据系统对通信速率的要求来选择通信方式; ◆对VC5509A和VC5510来讲,I2C总线的数据传输速率 可从10~400Kb/S,McBSP的最高频率可达CPU时钟频 率的1/2,若要求过高可考虑通过总线进行通信。 。人机接口的设计: ◆常用的人机接口主要有键盘和显示器; ◆可以通过与其它单片机的通信来构成,也可与DSP芯 片经FPGA/CPLD构成。 。电源和时钟电路的设计: ◆主要考虑电压的高低和电流的大小,既要满足电压的 匹配,又要满足电流容量的要求。 9

⚫通信接口的设计: 9 ◆主要根据系统对通信速率的要求来选择通信方式; ◆对VC5509A和VC5510来讲, I2C总线的数据传输速率 可从10~400Kb/s, McBSP的最高频率可达CPU时钟频 率的1/2, 若要求过高可考虑通过总线进行通信。 ⚫ 人机接口的设计: ◆常用的人机接口主要有键盘和显示器; ◆可以通过与其它单片机的通信来构成, 也可与DSP芯 片经FPGA/CPLD构成。 ⚫ 电源和时钟电路的设计: ◆主要考虑电压的高低和电流的大小, 既要满足电压的 匹配, 又要满足电流容量的要求

3.原理图设计 。原理图的设计是关键的一步: ◆必须清楚地了解器件的特性、使用方法 和系统的开发; ◆必要时可对单元电路进行功能仿真甚至 进行实验测试。 设计软件:Altium Designer(前身protel99SE), PADS或candence(多层复杂PCB) 10

3.原理图设计 ⚫ 原理图的设计是关键的一步: ◆必须清楚地了解器件的特性、使用方法 和系统的开发; ◆必要时可对单元电路进行功能仿真甚至 进行实验测试。 10 设计软件: Altium Designer(前身protel 99SE), PADS或candence(多层复杂PCB)

4.PCB设计(Printed Circuit Board) 数字器件正朝着高速低功耗、小体积、高抗干扰性的 方向发展,这一发展趋势对印刷电路板的设计提出了 很多新要求。 ●由于DSP指令周期为ns级,高频特性已经非常明显, 这就要求设计人员既要熟悉系统的工作原理,还要清 楚硬件系统的抗干扰技术、布线工艺和系统结构设计 ●必要时采用多层板进行PCB设计,以提高布通率和抗 噪声性能,保证信号的完整性。 PCB设计软件:Altium Designer(前身protel99SE), PADS或candence(多层复杂PCB) 11

4. PCB设计 (Printed Circuit Board) ⚫数字器件正朝着高速低功耗、小体积、高抗干扰性的 方向发展,这一发展趋势对印刷电路板的设计提出了 很多新要求。 ⚫由于DSP 指令周期为ns 级, 高频特性已经非常明显, 这就要求设计人员既要熟悉系统的工作原理, 还要清 楚硬件系统的抗干扰技术、布线工艺和系统结构设计。 ⚫必要时采用多层板进行PCB设计, 以提高布通率和抗 噪声性能, 保证信号的完整性。 11 PCB设计软件: Altium Designer(前身protel 99SE), PADS或candence(多层复杂PCB) Altium 奥腾公司

5.硬件调试 ·主要步骤: ◆拿到PCB板后,首先应检查是否同电路板图一致,对 于重要的点和线(特别是电源、地)要用万用表进行 测试,确保连接正确; ◆对所用的元器件进行质量检查; ◆按印刷电路板上器件名称、标识焊接好各个元器件; ◆采用硬件仿真器和万用表、示波器、信号发生器等 对硬件电路电器系统测试,看是否能正常工作。通 常应对不同功能模块编写出相应的测试程序。 12

5. 硬件调试 ⚫ 主要步骤: ◆ 拿到PCB板后, 首先应检查是否同电路板图一致, 对 于重要的点和线(特别是电源、地)要用万用表进行 测试, 确保连接正确; ◆ 对所用的元器件进行质量检查; ◆ 按印刷电路板上器件名称、标识焊接好各个元器件; ◆ 采用硬件仿真器和万用表、示波器、信号发生器等 对硬件电路电器系统测试, 看是否能正常工作。通 常应对不同功能模块编写出相应的测试程序。 12