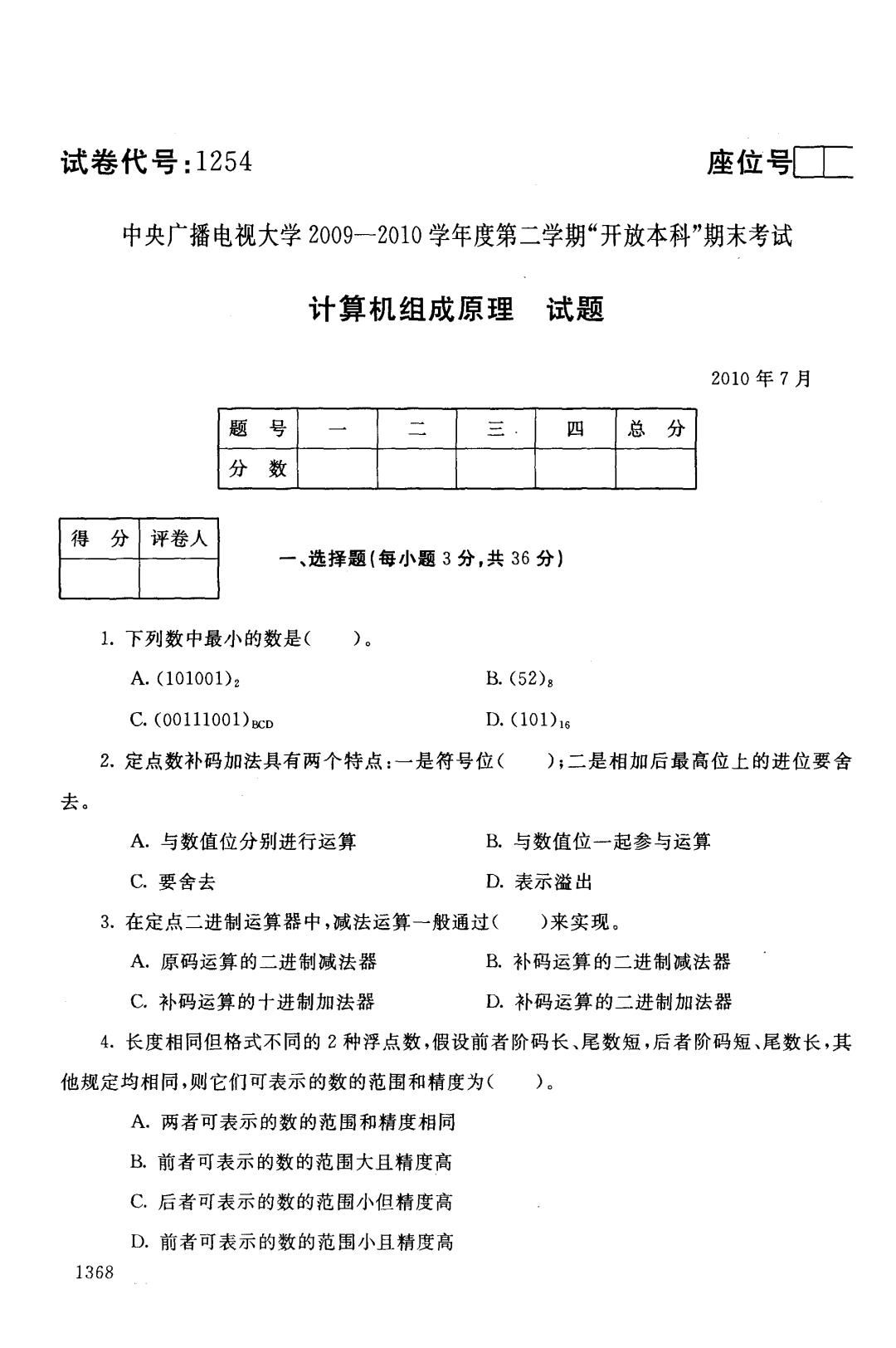

试卷代号:1254 座位号 中央广播电视大学2009一2010学年度第二学期“开放本科”期末考试 计算机组成原理试题 2010年7月 题 号 三 四 总分 分 数 得分 评卷人 一、选择题(每小题3分,共36分) 1.下列数中最小的数是()。 A.(101001)2 B.(52)8 C.(00111001)cD D.(101)16 2.定点数补码加法具有两个特点:一是符号位();二是相加后最高位上的进位要舍 去。 A.与数值位分别进行运算 B.与数值位一起参与运算 C.要舍去 D.表示溢出 3.在定点二进制运算器中,减法运算一般通过( )来实现。 A.原码运算的二进制减法器 B.补码运算的二进制减法器 C.补码运算的十进制加法器 D.补码运算的二进制加法器 4.长度相同但格式不同的2种浮点数,假设前者阶码长、尾数短,后者阶码短、尾数长,其 他规定均相同,则它们可表示的数的范围和精度为()。 A.两者可表示的数的范围和精度相同 B.前者可表示的数的范围大且精度高 C.后者可表示的数的范围小但精度高 D.前者可表示的数的范围小且精度高 1368

试卷代号 2 5 座位号 中央广播电视大学 0 0 2010 度第 二学 本科 期末 计算机组成原理试题 2010 年7 题号 总分 分数 得分|评卷人 一、选择题{每小题 3分,共 6分) 1.下列数中最小的数是( )。 A. (101001) 2 B. (52)8 c. (00111001 >Sc D D. (101) 16 2. 法具 个特 一 是符号位 ) ;二是相加后最高位上的进位要舍 去。 A.与数值位分别进行运算 .与数值位一起参与运算 c. 舍去 表示 3. 点 二 减法 算一般 )来实现。 A.原码运算的二进制减法器 .补码运算的二进制减法器 c.补码运算的十进制加法器 .补码运算的二进制加法器 4. 长度 格式 的2 前者 码长 尾数 他规定均相同,则它们可表示的数的范围和精度为( )。 A.两者可表示的数的范围和精度相同 B. 前者 且精度高 c.后者可表示的数的范围小但精度高 D. 前者 且精 1368

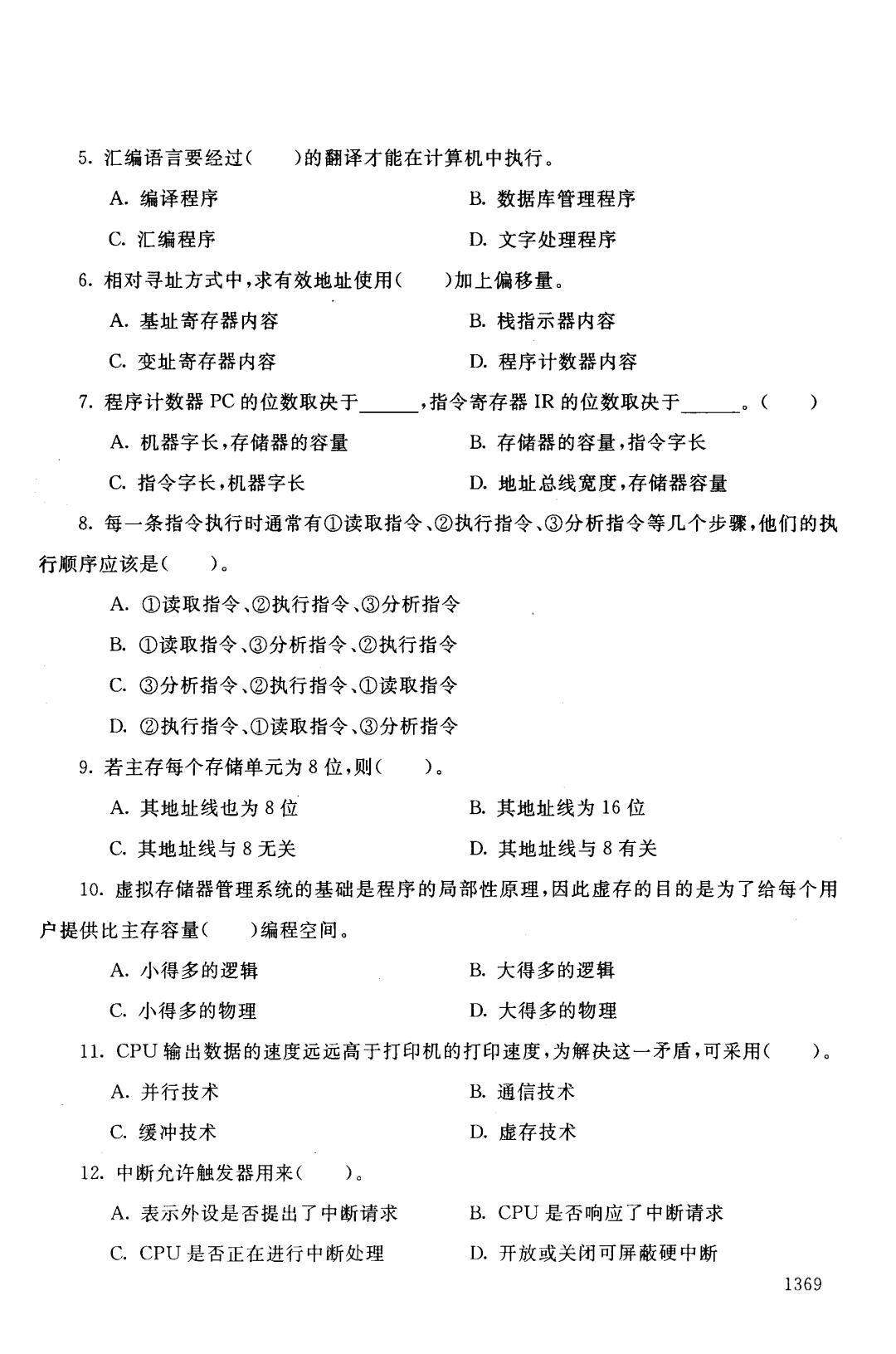

5.汇编语言要经过( )的翻译才能在计算机中执行。 A.编译程序 B.数据库管理程序 C.汇编程序 D.文字处理程序 6.相对寻址方式中,求有效地址使用( )加上偏移量。 A.基址寄存器内容 B.栈指示器内容 C.变址寄存器内容 D.程序计数器内容 7.程序计数器P℃的位数取决于 ,指令寄存器IR的位数取决于 A.机器字长,存储器的容量 B.存储器的容量,指令字长 C.指令字长,机器字长 D.地址总线宽度,存储器容量 8.每一条指令执行时通常有①读取指令、②执行指令、③分析指令等几个步骤,他们的执 行顺序应该是()。 A.①读取指令、②执行指令、③分析指令 B.①读取指令、③分析指令、②执行指令 C.③分析指令、②执行指令、①读取指令 D.②执行指令、①读取指令、③分析指令 9.若主存每个存储单元为8位,则()。 A.其地址线也为8位 B.其地址线为16位 C.其地址线与8无关 D.其地址线与8有关 10.虚拟存储器管理系统的基础是程序的局部性原理,因此虚存的目的是为了给每个用 户提供比主存容量( )编程空间。 A.小得多的逻辑 B.大得多的逻辑 C.小得多的物理 D.大得多的物理 11.CPU输出数据的速度远远高于打印机的打印速度,为解决这一矛盾,可采用()。 A.并行技术 B.通信技术 C.缓冲技术 D.虚存技术 12.中断允许触发器用来()。 A.表示外设是否提出了中断请求 B.CPU是否响应了中断请求 C.CPU是否正在进行中断处理 D.开放或关闭可屏蔽硬中断 1369

B. CPU D. 放或 可屏 蔽硬 5. )的翻译才能在计算机中执行。 A. 序B. 库管 程序 c.汇编程序D.文字处理程序 6. 寻址方 求有 地址使 )加上偏移量。 A. 容B. 枝指示 c.变址寄存器内容D.程序计数器内容 7. 器PC 位数取 器IR 取决 A. 机器 量B. 容量 令宇长 c.指令字长,机器宇长 .地址总线宽度,存储器容量 8. 指令 时通 ①读取 ②执 分析指令等几个步骤 行顺序应该是( )。 A. ①读 ②执行指 B. ①读 ③分析指 ②执 指令 c.③分析指令、②执行指令、①读取指令 D. ②执行 ①读取指 9. 储单 为8 )。 A. 其地 为8 位B. 地址 为16 C. 地址 与8 关D. 地址 与8 10. 是程 部性原 此虚 每个 户提供比主存容量( )编程空间。 A. 辑B. 大得 c.小得多的物理 .大得多的物理 11. CPU 度远 远高 于 可采 )。 A. 并行 B. 通信技术 c.缓冲技术 .虚存技术 12. 断允 )。 A. 示外设是 出 了 C. CPU 在进 断处 1369

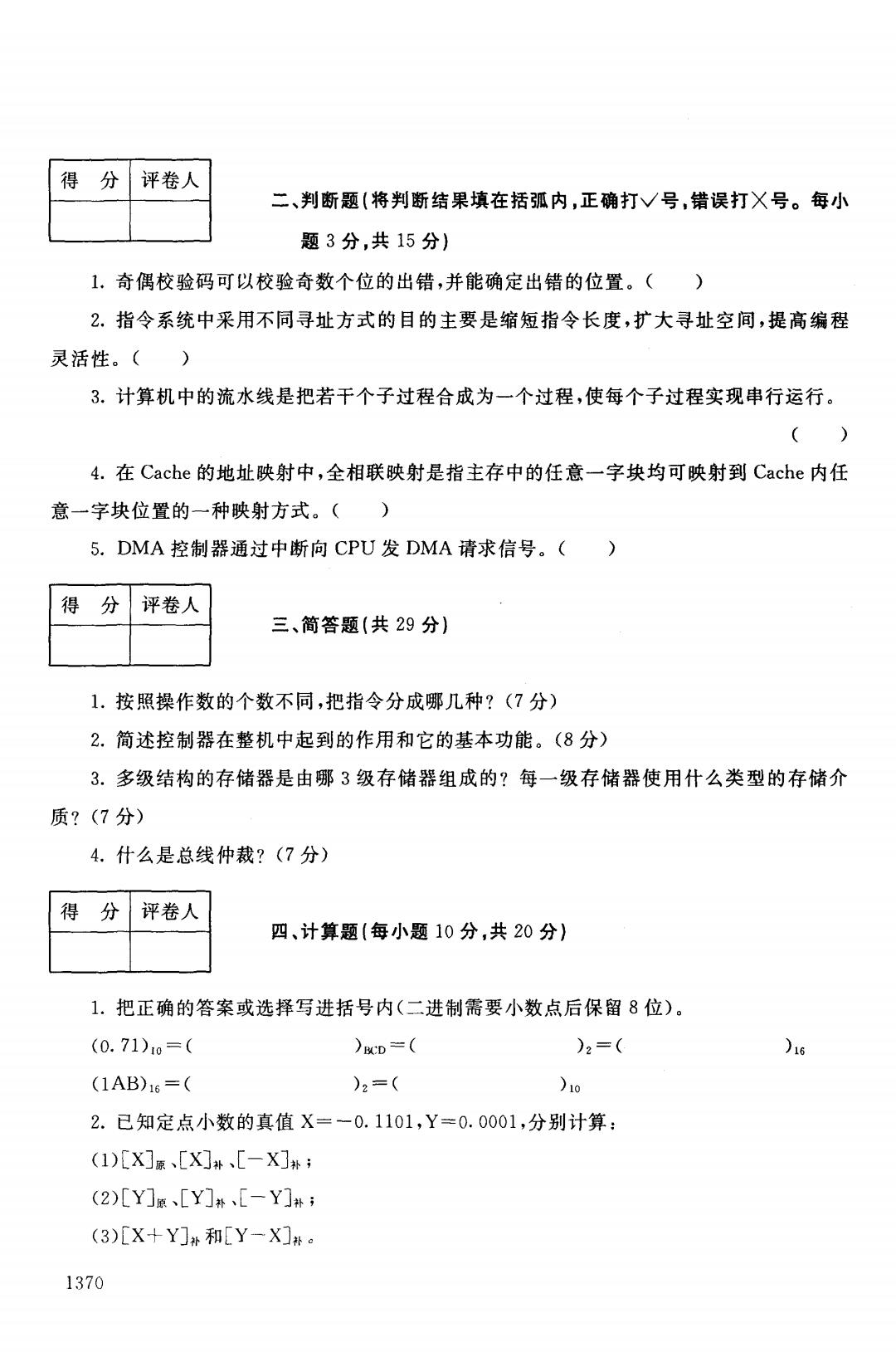

得 分 评卷人 二、判断题(将判断结果填在括弧内,正确打√号,错误打X号。每小 题3分,共15分) 1.奇偶校验码可以校验奇数个位的出错,并能确定出错的位置。() 2.指令系统中采用不同寻址方式的目的主要是缩短指令长度,扩大寻址空间,提高编程 灵活性。() 3.计算机中的流水线是把若干个子过程合成为一个过程,使每个子过程实现串行运行。 () 4.在Cache的地址映射中,全相联映射是指主存中的任意一字块均可映射到Cache内任 意一字块位置的一种映射方式。() 5.DMA控制器通过中断向CPU发DMA请求信号。() 得 分 评卷人 三、简答题(共29分) 1.按照操作数的个数不同,把指令分成哪几种?(7分) 2.简述控制器在整机中起到的作用和它的基本功能。(8分) 3.多级结构的存储器是由哪3级存储器组成的?每一级存储器使用什么类型的存储介 质?(7分) 4.什么是总线仲裁?(7分) 得 分 评卷人 四、计算题(每小题10分,共20分) 1.把正确的答案或选择写进括号内(二进制需要小数点后保留8位)。 (0.71)10=( )D=( )2=( )6 (1AB)16=( )2=( )10 2.已知定点小数的真值X=-0.1101,Y=0.0001,分别计算: (1)[X]原、[X幻补、[一X]补; (2)[Y]原、[Y]林、[一Y]林; (3)[X+Y]补和[Y-X]补。 1370

得分|评卷人 二、判断题{将判断结果填在括弧内,正确打\/号,错误打×号。每小 3分,共 5分) 1.奇偶校验码可以校验奇数个位的出错,并能确定出错的位置。( ) 2. 指令 寻址方 址 空 灵活性。( ) 3. 流水线是把 子过程 一个过 程实 运行 ( ) 4. 在Cache 映射是 块均 到Cache 意一字块位置的→种映射方式。( ) 5. DMA 器通过 向CPU 发DMA 求信号 ) 得分 1评卷人 三、简答题{共 9分) 1.按照操作数的个数不同,把指令分成哪几种? (7 2. 和 它 。(8 3. 存储器是 哪3 存储 级存 质? (7 4. 线仲裁 (7 得分|评卷人 四、计算题{每小题 0分,共 0分} 1.把正确的答案或选择写进括号内(二进制需要小数点后保留 8位)。 (0.71) 10 = ( (lA B ) 16= ( )IlCD = ( )2 = ( )2 =( 16 2. 知定 小数 值X= -0.1101 , Y=O. 0001 (1) 1 f - X]*f ; (2)[Y] 、[Y]*f -Y] (3)[X 十Y]* 和[Y 一X] 1370

试卷代号:1254 中央广播电视大学2009一2010学年度第二学期“开放本科”期末考试 计算机组成原理试题答案及评分标准 (供参考) 2010年7月 一、选择题(每小题3分,共36分) 1.C 2.B 3.D 4.C 5.C 6.D 7.B 8.B 9.C 10.B 11.C 12.D 二、判断题(每小题3分,共15分)】 1.X 2.V 3.X 4.√ 5./ 三、简答题(共29分) 1.按照操作数的个数不同,把指令分成哪几种?(7分) 答:按照操作数的个数不同,指令分为下面四种: (1)无操作数指令;(2)单操作数指令;(3)双操作数指令;(4)多操作数指令。 2.简述控制器在整机中起到的作用和它的基本功能。(8分) 答:控制器部件是计算机的五大功能部件之一,其作用是向整机中包括控制器部件在内的 每个部件提供协同运行所需要的控制信号。 计算机的最本质的功能是连续执行指令,而每一条指令往往又要分成几个执行步骤才得 以完成。所以,控制器的基本功能是,依据当前正在执行的指令和它当前所处的执行步骤,形 成并提供出在这一时刻整机各部件要用到的控制信号,并且决定下一步将进入哪个执行步骤。 3.多级结构的存储器是由哪3级存储器组成的?每一级存储器使用什么类型的存储介 质?(7分) 答:多级结构的存储器是由高速缓存、主存储器和辅助存储器(或虚拟存储器)组成的。 高速缓冲存储器使用静态存储器芯片实现,主存储器通常使用动态存储器芯片实现,而辅 助存储器(或虚拟存储器)通常则使用快速磁盘设备上.的一片存储区。前两者是半导体电路器 件,以数字逻辑电路方式进行读写,后者则是在磁性介质层中通过电磁转换过程完成信息读 写。 1371

试卷代号 中央广播电视大学 0 0 2010 度 第 二学 开放 末考 计算机组成原理试题答案及评分标准 (供参考) 2010 年7 一、选择题{每小题 3分,共 6分) I. e 7. B 2. B 8. B 3. D 9. e 4. e 10. B 5. e 11. e 6. D 12. D 二、判断题(每小题 3分,共 5分) 1. X 2. v 3. X 4. v 5.ν 三、简答题{共 9分) 1.按照操作数的个数不同,把指令分成哪几种? (7 答:按照操作数的个数不同,指令分为下面四种: (1)元操作数指令 )单操作数指令; (3)双操作数指令刊的多操作数指令。 2. 器在整机 到 的 基本功 能 。(8 答:控制器部件是计算机的五大功能部件之一,其作用是向整机中包括控制器部件在内的 每个部件提供协同运行所需要的控制信号。 计算机的最本质的功能是连续执行指令,而每一条指令往往又要分成几个执行步骤才得 以完成。所以,控制器的基本功能是,依据当前正在执行的指令和它当前所处的执行步骤,形 成并提供出在这一时刻整机各部件要用到的控制信号,并且决定下一步将进入哪个执行步骤。 3. 器是 哪3 级存 器组 器使 质? (7 答:多级结构的存储器是由高速缓存、主存储器和辅助存储器(或虚拟存储器)组成的。 高速缓冲存储器使用静态存储器芯片实现,主存储器通常使用动态存储器芯片实现,而辅 助存储器(或虚拟存储器)通常则使用快速磁盘设备上的→片存储区。前两者是半导体电路器 件,以数字逻辑电路方式进行读写,后者则是在磁性介质层中通过电睦转换过程完成信息读 写。 1:171

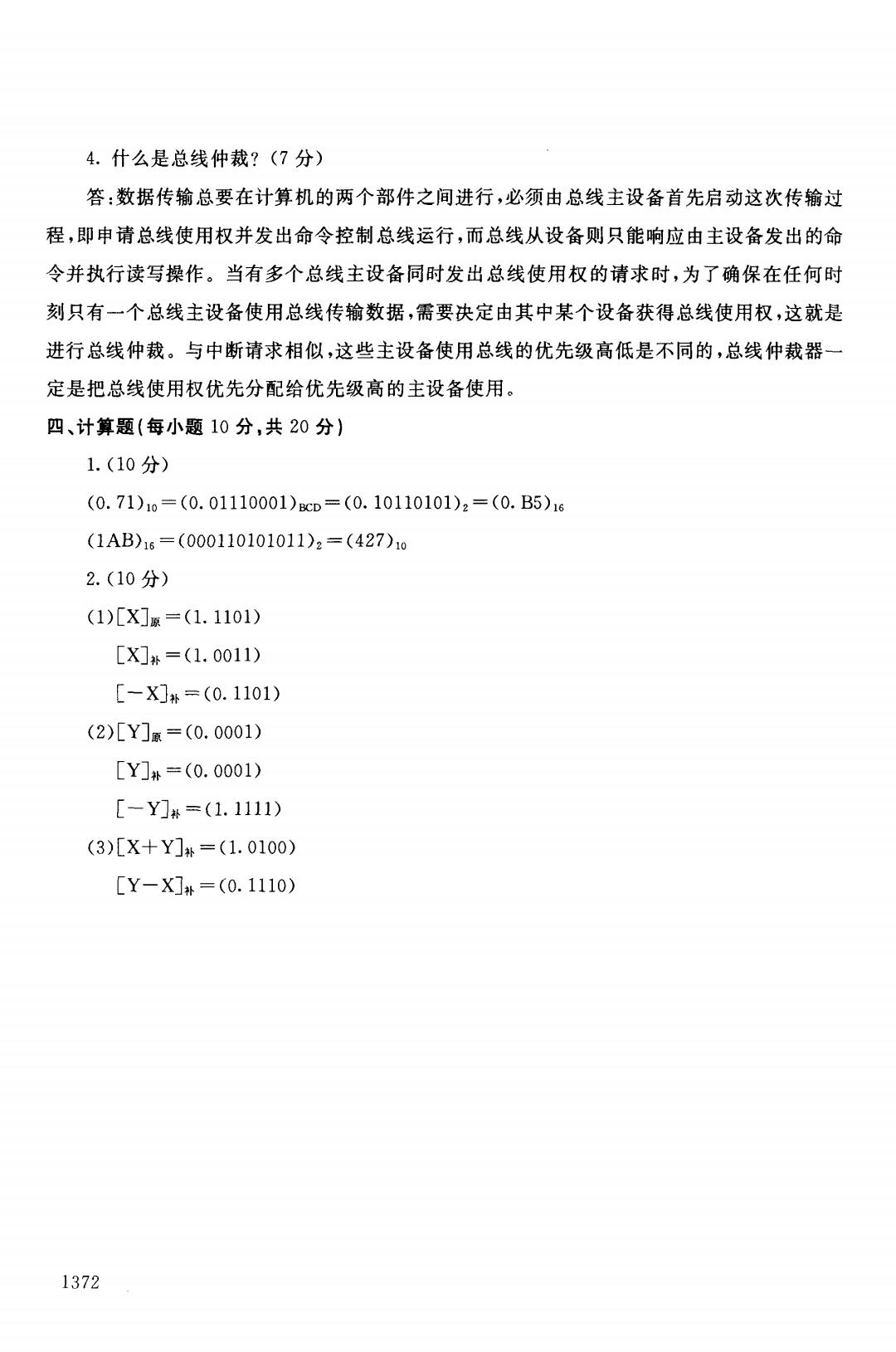

4.什么是总线仲裁?(7分) 答:数据传输总要在计算机的两个部件之间进行,必须由总线主设备首先启动这次传输过 程,即申请总线使用权并发出命令控制总线运行,而总线从设备则只能响应由主设备发出的命 令并执行读写操作。当有多个总线主设备同时发出总线使用权的请求时,为了确保在任何时 刻只有一个总线主设备使用总线传输数据,需要决定由其中某个设备获得总线使用权,这就是 进行总线仲裁。与中断请求相似,这些主设备使用总线的优先级高低是不同的,总线仲裁器一 定是把总线使用权优先分配给优先级高的主设备使用。 四、计算题(每小题10分,共20分) 1.(10分) (0.71)10=(0.01110001)cD=(0.10110101)2=(0.B5)16 (1AB)16=(000110101011)2=(427)10 2.(10分) (1)[X]原=(1.1101) [X]#=(1.0011) [-X]补=(0.1101) (2)[Y]原=(0.0001) [Y]补=(0.0001) [-Y]林=(1.1111) (3)[X+Y]=(1.0100) [Y-X]林=(0.1110) 1372

4. (7 答:数据传输总要在计算机的两个部件之间进行,必须由总线主设备首先启动这次传输过 程,即申请总线使用权并发出命令控制总线运行,而总线从设备则只能响应由主设备发出的命 令并执行读写操作。当有多个总线主设备同时发出总线使用权的请求时,为了确保在任何时 刻只有一个总线主设备使用总线传输数据,需要决定由其中某个设备获得总线使用权,这就是 进行总线仲裁。与中断请求相似,这些主设备使用总线的优先级高低是不同的,总线仲裁器 定是把总线使用权优先分配给优先级高的主设备使用。 四、计算题(每小题 0分,共 0分) 1. (1 (0.71) 10 = (0. 0111000 1)BCD= (0.10110101) 2 = (0. B5)16 (1 AB) 16=(00011010101 1) 2 =(427)10 2. (1 (1 (1. 1101) [X]lf=(l. 0011) [ - X]lf = (0. 1101) (2)[Y] (0.000 1) [Y] (0.000 1) [-Y] (1.1111) (3) [X+Y]lf = (1. 0100 ) [Y-X] (0.1110) 1372