《VHDL语言及应用》课程教学大纲 课程名称:VHDL语言及应用 课程代码:TELE2120 英文名称:VHD Language and Its Application 课程性质:大类专业教学课程 学分/学时:2.5/(36课时+18实验)》 开课学期:第4学期 适用专业:电子信息类专业 先修课程:数字系统与逻辑设计 后续课程:毕业设计 开课单位:电子信息学院 课程负贵人:胡剑凌 大纲执笔人:黄旭 大纲审核人:胡剑凌 一、课程性质和教学目标 课程性质:VHD儿语言及应用是通信工程、信总工程、电子信息工程等专业的一门专业 课程,是“数字系统与逻辑设计”课程的后续课程。 教学目标:VDL语言及应用课程主要讲授利用可编程逻辑器件、使用VDL语言设计 实现数字电子系统。通过理论学习、实验、综合设计等环节,使学生了解大规模可编程逻 辑器件的基本知识和工作原理,掌握DL语言的基本语法和常用数字电路的程序设计方 法,熟练使用EDA工具软件QuartusⅡ进行数字电子系统的设计,为今后运用现代化手段 从事有关数字电子系统方面的设计和研究开发工作打下基础。本课程的具体教学目标如下: 1、了解大规模可编程逻辑器件的基本知识和工作原理,掌握VHDL语言的基本语法,掌握 使用VHL语言设计数字系统的方法:能够针对设计要求完成模块和系统的设计。 2、对设计的模块和系统,能选择可行的实验方案进行仿真和验证: 3、熟练使用EDA工具软件QuartusⅡ对数字电子系统进行设计与仿真,掌握软件仿真平 台的设计流程和方法, 二、 课程目标与毕业要求的对应关系 毕业要求 指标点 课程目标 3.设计1开发解决方31能利用专业知识,根据给定的设计指标, 设计通信领域的单元或过程 教学目标1 4.研究 4.2能基于专业理论,针对通信模块和系统 教学目标2 选择研究路线,设计可行的实验方案。 5.使用现代工具 5.2能针对复杂工程问题,选择并合理使用软 教学目标3 硬件设计与仿真平台

《VHDL 语言及应用》课程教学大纲 课程名称:VHDL 语言及应用 课程代码:TELE2120 英文名称:VHD Language and Its Application 课程性质:大类专业教学课程 学分/学时:2.5/(36 课时+18 实验) 开课学期:第 4 学期 适用专业:电子信息类专业 先修课程:数字系统与逻辑设计 后续课程:毕业设计 开课单位:电子信息学院 课程负责人:胡剑凌 大纲执笔人:黄旭 大纲审核人:胡剑凌 一、 课程性质和教学目标 课程性质:VHDL 语言及应用是通信工程、信息工程、电子信息工程等专业的一门专业 课程,是 “数字系统与逻辑设计”课程的后续课程。 教学目标:VHDL 语言及应用课程主要讲授利用可编程逻辑器件、使用 VHDL 语言设计 实现数字电子系统。通过理论学习、实验、综合设计等环节,使学生了解大规模可编程逻 辑器件的基本知识和工作原理,掌握 VHDL 语言的基本语法和常用数字电路的程序设计方 法,熟练使用 EDA 工具软件 QuartusⅡ进行数字电子系统的设计,为今后运用现代化手段 从事有关数字电子系统方面的设计和研究开发工作打下基础。本课程的具体教学目标如下: 1、 了解大规模可编程逻辑器件的基本知识和工作原理,掌握 VHDL 语言的基本语法,掌握 使用 VHDL 语言设计数字系统的方法;能够针对设计要求完成模块和系统的设计。 2、 对设计的模块和系统,能选择可行的实验方案进行仿真和验证; 3、 熟练使用 EDA 工具软件 QuartusⅡ对数字电子系统进行设计与仿真,掌握软件仿真平 台的设计流程和方法。 二、 课程目标与毕业要求的对应关系 毕业要求 指标点 课程目标 3. 设计/开发解决方 案 3.1 能利用专业知识,根据给定的设计指标, 设计通信领域的单元或过程 教学目标 1 4. 研究 4.2 能基于专业理论,针对通信模块和系统, 选择研究路线,设计可行的实验方案。 教学目标 2 5. 使用现代工具 5.2 能针对复杂工程问题,选择并合理使用软 硬件设计与仿真平台。 教学目标 3

三、课程教学内容及学时分配 1、橛述(3学时)(支撑课程目标1) 1.1EDA技术概述 1.2硬件描述语言简介 1.3基于HDL的自顶向下设计方法 1.4EDA设计流程 1.5常用EDA工具 1.6P核 夕目标及要求: I)掌握EDA技术的相关知识: 2)了解硬件描述语言的基本知识: 3)了解自项向下的设计方法和设计流程。 女作业内容 理解EDA技术和硬件描述语言的相关基础知识。 令讨论内容: 数电课程中传统的电路设计方法与自顶向下设计方法的比较 夕自学拓展 复习数字逻辑电路的相关知识 2、可编程逻辑器件(3学时)(支撑课程目标1) 2.1可编程逻辑器件概述 2.2简单可编程逻辑器件 2.3复杂可编程逻辑器件CPLD 2.4现场可编程门阵列FPGA 2.5 CPLD/FPGA器件荷介 2.6FPGA和CPLD的开发应用选择 令目标及要求:

三、 课程教学内容及学时分配 1、 概述(3 学时)(支撑课程目标 1) 1.1 EDA 技术概述 1.2 硬件描述语言简介 1.3 基于 HDL 的自顶向下设计方法 1.4 EDA 设计流程 1.5 常用 EDA 工具 1.6 IP 核 目标及要求: 1) 掌握 EDA 技术的相关知识; 2) 了解硬件描述语言的基本知识; 3) 了解自顶向下的设计方法和设计流程。 作业内容: 理解 EDA 技术和硬件描述语言的相关基础知识。 讨论内容: 数电课程中传统的电路设计方法与自顶向下设计方法的比较。 自学拓展: 复习数字逻辑电路的相关知识。 2、 可编程逻辑器件(3 学时)(支撑课程目标 1) 2.1 可编程逻辑器件概述 2.2 简单可编程逻辑器件 2.3 复杂可编程逻辑器件 CPLD 2.4 现场可编程门阵列 FPGA 2.5CPLD/FPGA 器件简介 2.6FPGA 和 CPLD 的开发应用选择 目标及要求:

1)掌握简单可编程逻辑器件的编程方法: 2)了解大规模可编程逻辑器件的基本知识和工作原理: 3)了解大规模可编程逻辑器件的基本使用方法。 令作业内容: 理解大规模可编程逻辑器件的基本知识和工作原理,。 讨论内容 可编程逻辑器件的编程方法和应用, ◇自学拓展: 回顾学过的数字电路相关知识,查阅可编程逻辑器件的数据手册。 3、VDL设计初步(6学时)(支捧课程目标1) 3.1组合逻辑电路的VHDL描述 3.2基本时序电路的VHDL描述 3.3计数器的VHDL描述 3.4实用计数器的VHDL描述 令目标及要求: 1)掌握常用组合逻辑电路的程序设计方法★: 2)掌握基本时序逻辑电路的程序设计方法: 3)掌握计数器的程序设计方法★△: 令作业内容 强化常用组合逻辑电路、触发器及计数器的程序设计。 令讨论内容: 讨论传统的数字电路设计方法与VDL设计方法。 自学拓展 查阅资料,设计其他课程中未讲解的常用数字电路。 4、Quartus]Ⅱ的使用(3学时)(支撑课程目标3) 4.1基本设计流程

1) 掌握简单可编程逻辑器件的编程方法; 2) 了解大规模可编程逻辑器件的基本知识和工作原理; 3) 了解大规模可编程逻辑器件的基本使用方法。 作业内容: 理解大规模可编程逻辑器件的基本知识和工作原理,。 讨论内容: 可编程逻辑器件的编程方法和应用。 自学拓展: 回顾学过的数字电路相关知识,查阅可编程逻辑器件的数据手册。 3、 VHDL 设计初步(6 学时)(支撑课程目标 1) 3.1 组合逻辑电路的 VHDL 描述 3.2 基本时序电路的 VHDL 描述 3.3 计数器的 VHDL 描述 3.4 实用计数器的 VHDL 描述 目标及要求: 1) 掌握常用组合逻辑电路的程序设计方法; 2) 掌握基本时序逻辑电路的程序设计方法; 3) 掌握计数器的程序设计方法; 作业内容: 强化常用组合逻辑电路、触发器及计数器的程序设计。 讨论内容: 讨论传统的数字电路设计方法与 VHDL 设计方法。 自学拓展: 查阅资料,设计其他课程中未讲解的常用数字电路。 4、 QuartusⅡ的使用(3 学时)(支撑课程目标 3) 4.1 基本设计流程

4.2引脚设置与硬件验证 4.3原理图设计输入方法 ◇目标及要求: 1)掌握QuartusⅡ的设计流程★ 2)掌握QuartusⅡ的设计方法。 夕作业内容 强化对软件仿真平台的使用。 令自学拓展: 在自己的电脑上安装Quartus]Ⅱ并使用。 5、VHDL结构与要煮(6学时)(支撑课程目标1) 5.1VHDL程序结构 5.2VHDL语言要素 令目标及要求: 1)掌握VHDL的程序结构,主要是:实体,结构体,进程,库和程序包太: 2)掌握VHDL的语言要素,主要是:数据对象和数据类型★△: 令作业内容: 强化程序设计 令自学拓展: 编写程序。 6、VHDL基本语句(9学时)(支排课程目标1) 6.1顺序语句 6.2并行语句 63属性描述与定义语句 令目标及婴求 】)堂握顺序语句的结构及用法★ 2)掌操并行语句的结构及用法★: 3)了解属性描述与定义语句的用法 令作业内容: 强化使用顺序语句和并行语句进行程序设计的方法。 令自学拓展:

4.2 引脚设置与硬件验证 4.3 原理图设计输入方法 目标及要求: 1) 掌握 QuartusⅡ的设计流程; 2) 掌握 QuartusⅡ的设计方法。 作业内容: 强化对软件仿真平台的使用。 自学拓展: 在自己的电脑上安装 QuartusⅡ并使用。 5、 VHDL 结构与要素(6 学时)(支撑课程目标 1) 5.1 VHDL 程序结构 5.2 VHDL 语言要素 目标及要求: 1) 掌握 VHDL 的程序结构,主要是:实体,结构体,进程,库和程序包; 2) 掌握 VHDL 的语言要素,主要是:数据对象和数据类型; 作业内容: 强化程序设计。 自学拓展: 编写程序。 6、 VHDL 基本语句(9 学时)(支撑课程目标 1) 6.1 顺序语句 6.2 并行语句 6.3 属性描述与定义语句 目标及要求: 1) 掌握顺序语句的结构及用法; 2) 掌握并行语句的结构及用法; 3) 了解属性描述与定义语句的用法; 作业内容: 强化使用顺序语句和并行语句进行程序设计的方法。 自学拓展:

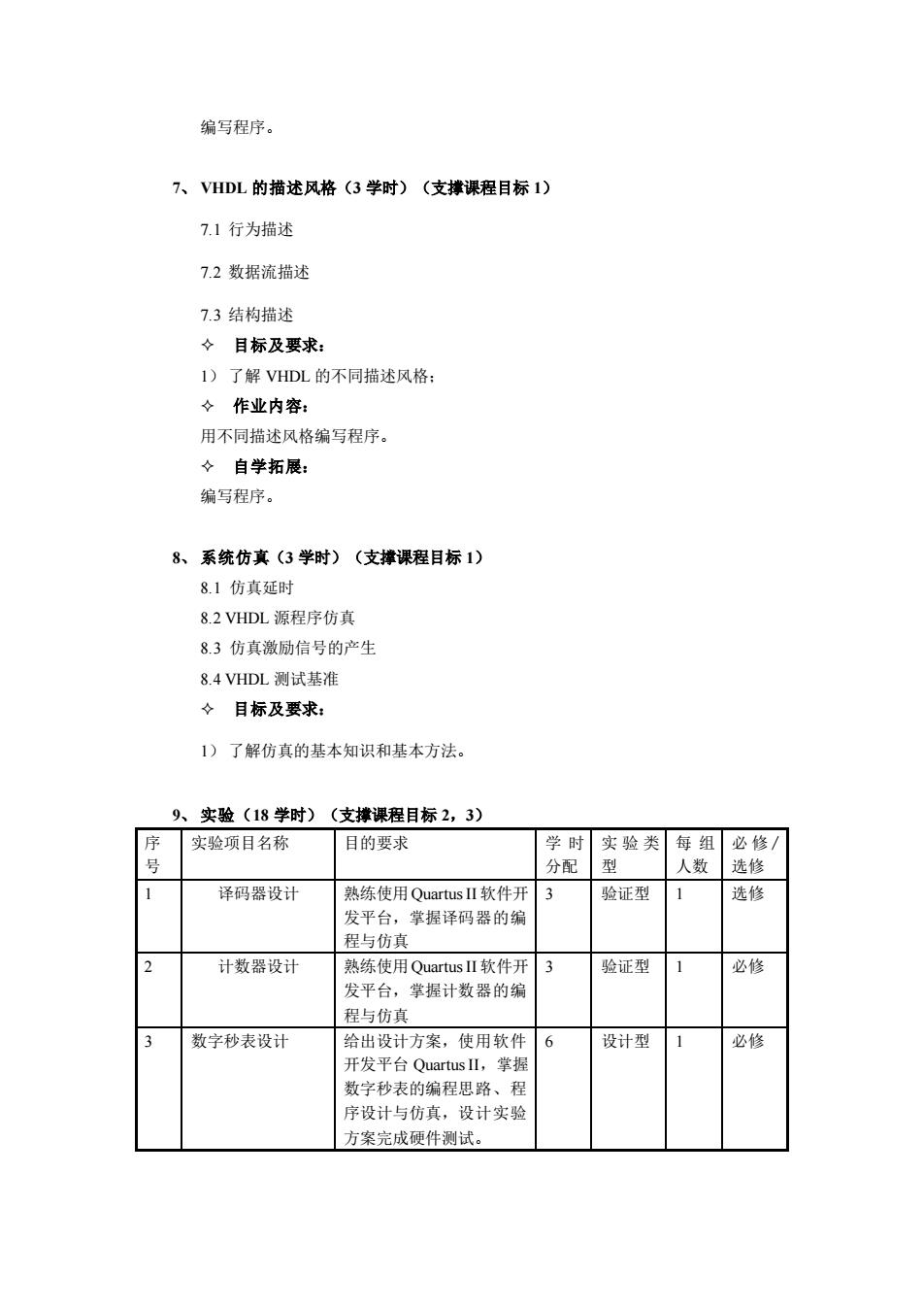

编写程序。 7、VHDL的描述风格(3学时)(支撑课程目标1) 7.1行为描述 7.2数据流描述 7.3结构描述 ◇目标及要求: 1)了解VHDL的不同描述风格: 女作业内容: 用不同描述风格编写程序。 令自学拓展: 编写程序。 8、系统仿真(3学时)(支撑课程目标1) 8.1仿真延时 82VHDL源程序仿真 83仿真激励信号的产生 84VHDL测试基准 令目标及要求: 1)了解仿真的基本知识和基本方法 9、实验(18学时)(支遭课程目标2,3) 实验项目名称 目的要求 学时实验类每组必修/ 号 分配型 人数选修 译码器设计 熟练使用QuartusⅡ软件开3 验证型 1 选修 发平 掌握译码器的编 程与仿真 计数器设计 熟练使用QuartusⅡ软件开3 验证型 必修 发平台,掌握计数器的编 程与仿真 数字秒表设计 给出设计方案,使用软件 6 设计型 必修 开发平台QuartusⅡ,掌握 数字秒表的综程思路、程 序设计与仿真,设计实验 方案完成硬件测试

编写程序。 7、 VHDL 的描述风格(3 学时)(支撑课程目标 1) 7.1 行为描述 7.2 数据流描述 7.3 结构描述 目标及要求: 1) 了解 VHDL 的不同描述风格; 作业内容: 用不同描述风格编写程序。 自学拓展: 编写程序。 8、 系统仿真(3 学时)(支撑课程目标 1) 8.1 仿真延时 8.2 VHDL 源程序仿真 8.3 仿真激励信号的产生 8.4 VHDL 测试基准 目标及要求: 1) 了解仿真的基本知识和基本方法。 9、 实验(18 学时)(支撑课程目标 2,3) 序 号 实验项目名称 目的要求 学 时 分配 实验类 型 每 组 人数 必 修 / 选修 1 译码器设计 熟练使用Quartus II 软件开 发平台,掌握译码器的编 程与仿真 3 验证型 1 选修 2 计数器设计 熟练使用Quartus II 软件开 发平台,掌握计数器的编 程与仿真 3 验证型 1 必修 3 数字秒表设计 给出设计方案,使用软件 开发平台 Quartus II,掌握 数字秒表的编程思路、程 序设计与仿真,设计实验 方案完成硬件测试。 6 设计型 1 必修

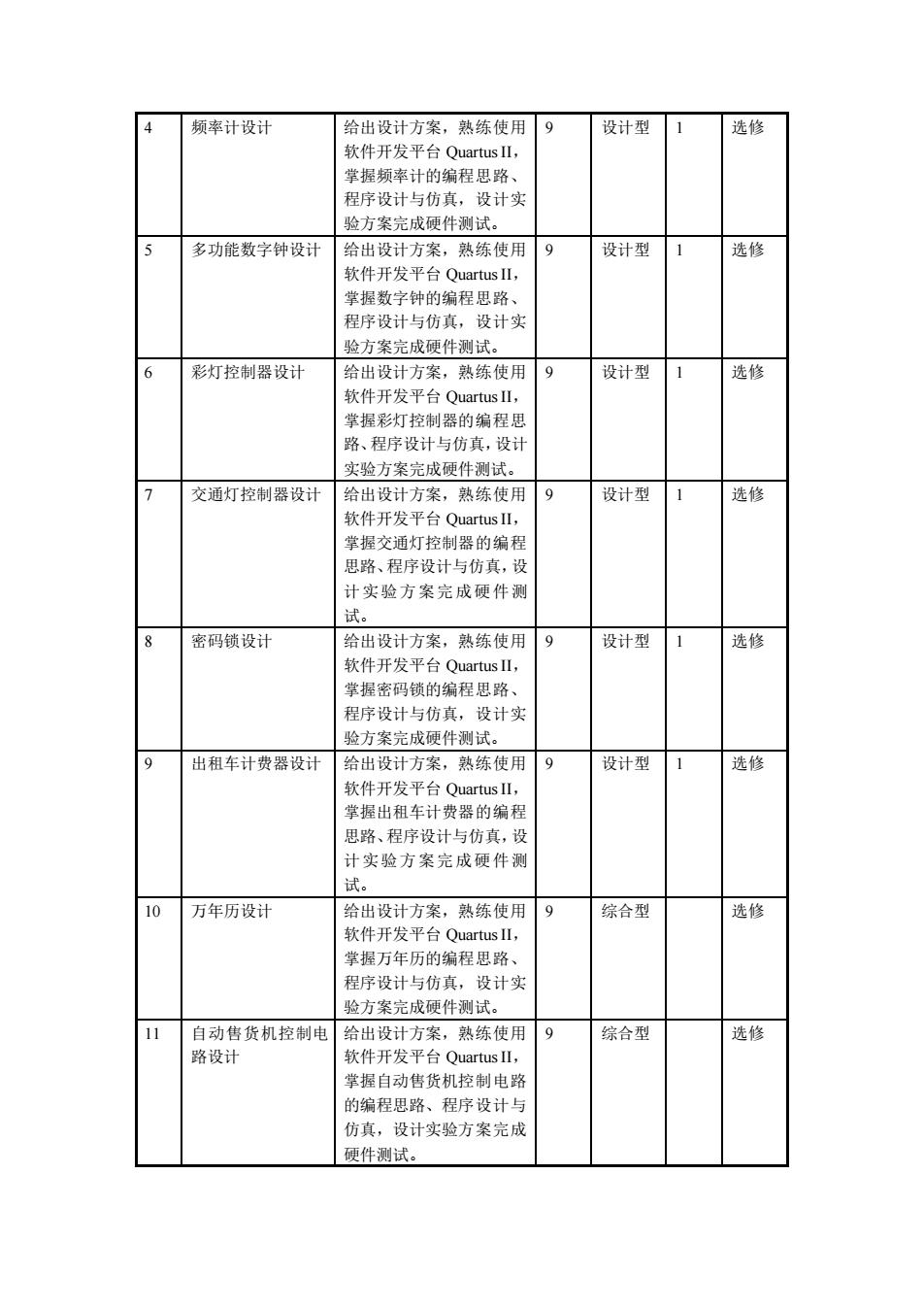

4 频率计设计 给出设计方案,熟练使用 设计型 1 选修 软件开发平台QuartusⅡ 掌握频率计的编程思路、 程序设计与仿真,设计实 哈方案完成硬件测试。 多功能数字钟设计 给出设计方案,熟练使用 设计型 选修 软件开发平台QuartusⅡ 掌握数字钟的编程思路 程序设计与仿真,设计实 验方案完成硬件测试。 6 彩灯控制器设计 给出设计方案,熟练使用 设计型 选修 软件开发平台Quartus II 掌棍彩灯控制器的编程思 路、程序设计与仿真,设计 实验方案完成硬件测试。 交通灯控制器设计 给出设计方案,熟练使用 设计型 选修 软件开发平台Quartus1I 掌握交通灯控制器的编程 思路、程序设计与仿直,设 计实验方案完成硬件测 试。 密码锁设计 给出设计方案,熟练使用 /9 设计型 选修 软件开发平台Quartus II. 掌握密码锁的编程思路、 程序设计与仿真,设计实 验方案完成硬件测试 9 出租车计费器设计 给出设计方案,熟练使用 设计型 1 迷修 软件开发平台Quartus IⅡ, 掌握出租车计费器的编程 思路、程序设计与仿直,设 计实验方案完成硬件测 10万年历设计 给出设计方案,熟练使用9 综合型 选修 软件开发平台Ouartus IⅡ. 堂挥万年历的绵程里路 程序设计与仿真,设计到 验方案完成硬件测试。 11自动售货机控制电给出设计方案,熟练使用 9 综合型 选修 路设计 软件开发平台Ouartus IⅡ, 掌握自动售货机控制电路 的编程思路、 程序设计 仿真,设计实验方案完成 硬件测试

4 频率计设计 给出设计方案,熟练使用 软件开发平台 Quartus II, 掌握频率计的编程思路、 程序设计与仿真,设计实 验方案完成硬件测试。 9 设计型 1 选修 5 多功能数字钟设计 给出设计方案,熟练使用 软件开发平台 Quartus II, 掌握数字钟的编程思路、 程序设计与仿真,设计实 验方案完成硬件测试。 9 设计型 1 选修 6 彩灯控制器设计 给出设计方案,熟练使用 软件开发平台 Quartus II, 掌握彩灯控制器的编程思 路、程序设计与仿真,设计 实验方案完成硬件测试。 9 设计型 1 选修 7 交通灯控制器设计 给出设计方案,熟练使用 软件开发平台 Quartus II, 掌握交通灯控制器的编程 思路、程序设计与仿真,设 计实验方案完成硬件测 试。 9 设计型 1 选修 8 密码锁设计 给出设计方案,熟练使用 软件开发平台 Quartus II, 掌握密码锁的编程思路、 程序设计与仿真,设计实 验方案完成硬件测试。 9 设计型 1 选修 9 出租车计费器设计 给出设计方案,熟练使用 软件开发平台 Quartus II, 掌握出租车计费器的编程 思路、程序设计与仿真,设 计实验方案完成硬件测 试。 9 设计型 1 选修 10 万年历设计 给出设计方案,熟练使用 软件开发平台 Quartus II, 掌握万年历的编程思路、 程序设计与仿真,设计实 验方案完成硬件测试。 9 综合型 选修 11 自动售货机控制电 路设计 给出设计方案,熟练使用 软件开发平台 Quartus II, 掌握自动售货机控制电路 的编程思路、程序设计与 仿真,设计实验方案完成 硬件测试。 9 综合型 选修

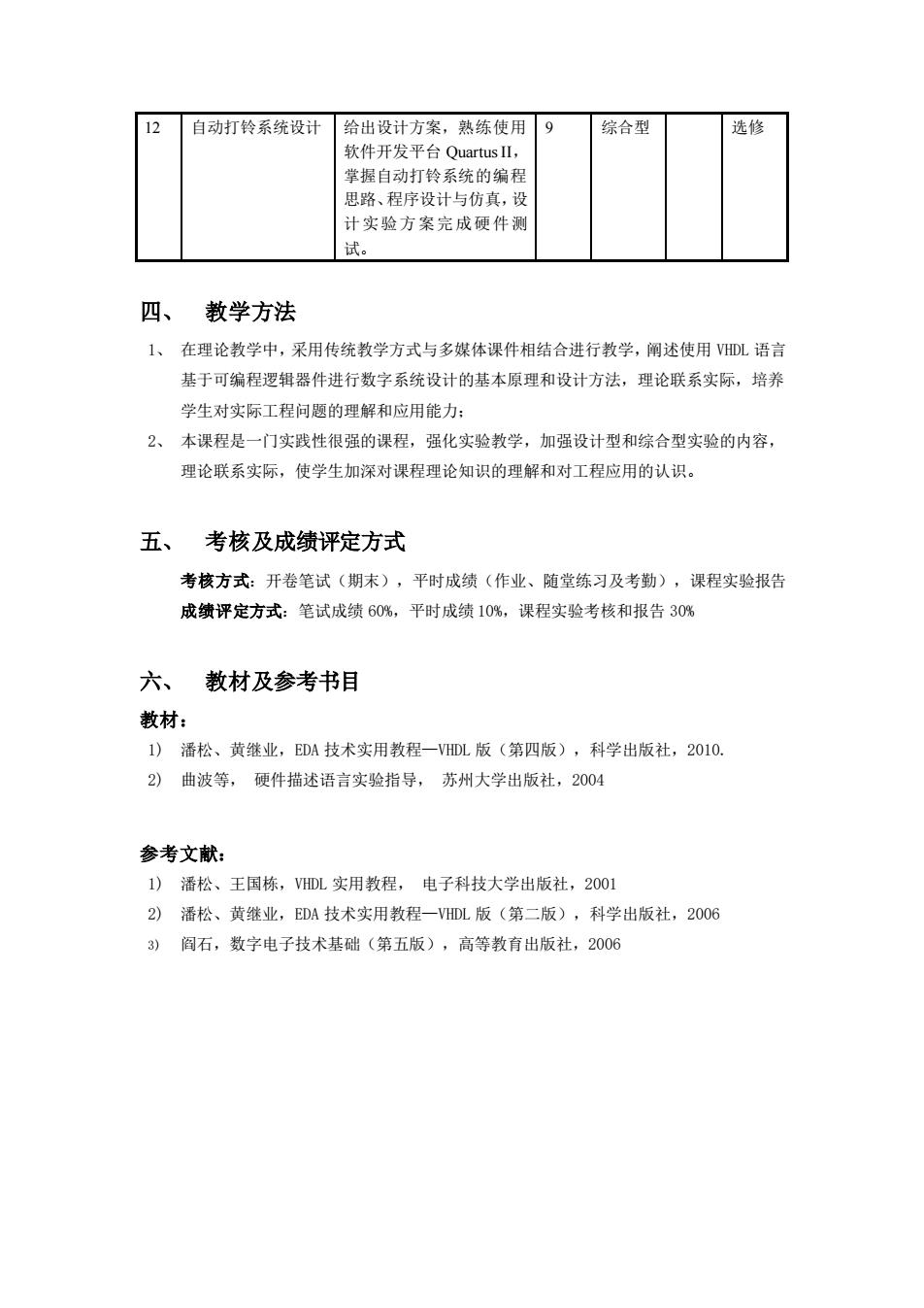

12 自动打铃系统设计 给出设计方案,熟练使用9 综合型 选修 软件开发 掌握自动打铃系统的编程 思路、程序设计与仿真,设 计实验方案完成硬件测 四、教学方法 1、在理论教学中,采用传统教学方式与多媒体课件相结合进行教学,阐述使用VHL语言 基于可编程逻辑器件进行数字系统设计的基本原理和设计方法,理论联系实际,培养 学生对实际工程问题的理解和应用能力: 2、本课程是一门实践性很强的课程,强化实验教学,加强设计型和综合型实验的内容, 理论联系实际,使学生加深对课程理论知识的理解和对工程应用的认识。 五、考核及成绩评定方式 考核方式:开卷笔试(期末),平时成绩(作业、随堂练习及考勤),课程实验报告 成绩评定方式:笔试成绩60%,平时成绩10%,课程实验考核和报告30% 六、教材及参考书目 教材: 1)潘松、黄继业,EDA技术实用教程一DL版(第四版),科学出版社,2010 2)曲波等,硬件描述语言实验指导,苏州大学出版社,2004 参考文献: 1)潘松、王国栋,HDL实用教程,电子科技大学出版社,2001 2)潘松、黄继业,EDA技术实用教程一VHDL版(第二版),科学出版社,20O6 3)阎石,数字电子技术基础(第五版),高等教有出版社,2006

12 自动打铃系统设计 给出设计方案,熟练使用 软件开发平台 Quartus II, 掌握自动打铃系统的编程 思路、程序设计与仿真,设 计实验方案完成硬件测 试。 9 综合型 选修 四、 教学方法 1、 在理论教学中,采用传统教学方式与多媒体课件相结合进行教学,阐述使用 VHDL 语言 基于可编程逻辑器件进行数字系统设计的基本原理和设计方法,理论联系实际,培养 学生对实际工程问题的理解和应用能力; 2、 本课程是一门实践性很强的课程,强化实验教学,加强设计型和综合型实验的内容, 理论联系实际,使学生加深对课程理论知识的理解和对工程应用的认识。 五、 考核及成绩评定方式 考核方式:开卷笔试(期末),平时成绩(作业、随堂练习及考勤),课程实验报告 成绩评定方式:笔试成绩 60%,平时成绩 10%,课程实验考核和报告 30% 六、 教材及参考书目 教材: 1) 潘松、黄继业,EDA 技术实用教程—VHDL 版(第四版),科学出版社,2010. 2) 曲波等, 硬件描述语言实验指导, 苏州大学出版社,2004 参考文献: 1) 潘松、王国栋,VHDL 实用教程, 电子科技大学出版社,2001 2) 潘松、黄继业,EDA 技术实用教程—VHDL 版(第二版),科学出版社,2006 3) 阎石,数字电子技术基础(第五版),高等教育出版社,2006