试卷代号:1011 座位号口 中央广播电视大学2007一2008学年度第一学期“开放本科”期末考试 计算机专业计算机组成原理 试题 2008年1月 题 号 一 二 三 四 分 总 分 数 得 分 评卷人 一、选择题(每小题3分,共30分) 1.冯·诺依曼机工作方式的基本特点是( A.多指令流单数据流 B.按地址访问并顺序执行指令 C.堆栈操作 D.存储器按内部选择地址 2.计算机系统中的存储器系统是指 ,没有外部存储器的计算机监控程序可以存 放在 中。() A.RAM,CPU B.ROM,RAM C.主存储器,RAM和ROM D.主存储器和外存储器,ROM 3.某机字长16位,采用定点小数表示,符号位为1位,尾数为15位,则可表示的最大正 小数为 ,最小负小数为 。() A.+(216-1),-(1-215) B.+(215-1),-(1-2-6) C.+(1-26),-(1-2-16) D.+(21-1),-(1-215) 4.在定点数运算中产生溢出的原因是( A.运算过程中最高位产生了进位或借位 B.参加运算的操作数超出了机器的表示范围 C.运算的结果的操作数超出了机器的表示范围 D.寄存器的位数太少,不得不舍弃最低有效位 75

试卷代号 :1011 座位号口口 中央广播电视大学2007-2008学年度第一学期“开放本科”期末考试 计算机专业 计算机组成原理 试题 2008年 1月 题 号 四 总 分 分 数 得 分 评卷人 一、选择题(每小题 3分,共 30分) 1.冯 ·诺依曼机工作方式的基本特点是( )。 A.多指令流单数据流 B.按地址访问并顺序执行指令 C.堆栈操作 D.存储器按内部选择地址 2.计算机系统中的存储器系统是指 ,没有外部存储器的计算机监控程序可以存 放在 中。( ) A. RAM,CPU B. ROM ,RAM C.主存储器,RAM 和 ROM D.主存储器和外存储器,ROM 3.某机字长 16位,采用定点小数表示,符号位为 1位,尾数为 ]:,位,则可表示的最大正 小数为 ,最小负小数为 。( ) A. -f- ( 2' 6一1),一(1一2一‘}) F3.十(2}5一1),一(1一2一‘e} C. -r- (1一2一‘5),一(1一2一“) D. -I- ( 2 `j一l),一(1一2一‘s} 4.在定点数运算中产生溢出的原因是( )。 A.运算过程中最高位产生了进位或借位 B.参加运算的操作数超出了机器的表示范围 C.运算的结果的操作数超出了机器的表示范围 n.寄存器的位数太少,不得不舍弃最低有效位

5.间接寻址是指()。 A.指令中直接给出操作数地址 B.指令中直接给出操作数 C.指令中间接给出操作数 D.指令中间接给出操作数地址 6.输入输出指令的功能是()。 A.进行算术运算和逻辑运算 B.进行主存与CPU之间的数据传送 C.进行CPU和I/O设备之间的数据传送 D.改变程序执行的顺序 7.某计算机的字长是8位,它的存储容量是64KB,若按字编址,那么它的寻址范围应该 是( A.0-128K B.0-64K C.0-32K D.0--16K 8.若主存每个存储单元为16位,则( )。 A.其地址线也为16位 B.其地址线与16无关 C.其地址线为8位 D.其地址线与16有关 9.在计算机I/O系统中,在用DMA方式传送数据时,DMA控制器应控制()。 A.地址总线 B.数据总线 C,控制总线 D.以上都是 10.在计算机总线结构的单机系统中,三总线结构的计算机的总线系统由( )组成。 A.系统总线、内存总线和I/O总线 B.数据总线、地址总线和控制总线 C.内部总线、系统总线和/O总线 D.ISA总线、VESA总线和PCI总线 76

5.间接寻址是指( )。 A.指令中直接给出操作数地址 B.指令中直接给出操作数 C.指令中间接给出操作数 D.指令 中间接给出操作数地址 G.输入输 出指令 的功能是 ( )。 A.进行算术运算和逻辑运算 B.进行主存与 CPU之间的数据传送 C.进行 CPU和 I/O设备之间的数据传送 D.改变程序执行的顺序 7.某计算机的字长是8位,它的存储容量是64KI3,若按字编址,那么它的寻址范围应俄 是 ( A.0- 128 K I3. 0- 64 K C. 0- 32K D. U一 16K 8.若主存每个存储单元为 16位 ,则 ( )。 A.其地址线也为 16位 B。其地址线与 16无关 C.其地址线为 8位 D.其地址线与 16有关 9.在计算机 I/O系统中,在用 DMA方式传送数据时,DMA控制器应控制( )。 A.地址总线 B.数据总线 C.控制总线 D.以上都是 10.在计算机总线结构的单机系统中,三总线结构的计算机的总线系统由( )组成。 A.系统总线、内存总线和 I/O总线 B.数据总线 、地址总线和控制总线 C.内部总线 、系统总线和 I/C)总线 D. 1SA总线 、VE5A总线和 r}Ci总线

得分 评卷人 二、填空题(每空2分,共32分) 1.主频是计算机的一个重要指标,它的单位是 :运算速度的单位是MIPS, 也就是 2.十进制到二进制的转换,通常要区分数的 部分和 部分,并分别 按 和 部分两种不同的方法来完成。 3.寻址方式要解决的问题是如何在指令中表示一个操作数的地址,如何用这种表示得到 操作数、或怎样计算出操作数的地址。表示在指令中的操作数地址通常被称为 ;用这种形式地址并结合某些规则,可以计算出操作数在存储器中的存储单元地址,这 一地址被称为数据的 4.三级不同的存储器,是用读写速度不同、存储容量不同、运行原理不同、管理使用方法 也不尽相同的不同存储器介质实现的。高速缓冲存储器使用 实 现,主存储器使用 实现,而虚拟存储器则使用 上的一片存储区。 5.在计算机主机和【/O设备之间,可以采用不同的控制方式进行数据传送。通常分为以 下五种方式,即 和 得 分 评卷人 三、计算题(共28分】 1.写出X=10111101,Y=一00101011的双符号位原码、反码、补码表示,并用双符号补 码计算两个数的差。(每空2分,共18分) 原码 反码 补码 X=10111101 Y=-00101011 X-Y 77

得 分 评卷人 二、填空题 (每空 2分,共 32分) 1.主频是计算机的一个重要指标,它的单位是_ ;运算速度的单位是MIPS, 也就是 2.十进制到二进制的转换,通常要区分数的 部分和 部分,并分别 按 和 部分两种不同的方法来完成。 3.寻址方式要解决的问题是如何在指令 中表示一个操作数 的地址 ,如何用这种表示得到 操作数、或怎样计算出操作数的地址。表示在指令中的操作数地址通常被称为 ;用这种形式地址并结合某些规则 ,可以计算出操作数在存储器 中的存储单元地址 ,这 一地址被称为数据的 4.三级不同的存储器,是用读写速度不同、存储容量不 同、运行原理不同 也不尽相同的不同存储 器介质实现的。高速缓冲存储器使用 、管理使用方法 实 现 ,主存储 器使用 实现 ,而虚拟存储 器则 使用 上的一片存储区。 J.在计算机主机和 I/O设备之间,可以采用不同的控制方式进行数据传送 。通常分为以 下五种方式,即 、 _ ______ ___ 和 得 分 评卷人 三、计算题 (共 28分) 写出X= 10111101 , Y=一。0101011的双符号位原码、反码、补码表示,并用双符号补 码计算两个数的差。(每空 2分,共 18分) 原 码 反 码 补 码 X= 10111101 Y= 一00101011 X一 Y

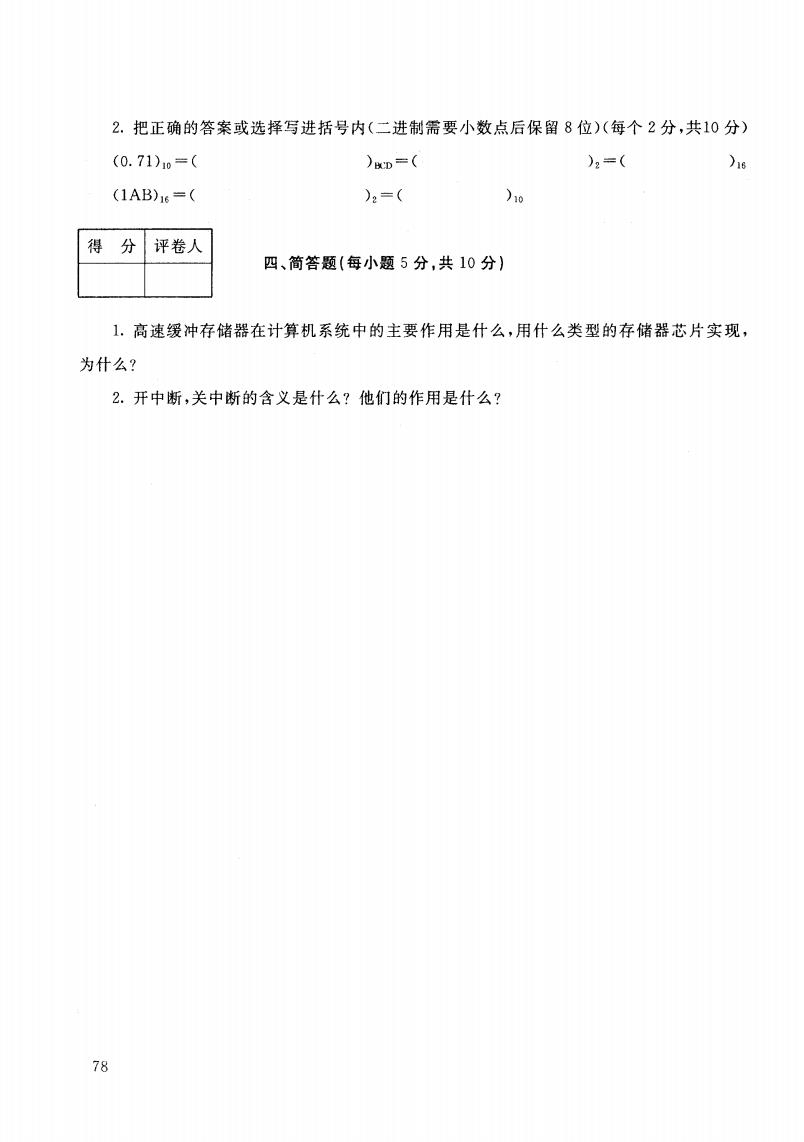

2.把正确的答案或选择写进括号内(二进制需要小数点后保留8位)(每个2分,共10分) (0.71)1o=( )D=( )2=( )16 (1AB)16=( )2=( )40 得分 评卷人 四、简答题(每小题5分,共10分) 1.高速缓冲存储器在计算机系统中的主要作用是什么,用什么类型的存储器芯片实现, 为什么? 2.开中断,关中断的含义是什么?他们的作用是什么? 78

2.把正确的答案或选择写进括号内(二进制需要小数点后保 留 8位)(每个 2分,共 10分) }}" 11)10=( )d(:D -( }Z=( ),。 (lAl}}l6=( }2=( }10 得 分 评卷人 四、简答题(每小题 5分 .共 1}分 ) 1.高速缓冲存储器在计算机系统中的主要作用是什么 ,用什么类 型的存储 器芯片实现, 为什么? 2.开中断,关中断的含义是什么?他们 的作用是什么?

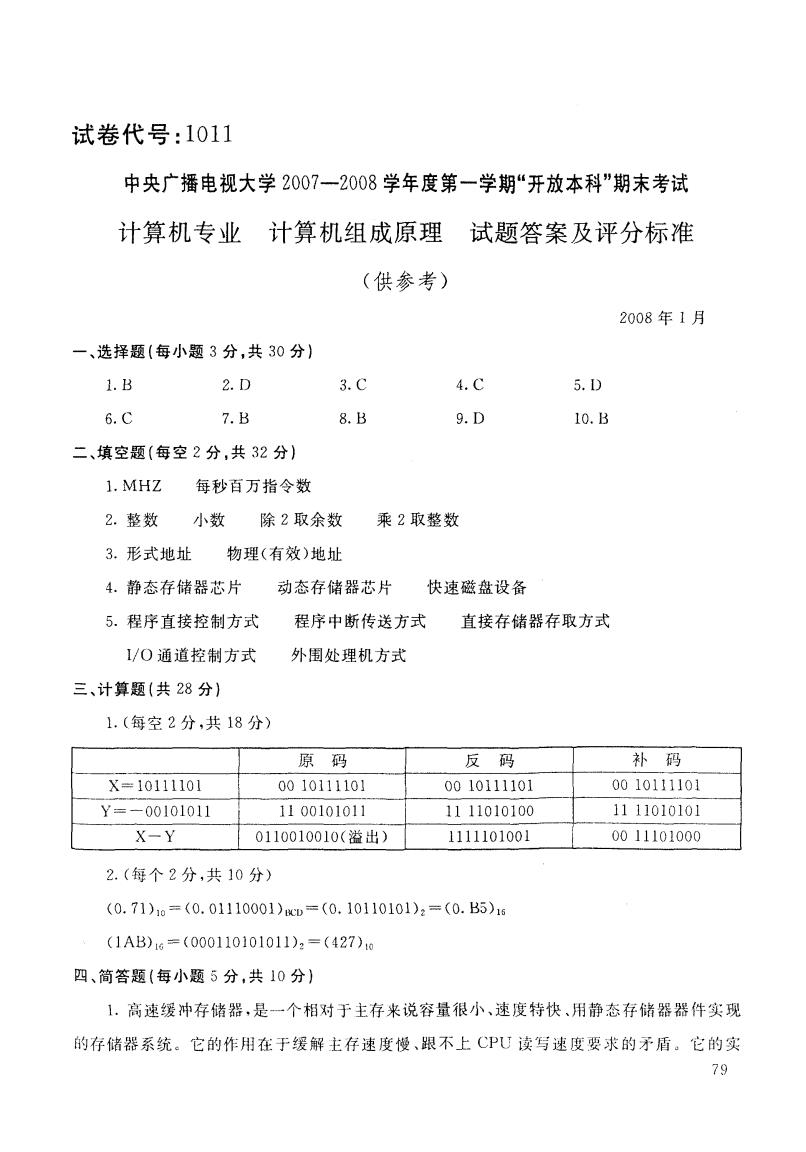

试卷代号:1011 中央广播电视大学2007一2008学年度第一学期“开放本科”期末考试 计算机专业计算机组成原理试题答案及评分标准 (供参考) 2008年1月 一、选择题(每小题3分,共30分) 1.B 2.D 3.C 4.C 5.D) 6.C 7.B 8.B 9.D 10.B 二、填空题(每空2分,共32分) 1.MHZ 每秒百万指令数 2.整数 小数 除2取余数 乘2取整数 3.形式地址 物理(有效)地址 4.静态存储器芯片 动态存储器芯片 快速磁盘设备 5.程序直接控制方式 程序中断传送方式 直接存储器存取方式 L/O通道控制方式 外围处理机方式 三、计算题(共28分)】 1.(每空2分,共18分) 原码 反码 补码 X=10111101 0010111101 0010111101 0010111101 Y=-00101011 1100101011 1111010100 1111010101 X-Y 0110010010(溢出) 1111101001 0011101000 2.(每个2分,共10分)》 (0.71)10=(0.01110001)cD=(0.10110101)2=(0.B5)16 (1AB)16=(000110101011)2=(427)10 四、简答题(每小题5分,共10分)】 1.高速缓冲存储器,是一个相对于主存来说容量很小、速度特快、用静态存储器器件实现 的存储器系统。它的作用在于缓解主存速度慢、跟不上CPU读写速度要求的矛盾。它的实 79

试卷代号:1011 中央广播电视大学200-2008学年度第一学期“开放本科”期末考试 计算机专业 计算机组成原理 试题答案及评分标准 (供参考) 200 年 1月 一、选择题(每小题 3分,共 30分) 1. I3 2.D 3.C 4.C 5.U 6.C 7. I3 S. I3 9.D 10.13 二、填 空题 (每空 2分 ,共 32分) 1. MHZ 每秒百万指令数 2.整数 小数 除 2取余数 乘 2取整数 3.形式地址 物理(有效)地址 4.静态存储器芯片 动态存储器芯片 快速磁盘设备 5.程序直接控制方式 程序中断传送方式 直接存储器存取方式 I/O通道控制方式 外围处理机方式 三、计算题 (共 28分) l.(每空 2分 ,共 18分) X= 10111101 Y= 一 00101011 X一 Y 原 码 00 10111101 11 00101011 0110010010(溢出) 反 码 00 10111101 11 11010100 1111101001 补 码 00 10111101 11 11010101 00 11101000 2 (每个 2分 ,共 10分) (0. 71),0={0.01110001)i} n=(0.10110141):=CO. 13})1s (1 A13) io -- 0000110101011):= 0427):。 四、简答题(每小题 5分,共 10分) 卜高速缓冲存储器,是一个相对于主存来说容量很小、速度特快、川静态存储器器件实现 的存储器系统。它的作用在于缓解主存速度慢、跟不上 CPt?读写速度要求的矛盾。它的实 79

现原理,是把CPU最近最可能用到的少量信息(数据或指令)从主存复制到CACHE中,当 CPU下次再用这些信息时,它就不必访问慢速的主存,而直接从快速的CACHE中得到,从而 提高了得到这些信息的速度,使CPU有更高的运行效率。 2.通常是在CPU内部设置一个“中断允许”触发器,只有该触发器被置为“1”状态,才允 许CPU响应中断请求,该触发器被置为“o”状态,则禁止CPU响应中断请求。为此,在指令 系统中,为操作“中断允许”触发器,应设置“开中断”指令(置“1”中断允许触发器)和“关中断” 指令(清“0”中断允许触发器)。 80

现原理,是把 CPU最近最可能用到的少量信息(数据或指令)从主存复制到 CACHE中,当 CPU下次再用这些信息时,它就不必访问慢速的主存,而直接从快速的 CACHE中得到,从而 提高了得到这些信息的速度,使 C}'U有更高的运行效率。 2。通常是在 CPU内部设置一个“中断允许”触发器,只有该触发器被置为“1”状态,才允 许 CPU响应中断请求,该触发器被置为“0”状态,则禁止 CPU响应中断请求。为此,在指令 系统中,为操作“中断允许”触发器,应设置“开中断”指令(置“1"中断允许触发器)和“关中断” 指令(清“0”中断允许触发器 )