R 第4章 8088的总线操作和时序 4.18088处理器 ● 8088CPU是PCXT微型计算机的核心部件 8088CPU可应用于各种规模的智能控制系统 808CPU具有最大模和最小模式,以及内置的 多任务处理能力 8088CPU具有40个引脚,某些引脚具有双功能 i Lin University China CpTE型CIENCE AND T厘CHNDOLOGY

COMPUTER SCIENCE AND TECHNOLOGY COMPUTER SCIENCE AND TECHNOLOGY 第4章 8088的总线操作和时序 4.1 8088处理器 • 8088 CPU是PC/XT微型计算机的核心部件 • 8088 CPU可应用于各种规模的智能控制系统 • 8088 CPU具有最大模和最小模式,以及内置的 多任务处理能力 • 8088 CPU具有40个引脚,某些引脚具有双功能

4.1最小的8088系统 上 最小配置下仅需4片外围芯片即可构成典型应用系统 地址 定时器 CL OCK 数据 TIMER 8088 CPU 控刺 口A 8755A EPROM 端口B I/O 8284 8185 时钟 K×8 发生委 RAM Ji Lin University China COMPUTER SCIENCE AND TECHNOLOGY

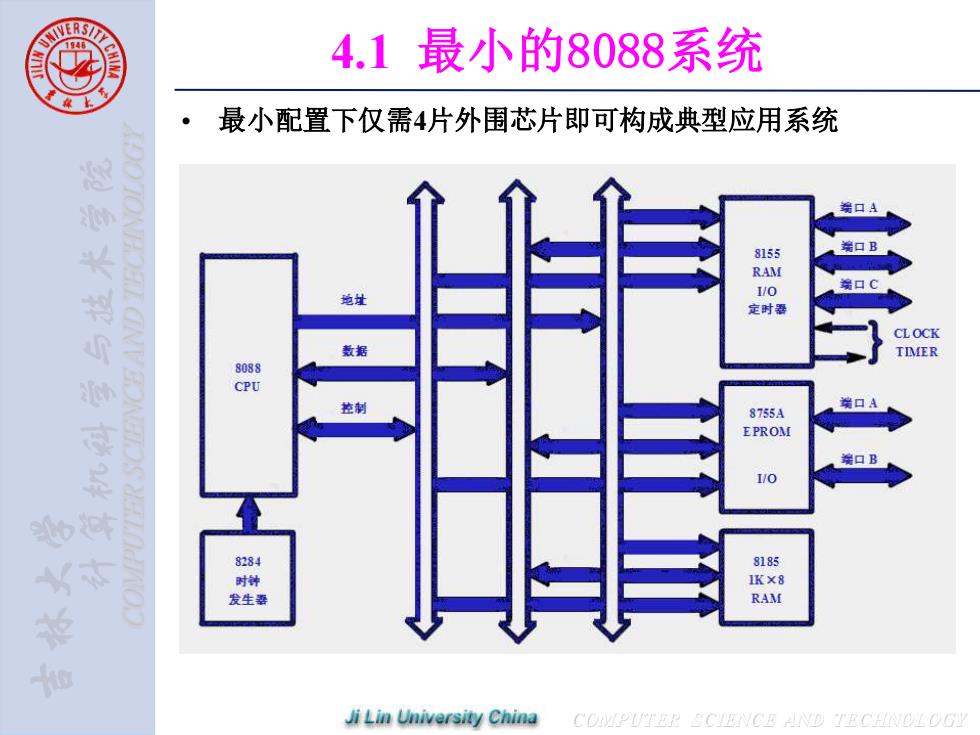

COMPUTER SCIENCE AND TECHNOLOGY COMPUTER SCIENCE AND TECHNOLOGY 4.1 最小的8088系统 • 最小配置下仅需4片外围芯片即可构成典型应用系统

8088处理器引脚 (1) 8088和8086CPU都 GND Vcc 具有40条引脚,采 A15 Aid/S3 用双列直插式封装 A7/S 为了减少芯片的引 线,8088的许多引 脚具有双重定义和 功能,采用分时复 AD6 用方式工作,即在 s 不同时刻,这些引 AD 线上的信号是不相 同的 5 8088的最大和最小 ADo 12345678901234567890 4439876543250 A1s/Ss A19/S6 SSo HIGH MN/M区 RD HOLD HLDA (RQ/GT) W丞 (RQ/GT) 93765432 IO/M (LOCK) DT/R ( S) DEN ( ALE ) NMI INTA (QSo) 两种工作模式可以 TEST (QS1) 通过引脚选择 READY GND 1 RESET Ji Lin University China COMPUTER SCIENCE山NY厘CHNOLOG

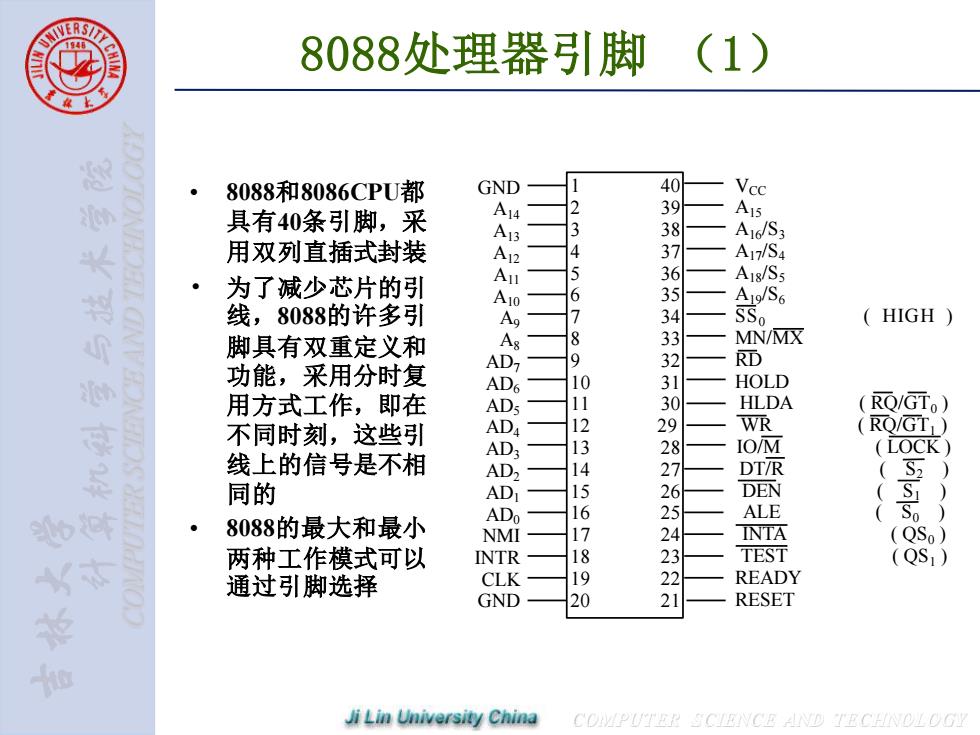

COMPUTER SCIENCE AND TECHNOLOGY COMPUTER SCIENCE AND TECHNOLOGY 8088处理器引脚 (1) • 8088和8086CPU都 具有40条引脚,采 用双列直插式封装 • 为了减少芯片的引 线,8088的许多引 脚具有双重定义和 功能,采用分时复 用方式工作,即在 不同时刻,这些引 线上的信号是不相 同的 • 8088的最大和最小 两种工作模式可以 通过引脚选择 1 40 2 39 3 38 4 37 5 36 6 35 7 34 8 33 9 32 10 31 11 30 12 29 13 28 14 27 15 26 16 25 17 24 18 23 19 22 20 21 GND A14 A13 A12 A11 A10 A9 A8 AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0 NMI INTR CLK GND VCC A15 A16/S3 A17/S4 A18/S5 A19/S6 S S0 ( HIGH ) MN/MX RD HOLD HLDA ( RQ/GT0 ) WR ( RQ/GT1 ) IO/M ( LOCK ) DT/R ( S2 ) DEN ( S1 ) ALE ( S0 ) INTA ( QS0 ) TEST ( QS1 ) READY RESET

8088处理器引脚(2) 上 最小模式下的引线(MN/MX=1) A16一A1g/S3~S6,地址、状态复用的引脚,三态 输出。在8088执行指令过程中,某一时刻从这4 个引脚上送出地址的最高4位A16~A1g,而在另外 时刻,这4个引脚送出状态信号$3~S6 这些状态信息中,S恒等于0,S5指示中断允 许标志位IF的状态,S4、Sg的组合指示CPU当前 正在使用的段寄存器,其编码见表 Ji Lin University China COMPUTER SCIENCE AND TECHNOLOGY

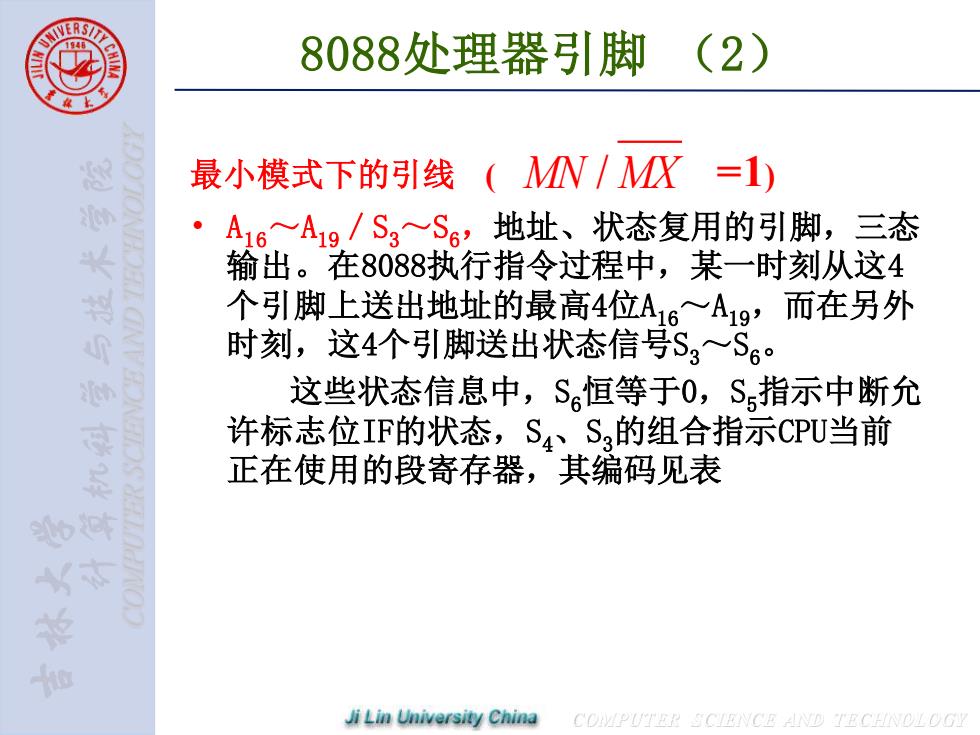

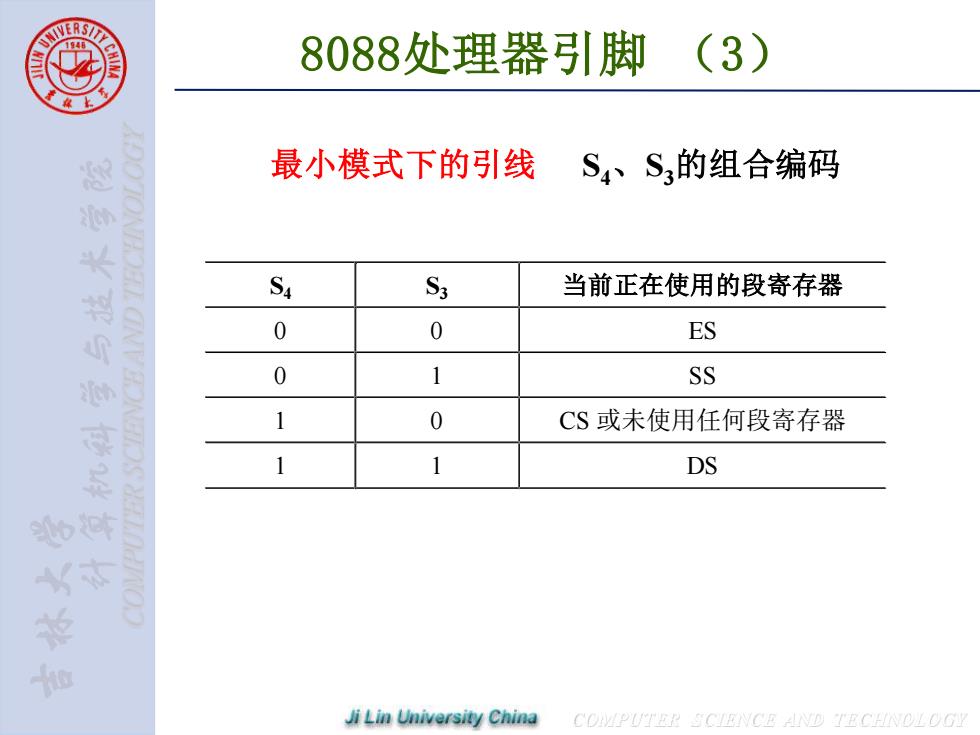

COMPUTER SCIENCE AND TECHNOLOGY COMPUTER SCIENCE AND TECHNOLOGY 8088处理器引脚 (2) 最小模式下的引线 ( =1) • A16 ~A19/S3 ~S6,地址、状态复用的引脚,三态 输出。在8088执行指令过程中,某一时刻从这4 个引脚上送出地址的最高4位A16 ~A19,而在另外 时刻,这4个引脚送出状态信号S3 ~S6。 这些状态信息中,S6恒等于0,S5指示中断允 许标志位IF的状态,S4、S3的组合指示CPU当前 正在使用的段寄存器,其编码见表 MN / MX

8088处理器引脚 (3) 最小模式下的引线 S,的组合编码 S4 S 当前正在使用的段寄存器 0 0 ES 0 1 SS 1 0 CS或未使用任何段寄存器 1 1 DS i Lin University China CpTE型CIENCE AND T室CHNOLOGY

COMPUTER SCIENCE AND TECHNOLOGY COMPUTER SCIENCE AND TECHNOLOGY 8088处理器引脚 (3) 最小模式下的引线 S4、S3的组合编码 S4 S3 当前正在使用的段寄存器 0 0 ES 0 1 SS 1 0 CS 或未使用任何段寄存器 1 1 DS

8088处理器引脚 (4) 最小模式下的引线 A15~Ag,地址输出,三态。CPU寻址内存或接口 时,从这些引脚送出地址A15~Ag AD,AD,地址、数据分时复用的双向信号线, 三态。当ALE=1时,这些引脚上传输的是地址信 号。当ALE=O时,这些引脚上传输的是数据信号 Ji Lin University China COMPUTER SCIENCE AND TECHNOLOGY

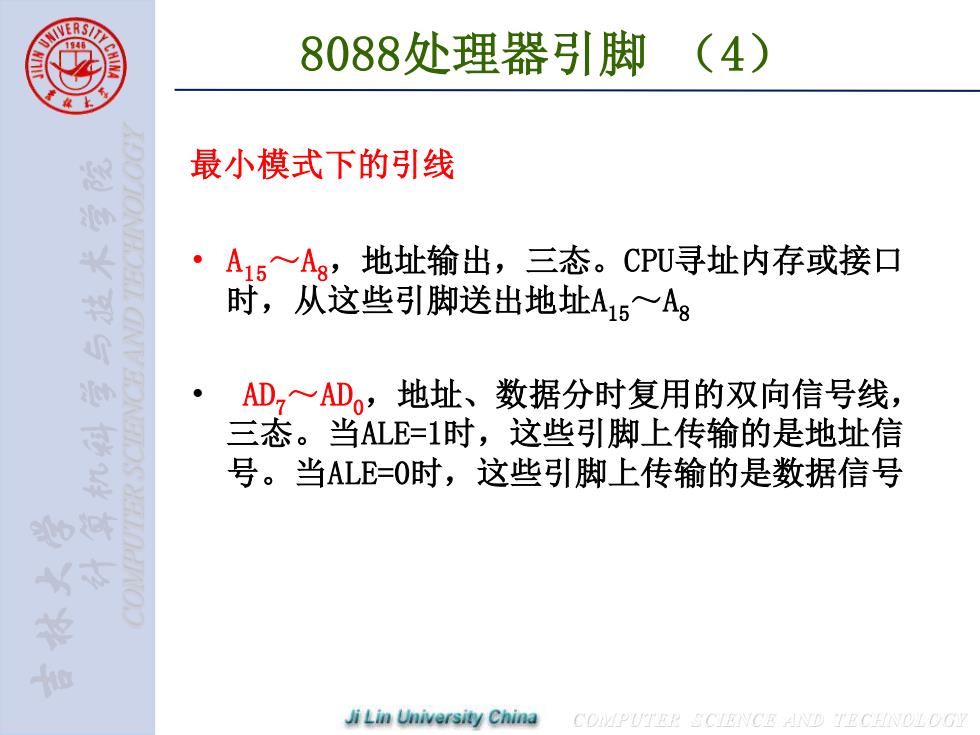

COMPUTER SCIENCE AND TECHNOLOGY COMPUTER SCIENCE AND TECHNOLOGY 8088处理器引脚 (4) 最小模式下的引线 • A15 ~A8,地址输出,三态。CPU寻址内存或接口 时,从这些引脚送出地址A15 ~A8 • AD7 ~AD0,地址、数据分时复用的双向信号线, 三态。当ALE=1时,这些引脚上传输的是地址信 号。当ALE=0时,这些引脚上传输的是数据信号

8088处理器引脚 (5) 最小模式下的引线 IO/M输入输出/存储器控制信号,三态,用来 区分当前操作是访问存储器还是访问I/0端口。 若此引脚输出为低电平,访问存储器;若输出为 高电平,则是访问I/0端口 。 WR写信号输出,三态。此引脚输出为低电平 时,表示CPU正在对存储器或I/O端口进行写操 作 i Lin University China CpTE型CIENCE AND T厘CHNDOLOGY

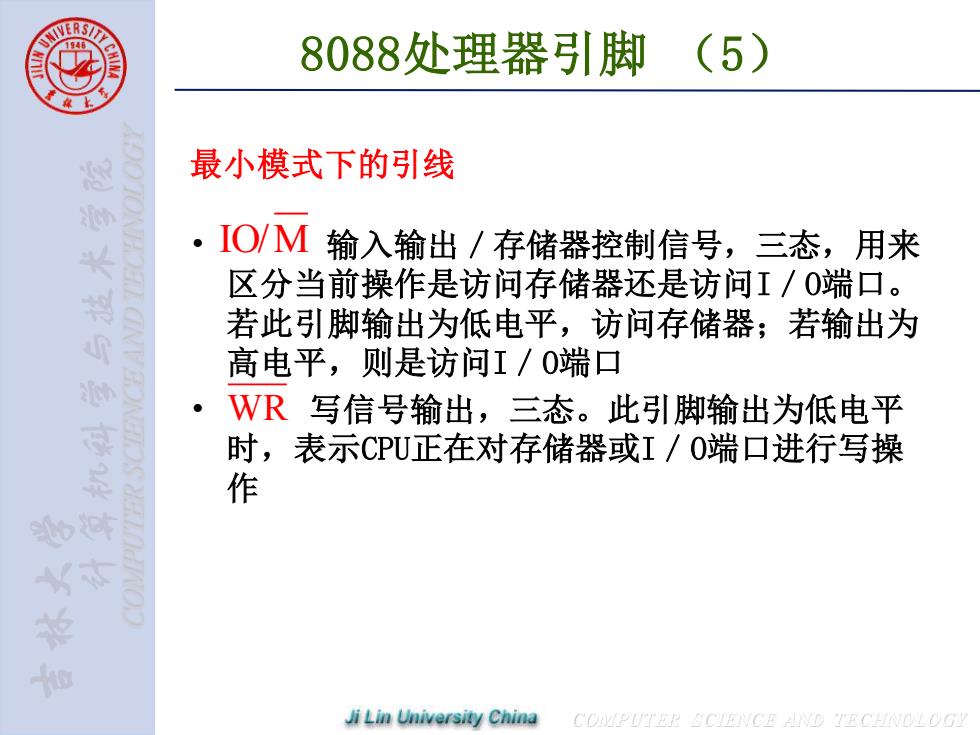

COMPUTER SCIENCE AND TECHNOLOGY COMPUTER SCIENCE AND TECHNOLOGY 8088处理器引脚 (5) 最小模式下的引线 • 输入输出/存储器控制信号,三态,用来 区分当前操作是访问存储器还是访问I/O端口。 若此引脚输出为低电平,访问存储器;若输出为 高电平,则是访问I/O端口 • 写信号输出,三态。此引脚输出为低电平 时,表示CPU正在对存储器或I/O端口进行写操 作 IO/M WR

8088处理器引脚 (6) 最小模式下的引线 。 DT/R数据传送方向控制信号,三态,用于确定 数据传送的方向。高电平时,CPU向存储器或I/ 0端口发送数据;低电平时,CPU从存储器或I/0 端口接收数据。此信号用于控制总线收发器 74LS245的传送方向 DEW数据允许信号,三态。该信号有效时,表 示数据总线上有有效数据。它在每次访问内存或 I/0端口以及在中断响应期间有效。它常用作数 据总线驱动器的片选信号 Ji Lin University China COMPUTER SCIENCE AND TECHNOLOGY

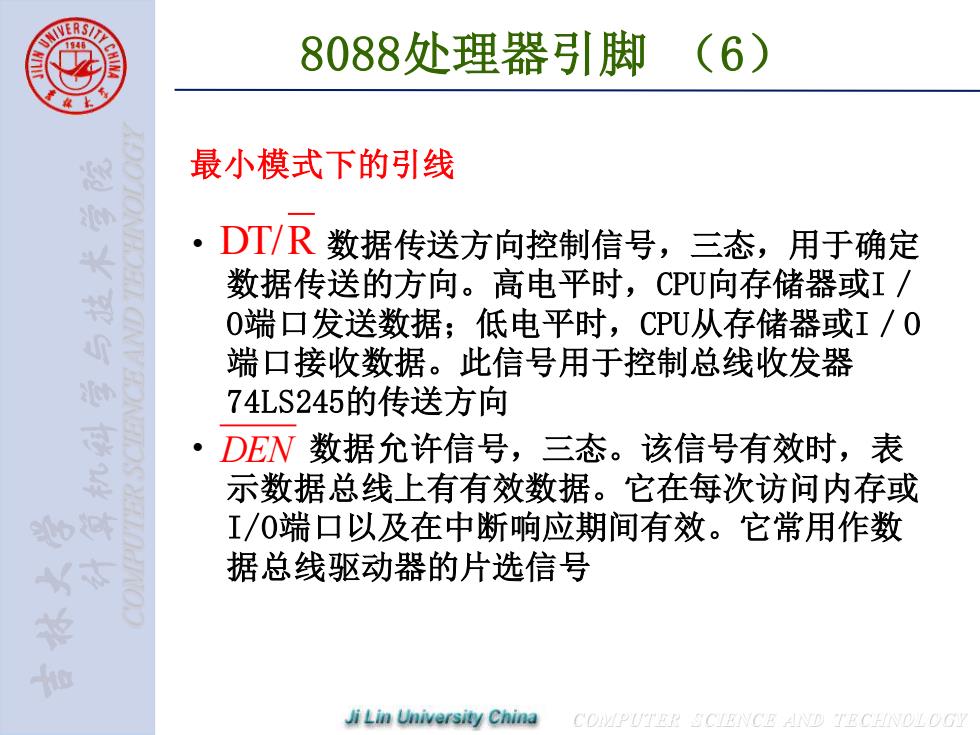

COMPUTER SCIENCE AND TECHNOLOGY COMPUTER SCIENCE AND TECHNOLOGY 8088处理器引脚 (6) 最小模式下的引线 • 数据传送方向控制信号,三态,用于确定 数据传送的方向。高电平时,CPU向存储器或I/ O端口发送数据;低电平时,CPU从存储器或I/O 端口接收数据。此信号用于控制总线收发器 74LS245的传送方向 • 数据允许信号,三态。该信号有效时,表 示数据总线上有有效数据。它在每次访问内存或 I/O端口以及在中断响应期间有效。它常用作数 据总线驱动器的片选信号 DT/R DEN

8088处理器引脚 (7) 最小模式下的引线 ALE地址锁存允许信号,三态输出,高电平有效。 当它为高电平时,表明CPU地址线上有有效地址。 因此,它常作为锁存控制信号将A1g~A,锁存到地 址锁存器 RD数据允许信号,三态。该信号有效时,表 示数据总线上有有效数据。它在每次访问内存或 I/0端口以及在中断响应期间有效。它常用作数 据总线驱动器的片选信号 i Lin University China CpTE型CIENCE AND T厘CHNDOLOGY

COMPUTER SCIENCE AND TECHNOLOGY COMPUTER SCIENCE AND TECHNOLOGY 8088处理器引脚 (7) 最小模式下的引线 • ALE 地址锁存允许信号,三态输出,高电平有效。 当它为高电平时,表明CPU地址线上有有效地址。 因此,它常作为锁存控制信号将A19 ~A0锁存到地 址锁存器 • 数据允许信号,三态。该信号有效时,表 示数据总线上有有效数据。它在每次访问内存或 I/O端口以及在中断响应期间有效。它常用作数 据总线驱动器的片选信号 RD

8088处理器引脚 (8) 最小模式下的引线 READY准备好信号输入引脚,高电平有效。它是 由被访问的内存或I/0设备发出的响应信号,当 其有效时,表示存储器或I/0设备已准备好, CPU可以进行数据传送。 若存储器或I/O设备没准备好,则使READY 信号为低电平。CPU在T,周期采样READY信号,若 其为低,CPU自动插入等待周期T.(1个或多个), 直到READY?变为高电平后,CPU才脱离等待状态, 完成数据传送过程。 Ji Lin University China COMPUTER SCIENCE AND TECHNOLOGY

COMPUTER SCIENCE AND TECHNOLOGY COMPUTER SCIENCE AND TECHNOLOGY 8088处理器引脚 (8) 最小模式下的引线 • READY 准备好信号输入引脚,高电平有效。它是 由被访问的内存或I/O设备发出的响应信号,当 其有效时,表示存储器或I/O设备已准备好, CPU可以进行数据传送。 若存储器或I/O设备没准备好,则使READY 信号为低电平。CPU在T3周期采样READY信号,若 其为低,CPU自动插入等待周期TW(1个或多个), 直到READY变为高电平后,CPU才脱离等待状态, 完成数据传送过程