计数器及其应用 一、实验目的 1.学习用集成触发器构成计数器的方法 2.掌握集成计数器的使用及功能测试 二、实验仪器和设备 ·数字实验箱 。芯片 。CC4013 CC40192(CC40193)

计数器及其应用 一、实验目的 1.学习用集成触发器构成计数器的方法 2.掌握集成计数器的使用及功能测试 二、实验仪器和设备 数字实验箱 芯片 ◦ CC4013 CC4O192(CC40193)

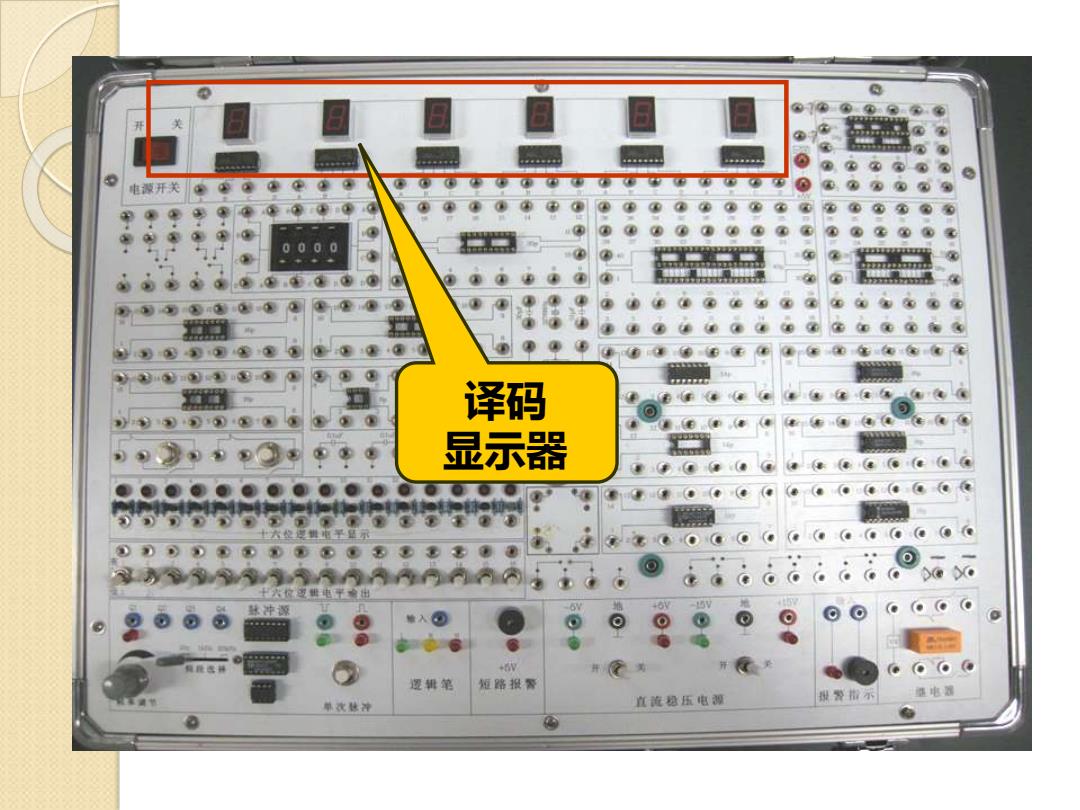

译码 显示器 d4Gd6dda 大位电平出 冲源 入 ⊙ 逻辑笔 短路报 直流超压电湖 电器

译码 显示器

译码电路电源, 用时连接 信号输入最 低位是A

译码电路电源, 用时连接 信号输入最 低位是A

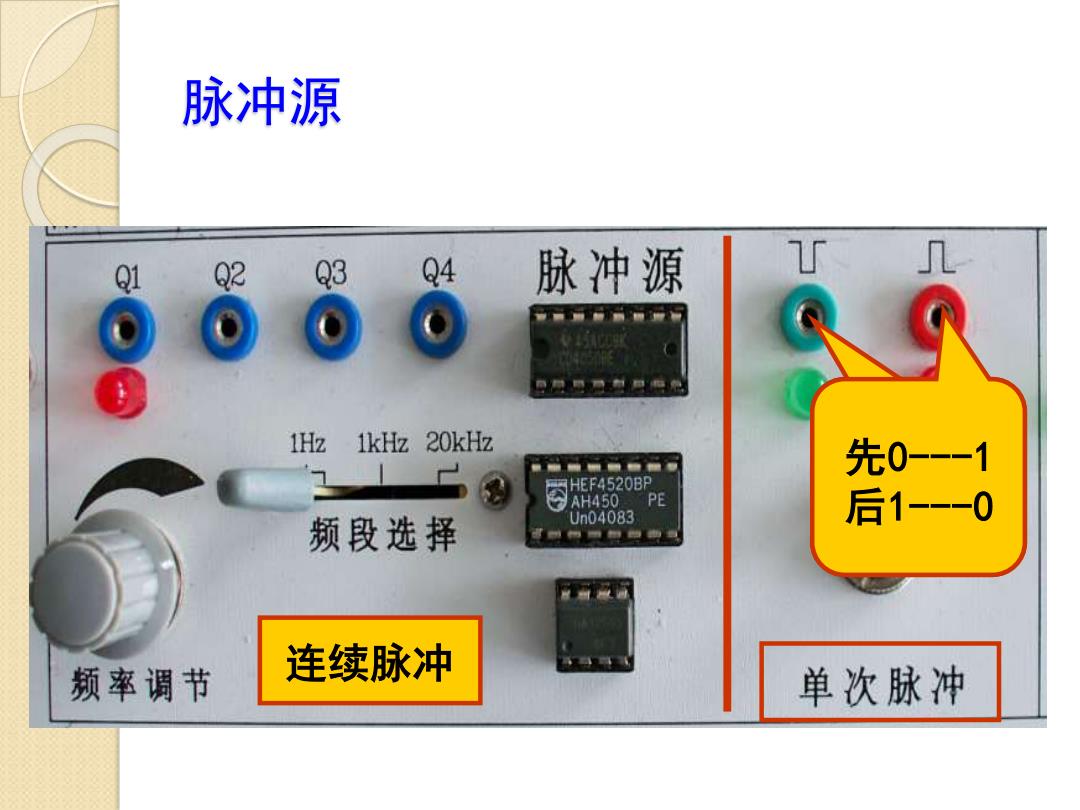

脉冲源 Q1 Q2 Q3 Q4 脉冲源 1Hz 1kHz 20kHz 520BP AH450 PE 0n04083 二0 频段选择 频率调节 连续脉冲 单次脉冲

脉冲源 连续脉冲 先1---0 后0---1 先0---1 后1---0

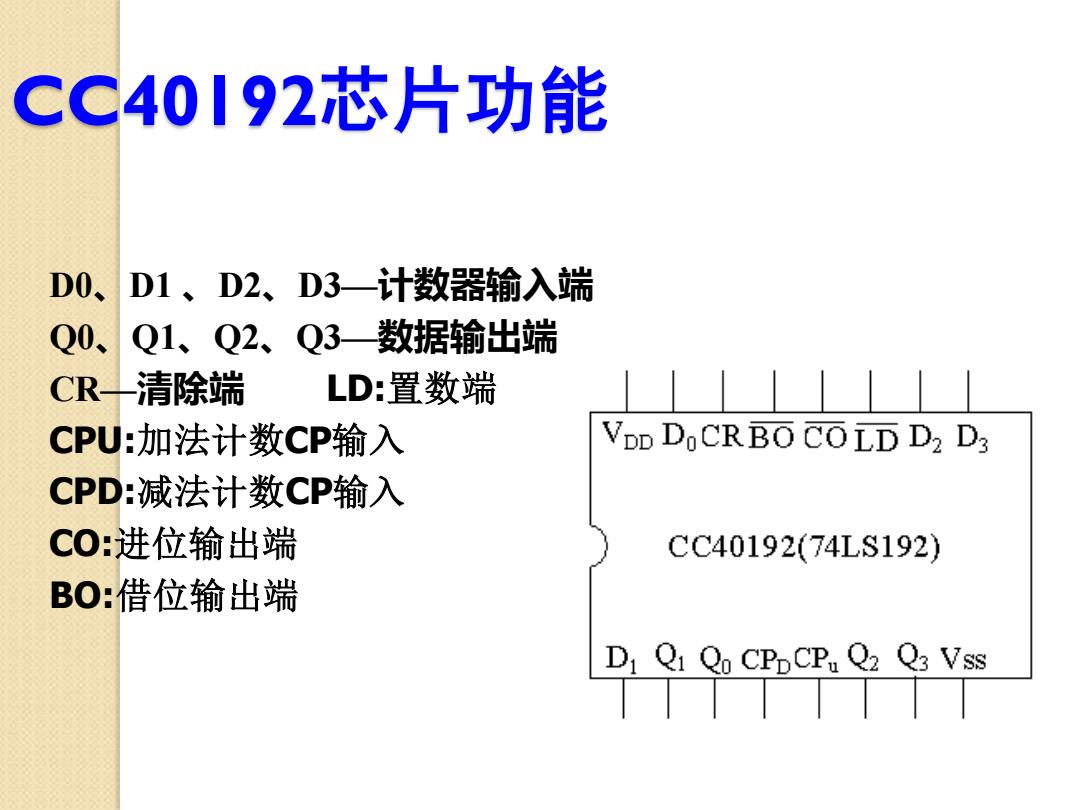

CC40192芯片功能 D0、D1、D2、D3一计数器输入端 Q0、 Q1、Q2、Q3一数据输出端 CR一清除端 LD:置数端 CPU:加法计数CP输入 VDD DoCRBO COLD D2 D3 CPD:减法计数CP输入 CO:进位输出端 CC40192(74LS192) BO:借位输出端 D1 Q1 Qo CPDCPu Q2 Q3 Vss

CC40192芯片功能 D0、D1 、D2、D3—计数器输入端 Q0、Q1、Q2、Q3—数据输出端 CR—清除端 LD:置数端 CPU:加法计数CP输入 CPD:减法计数CP输入 CO:进位输出端 BO:借位输出端

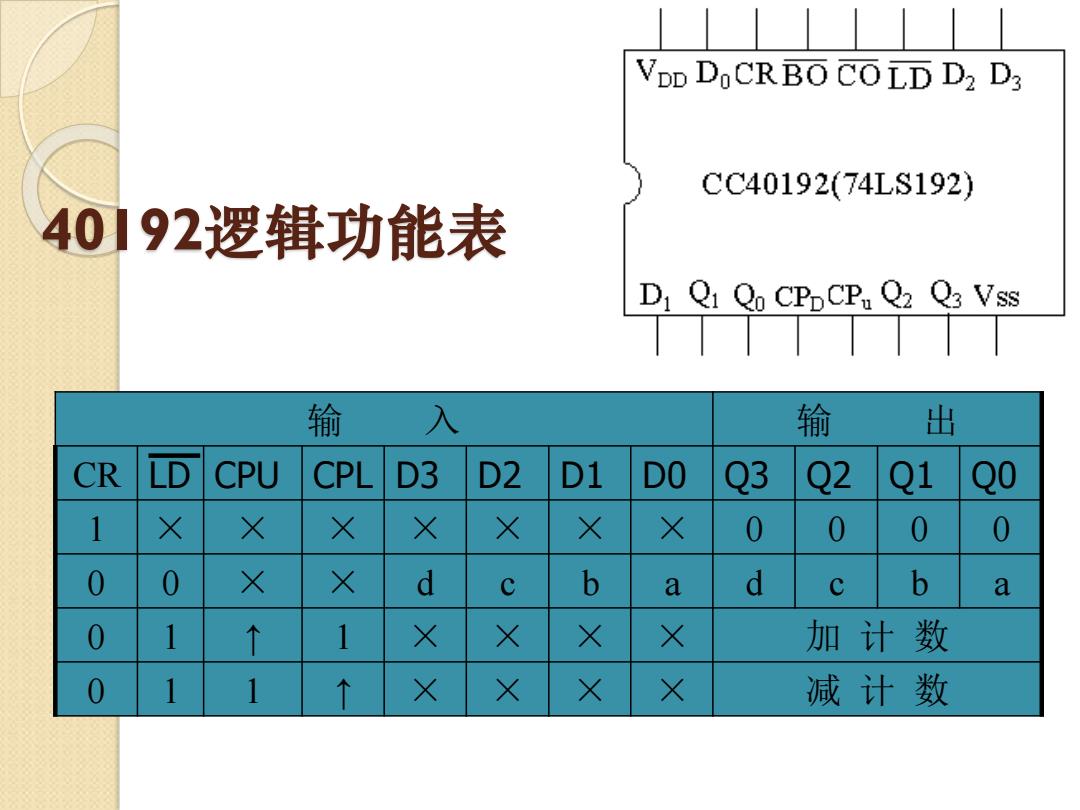

VDD DoCRBO CO LD D2 D3 CC40192(74LS192) 4092逻辑功能表 D1 Q1 Qo CPDCPu Q2 Q3 Vss 输 入 输 出 CR LD CPU CPL D3 D2 D1 DO Q3 Q2 Q1 Q0 1 × × × X × × × 0 0 0 0 0 0 X × d b a d b a 0 1 ↑ X X × 加计数 0 1 个 × × × X 减计数

40192逻辑功能表 74ls192功能表: LDQCD0132P1302 DU 输 入 输 出 CR LD CPU CPL D3 D2 D1 D0 Q3 Q2 Q1 Q0 1 × × × × × × × 0 0 0 0 0 0 × × d c b a d c b a 0 1 ↑ 1 × × × × 加 计 数 0 1 1 ↑ × × × × 减 计 数

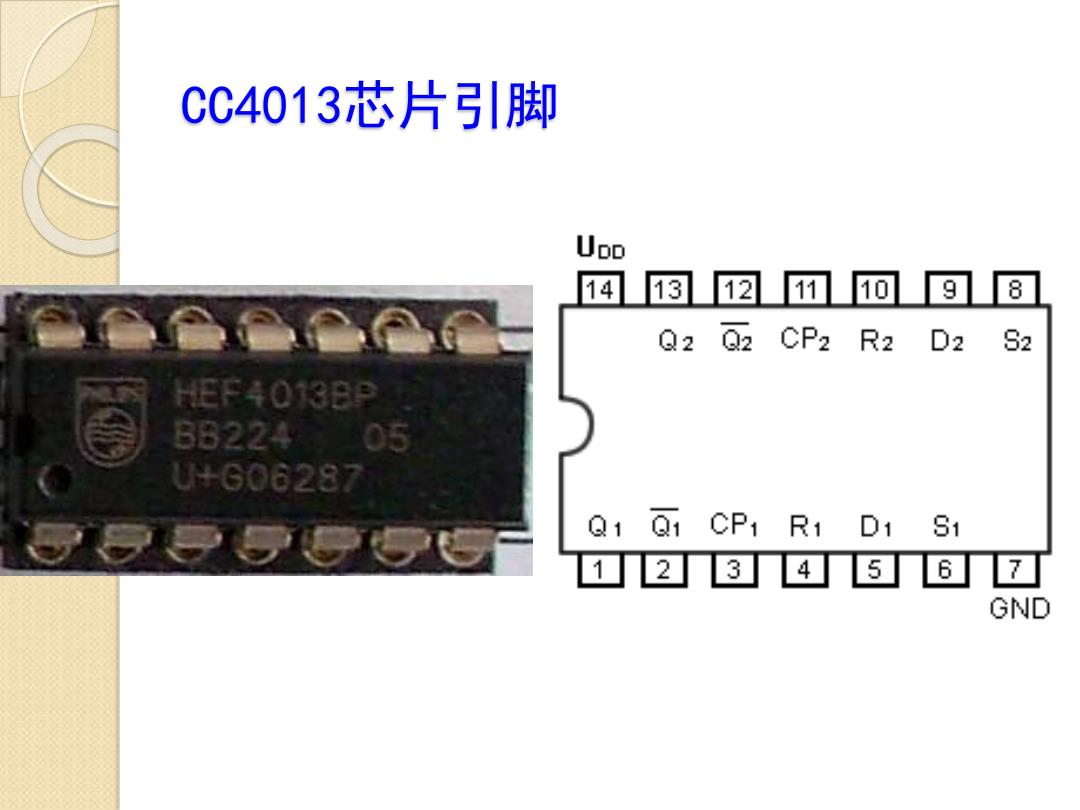

CC4013芯片引脚 Uoo 1413121M198 Q2 Q2 CP2 R2 D2 S2 HEF4013BP 88224 05 U+G06287 Q1ā1CP1R1D1 S1 1234567 GND

CC4013芯片引脚

三、实验原理 所谓计数,就是统计脉冲的个数,计数器就是实现“计数”操作的 时序逻辑电路。 计数器种类繁多。根据计数体制的不同,计数器可分成 二进制(即2n进制)计数器和非二进制计数器两大类 根据计数器的增减趋势不同,计数器可分为加法计数器—随着 计数脉冲的输入而递增计数的;减法计数器一随着计数脉冲的 输入而递减的,可逆计数器一既可递增、也可递减的。 根据计数脉冲引人方式不同,计数器又可分为同步计数器 一计 数脉冲直接加到所有触发器的时钟脉冲(CP)输入端;异步计 数器一计数脉冲不是直接加到所有触发器的时钟脉冲(CP) 输入端

三、实验原理 所谓计数,就是统计脉冲的个数,计数器就是实现“计数”操作的 时序逻辑电路。 计数器种类繁多。根据计数体制的不同,计数器可分成 二进制(即2n进制)计数器和非二进制计数器两大类 根据计数器的增减趋势不同,计数器可分为加法计数器——随着 计数脉冲的输入而递增计数的;减法计数器——随着计数脉冲的 输入而递减的,可逆计数器——既可递增、也可递减的。 根据计数脉冲引人方式不同,计数器又可分为同步计数器——计 数脉冲直接加到所有触发器的时钟脉冲(CP)输入端;异步计 数器——计数脉冲不是直接加到所有触发器的时钟脉冲(CP) 输入端

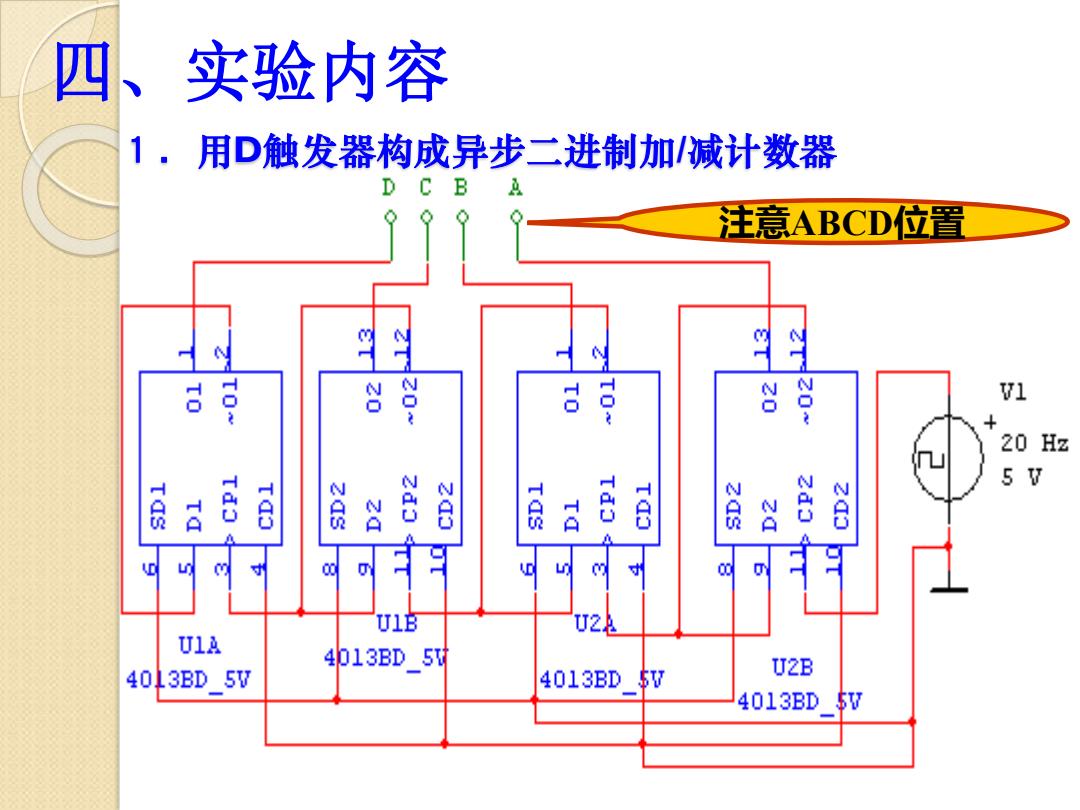

四、实验内容 1.用D触发器构成异步二进制加/减计数器 DC B 注意ABCD位置 8 88 VI 20 Hz N N y 员 N N B 员 员 0 U1B U2 UIA 4013BD 5V 40L3BD 5V 4013BD5V U2B 4013BD5V

1.用D触发器构成异步二进制加/减计数器 注意ABCD位置 四、实验内容

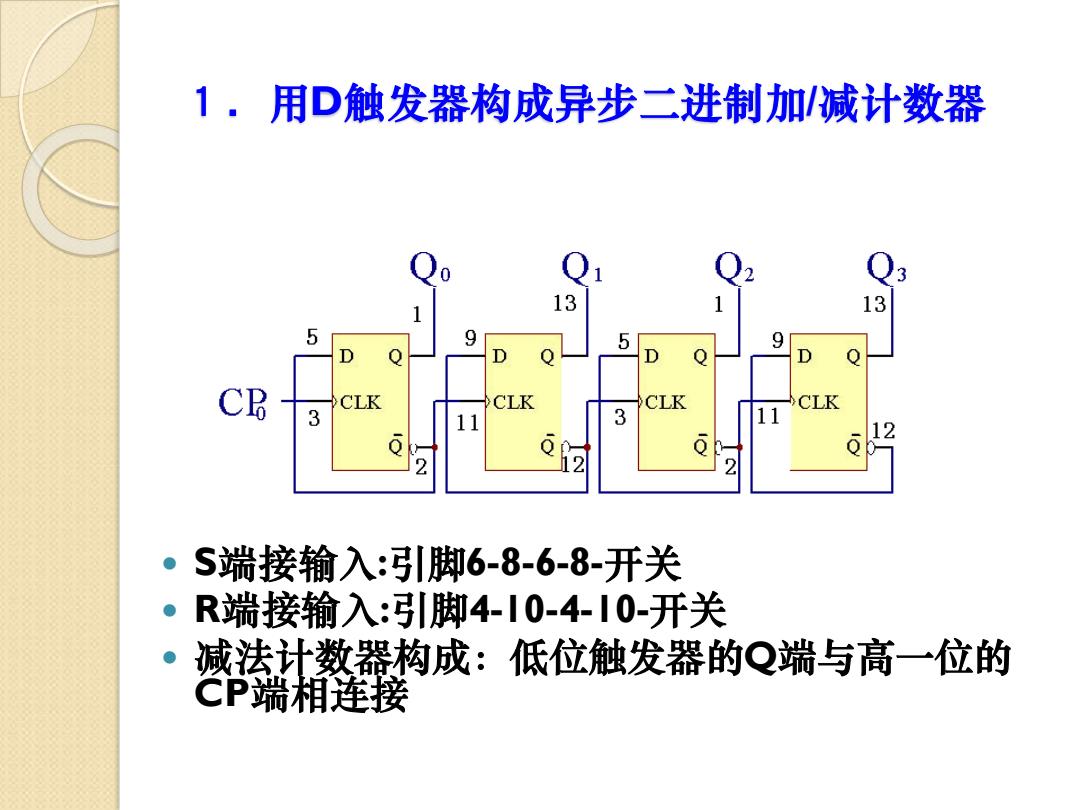

1·用D触发器构成异步二进制加/减计数器 o Q Q2 13 1 1 13 5 9 5 9 D Q D Q D CR CLK CLK CLK CLK 3 11 2 ● S端接输入:引脚6-8-6-8-开关 R端接输入:引脚4-10-4-10-开关 减法计数器构成:低位触发器的Q端与高一位的 CP端相连接

1.用D触发器构成异步二进制加/减计数器 S端接输入:引脚6-8-6-8-开关 R端接输入:引脚4-10-4-10-开关 减法计数器构成:低位触发器的Q端与高一位的 CP端相连接