电子秒表的设计 一、 实验目的 I、学习数字电路中基本RS触发器、时钟发生 器及计数、译码显示等单元电路的综合应用。 2、学习电子秒表的调试方法,设计60秒计时器

1、学习数字电路中基本RS触发器、时钟发生 器及计数、译码显示等单元电路的综合应用。 2、学习电子秒表的调试方法,设计60秒计时器。 一、实验目的 电子秒表的设计

二、实验仪器和设备 1数字电子实验箱 2.示波器 3.74LS192×2、555×、CC4011×2、电位器、电 阻、电容若干

二、实验仪器和设备 1.数字电子实验箱 2.示波器 3.74LS1922、5551、CC40112、电位器、电 阻、电容若干

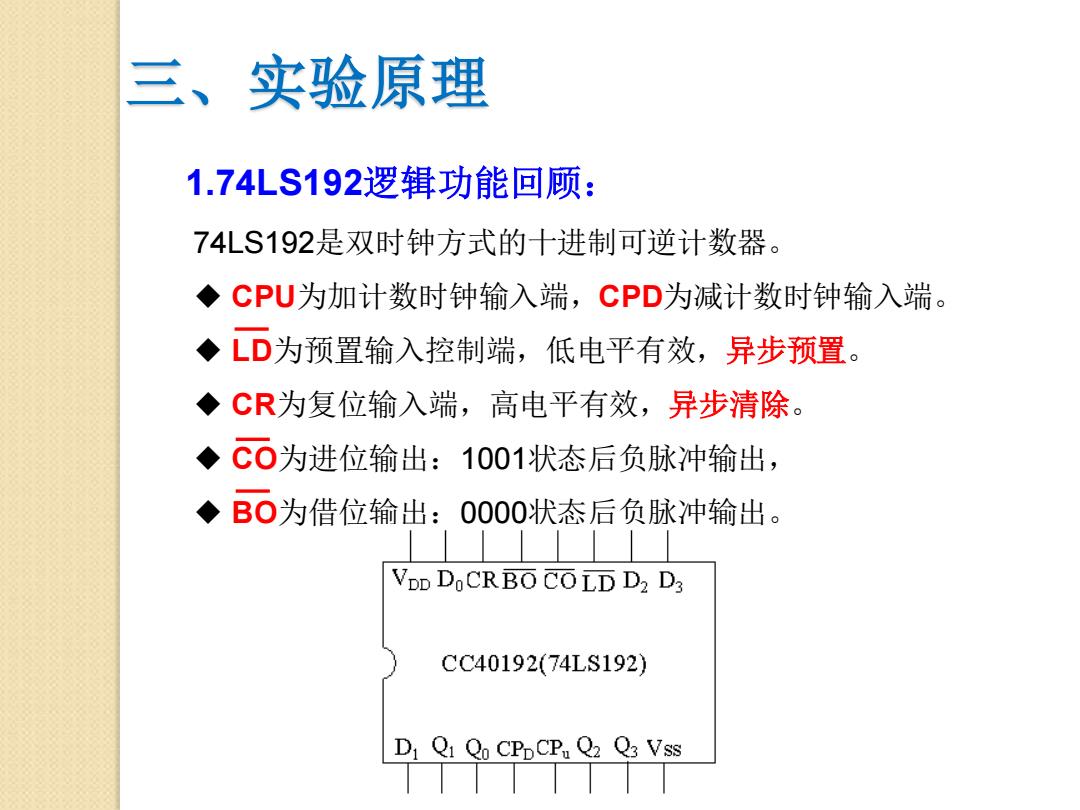

三、实验原理 1.74LS192逻辑功能回顾: 74LS192是双时钟方式的十进制可逆计数器。 ◆CPU为加计数时钟输入端,CPD为减计数时钟输入端。 ◆LD为预置输入控制端,低电平有效,异步预置。 ◆CR为复位输入端,高电平有效,异步清除。 ◆C0为进位输出:1001状态后负脉冲输出, ◆BO为借位输出:0000状态后负脉冲输出。 VDD DoCRBO COLD D2 D3 CC40192(74LS192) D1 Q1 Qo CPDCPu Q2 Q3 Vss

三、实验原理 1.74LS192逻辑功能回顾: 74LS192是双时钟方式的十进制可逆计数器。 ◆ CPU为加计数时钟输入端,CPD为减计数时钟输入端。 ◆ LD为预置输入控制端,低电平有效,异步预置。 ◆ CR为复位输入端,高电平有效,异步清除。 ◆ CO为进位输出:1001状态后负脉冲输出, ◆ BO为借位输出:0000状态后负脉冲输出

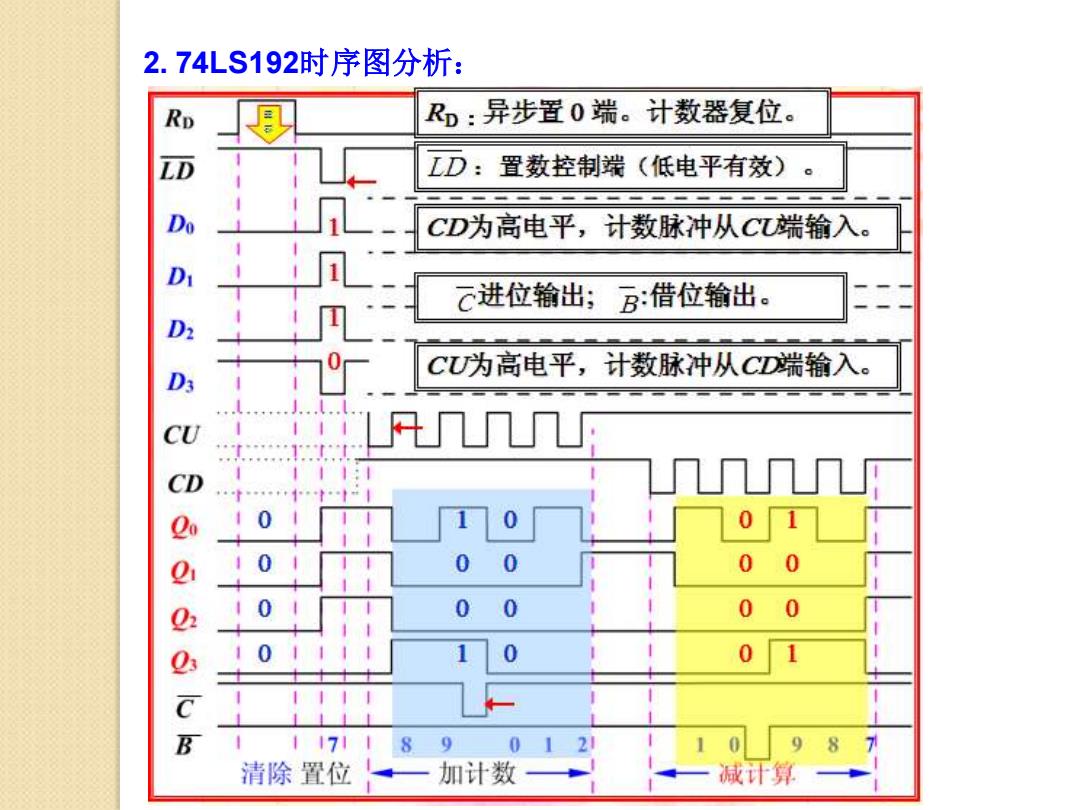

2.74LS192时序图分析: R:异步置0端。计数器复位。 D LD:置数控制端(低电平有效) CD为高电平,计数脉冲从CL端输入。 C进位输出; B:借位输出。 0 CU为高电平,计数脉冲从CD端输入。 0 0 0 0 0 0 0 0 0 0 0 0 11711 0 清除置位 加计数 减计算

2. 74LS192时序图分析:

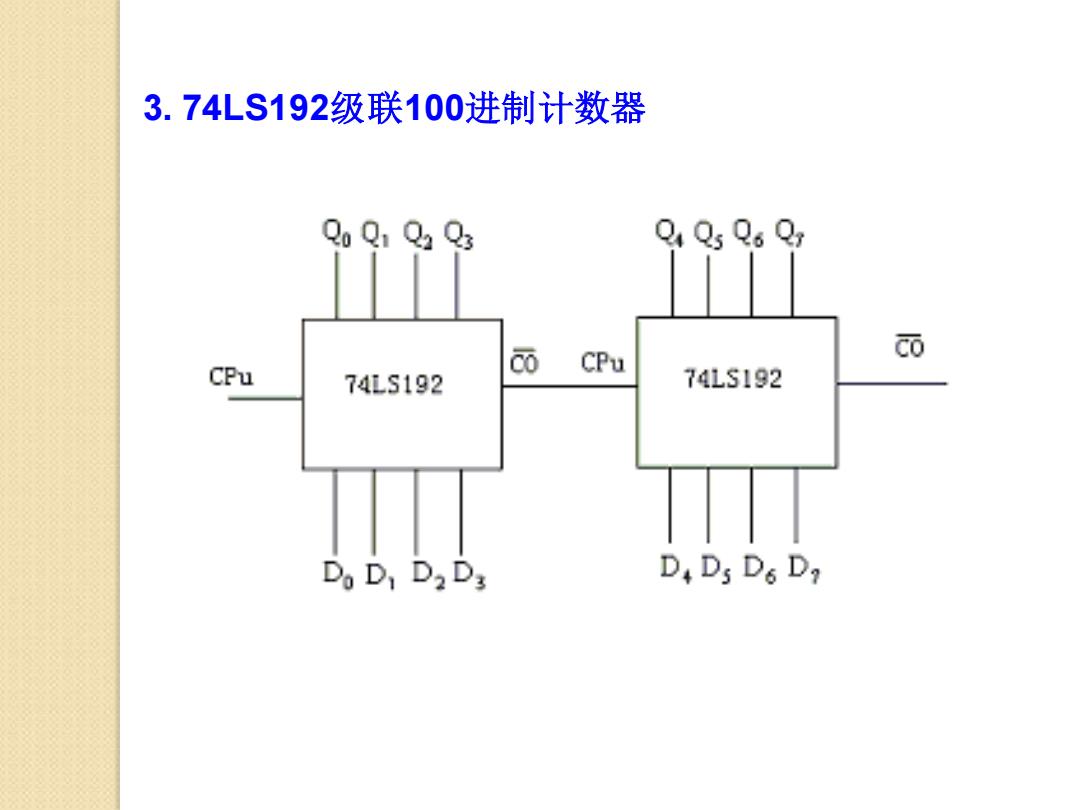

3.74LS192级联100进制计数器 Qo Q:Q2 Q3 Q Q5 Q6 Q CPu 而 CPu 741S192 741S192 Do D D2D3 D Ds D6 D2

3. 74LS192级联100进制计数器

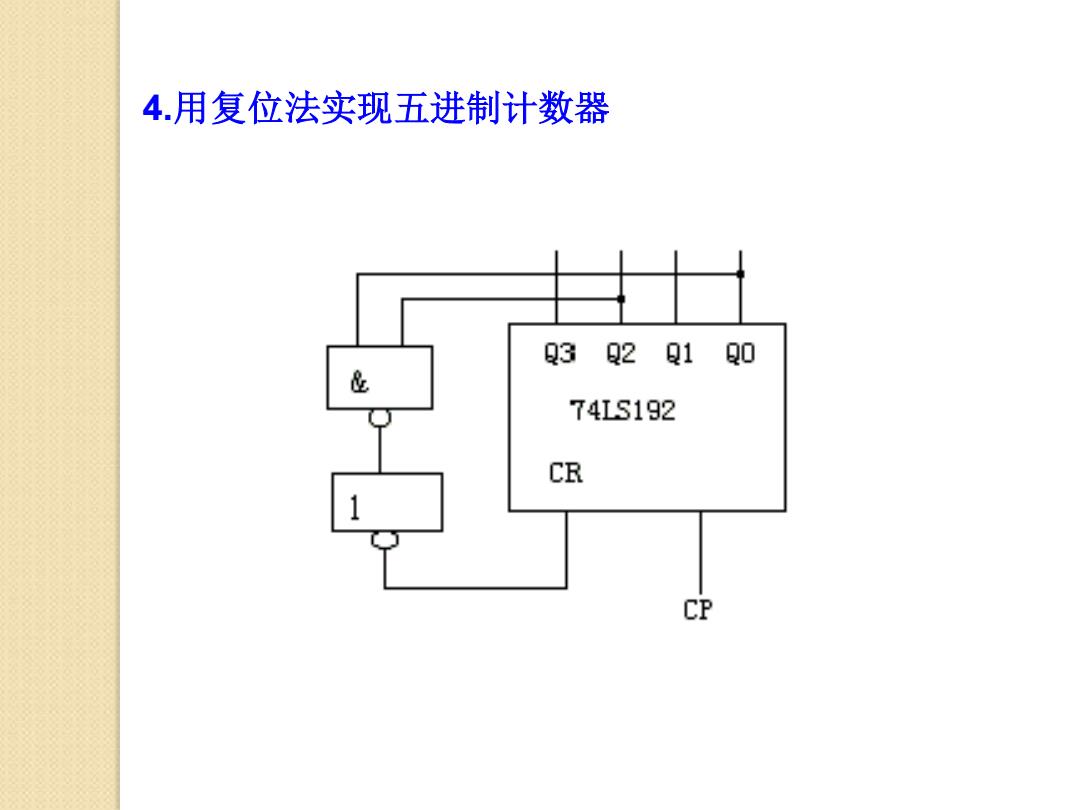

4.用复位法实现五进制计数器 Q3 Q2 Q1 Q0 74LS192 CR CP

4.用复位法实现五进制计数器

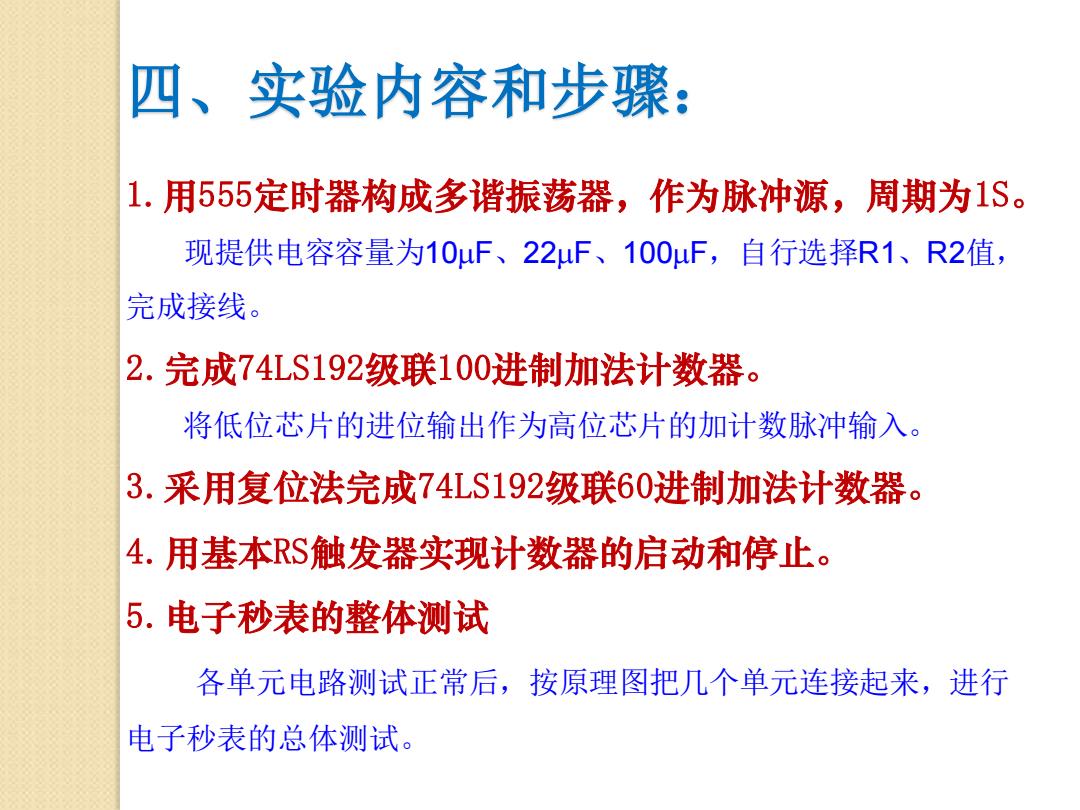

四、实验内容和步骤: 1.用555定时器构成多谐振荡器,作为脉冲源,周期为1S。 现提供电容容量为10uF、22uF、100uF,自行选择R1、R2值, 完成接线。 2.完成74LS192级联100进制加法计数器。 将低位芯片的进位输出作为高位芯片的加计数脉冲输入。 3.采用复位法完成74LS192级联60进制加法计数器。 4.用基本RS触发器实现计数器的启动和停止。 5.电子秒表的整体测试 各单元电路测试正常后,按原理图把几个单元连接起来,进行 电子秒表的总体测试

四、实验内容和步骤: 1.用555定时器构成多谐振荡器,作为脉冲源,周期为1S。 现提供电容容量为10F、22F、100F,自行选择R1、R2值, 完成接线。 2.完成74LS192级联100进制加法计数器。 将低位芯片的进位输出作为高位芯片的加计数脉冲输入。 3.采用复位法完成74LS192级联60进制加法计数器。 4.用基本RS触发器实现计数器的启动和停止。 5.电子秒表的整体测试 各单元电路测试正常后,按原理图把几个单元连接起来,进行 电子秒表的总体测试

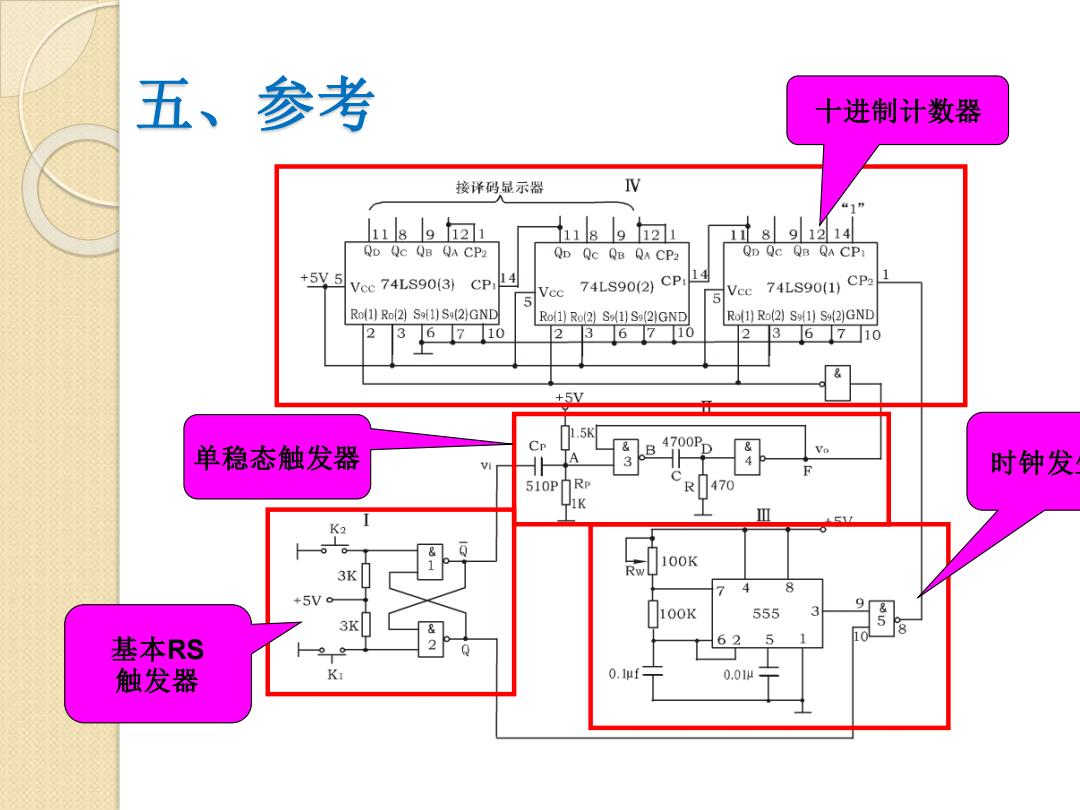

五、参考 十进制计数器 接译码显示器 u892i 8g214 QD Qc QB QA CP2 QD Qc QB QA CP2 QD Qc QB QA CP1 +5V5 Vcc 74LS90(3)CP 14 74LS902)CP Vcc 74LS901)CP Rol1)Ro(2)S9(1)S9(2)GND Rof1)Ro(2)S9(1)S(2)GND Rof1)Ro(2)S9(1)S9(2)GND 236710 36710 36710 +5V 单稳态触发器 时钟发 R470 1K 金 100K 3K 100K 555 3K 基本RS 62 触发器 K 0.1uf1

五、参考 基本RS 触发器 单稳态触发器 时钟发生器 十进制计数器

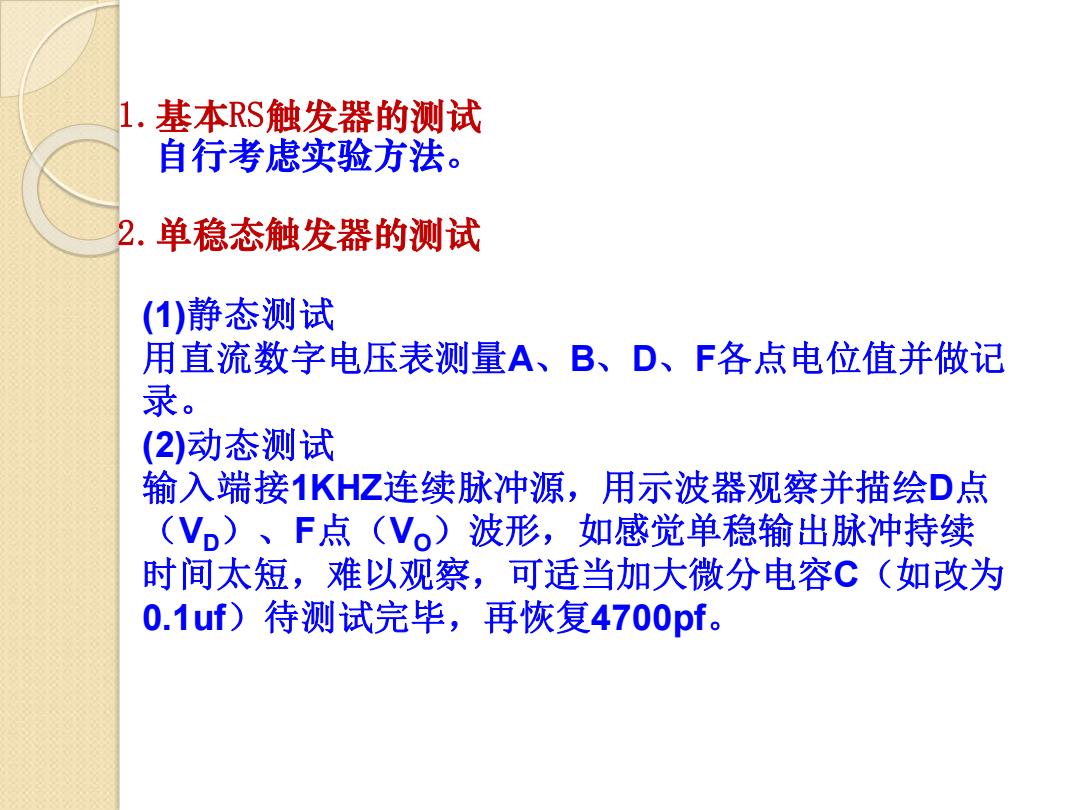

1.基本RS触发器的测试 自行考虑实验方法。 2.单稳态触发器的测试 (1)静态测试 用直流数字电压表测量A、B、D、F各点电位值并做记 录。 (2)动态测试 输入端接1KHZ连续脉冲源,用示波器观察并描绘D点 (Vo)、F点(Vo)波形,如感觉单稳输出脉冲持续 时间太短,难以观察,可适当加大微分电容C(如改为 0.1uf)待测试完毕,再恢复4700pf

1.基本RS触发器的测试 自行考虑实验方法。 2.单稳态触发器的测试 (1)静态测试 用直流数字电压表测量A、B、D、F各点电位值并做记 录。 (2)动态测试 输入端接1KHZ连续脉冲源,用示波器观察并描绘D点 (VD)、F点(VO)波形,如感觉单稳输出脉冲持续 时间太短,难以观察,可适当加大微分电容C(如改为 0.1uf)待测试完毕,再恢复4700pf

3.时钟发生器的测试 自行考虑实验方法,用示波器观察输出电压波形并测量其 频率,调节RW,使输出矩形波频率为Hz。 4.计数器的测试 ()计数器①接成五进制形式,接逻辑开关输出插口,接单 次脉冲源,接高电平“1”,接实验设备上译码显示输入 端D、C、B、A,按教材中表5一27测试其逻辑功能并做 记录。 (2)计数器②及计数器③接成8421码十进制形式,同内容 ()进行逻辑功能测试并做记录。 (3)将计数器①、②、③级连,进行逻辑功能测试并做记 录

3.时钟发生器的测试 自行考虑实验方法,用示波器观察输出电压波形并测量其 频率,调节RW,使输出矩形波频率为1Hz。 4.计数器的测试 (1)计数器①接成五进制形式,接逻辑开关输出插口,接单 次脉冲源,接高电平“1”,接实验设备上译码显示输入 端D、C、B、A,按教材中表5—27测试其逻辑功能并做 记录。 (2)计数器 ② 及计数器③接成8421码十进制形式,同内容 (1)进行逻辑功能测试并做记录。 (3)将计数器 ①、②、③ 级连,进行逻辑功能测试并做记 录