4.组合逻辑电路 1.写出图1a、b所示电路的逻辑表达式,并化简 A 图1 2。组合逻辑电路及输人波形(4.B)如图2所示,试写出输出端的逻辑表达式并画出输 出波形。 厂 B几一 图2 3.设有四种组合逻辑电路,它们的输入波形(4、B.C,D)如图3所示,其对应的输出 波形为队、X.了.工,试分别写出它们的简化逻辑表达式. 几几几几 D 输出 冂 xu厂 图3

4.组合逻辑电路 1.写出图 1 a、b 所示电路的逻辑表达式,并化简。 A B (a) C L 1 & ≥1 & ≥1 & L1 L2 A B (b) C 1 ≥1 1 1 & & & 1 ≥1 图 1 2.组合逻辑电路及输入波形(A、B)如图 2 所示,试写出输出端的逻辑表达式并画出输 出波形。 A B B L 1 & 1 & A ≥1 图 2 3.设有四种组合逻辑电路,它们的输入波形(A、B、C、D)如图 3 所示,其对应的输出 波形为 W、X、Y、Z,试分别写出它们的简化逻辑表达式。 输出 A B C D W X Y Z 输入 图 3

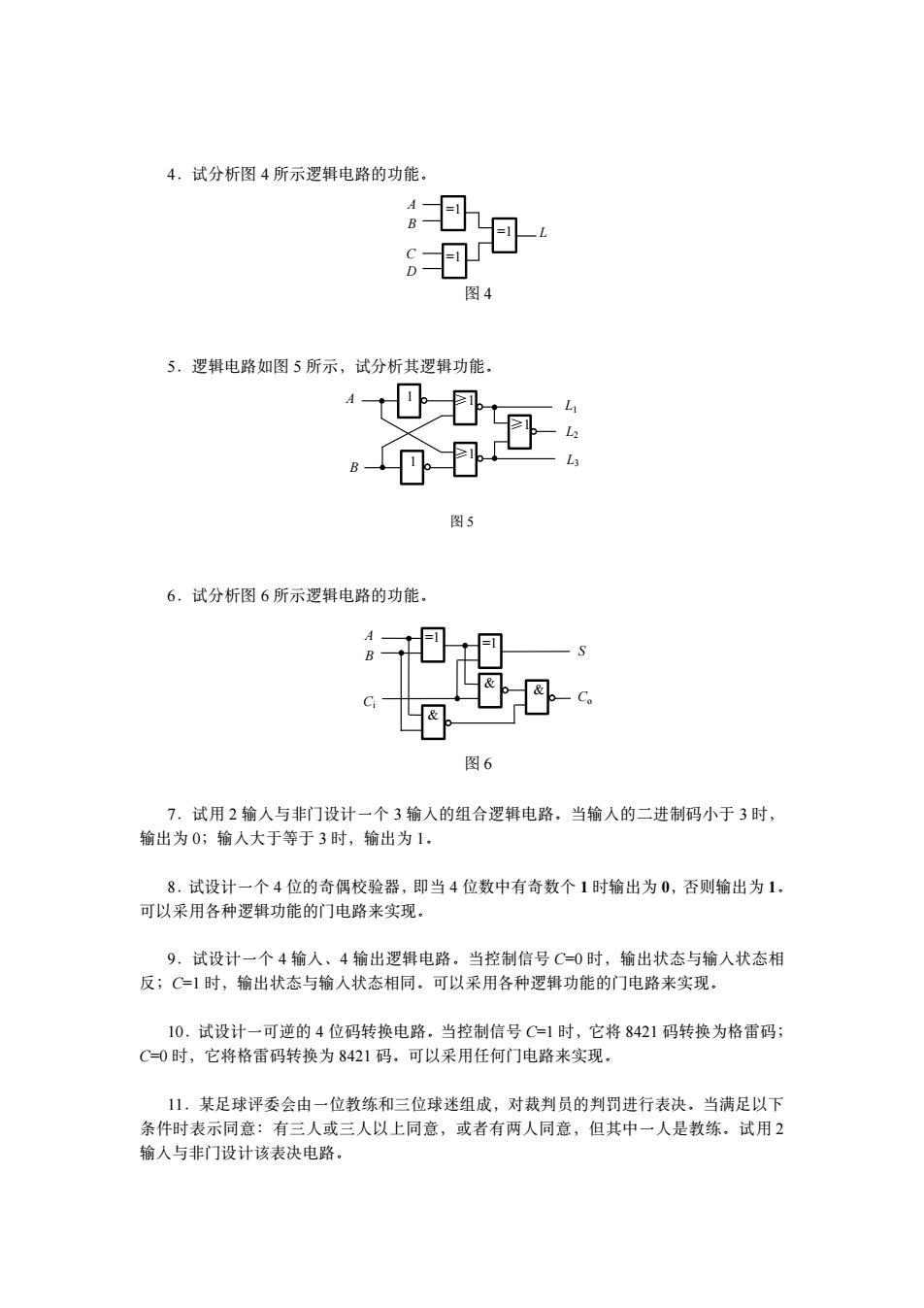

4.试分析图4所示逻辑电路的功能. 0 6 图4 5.逻辑电路如图5所示,试分析其逻辑功能. 图5 6.试分析图6所示逻辑电路的功能.。 图6 7.试用2输人与非门设计一个3输入的组合逻辑电路,当输入的二进制码小于3时 输出为0:输人大于等于3时,输出为1, 8.试设计一个4位的奇偶校验器,即当4位数中有奇数个1时输出为0,否则输出为1, 可以采用各种逻辑功能的门电路来实现。 g试设计一个4输 、4输出逻辑电路。当控制信号C-0时,输出状态与输人状态相 反:C1时,输出状态与输人状态相同。可以采用各种逻辑功能的门电路来实现 10.试设计一可逆的4位码转换电路。当控制信号C=]时,它将8421码转换为格雷码; C-0时,它将格雷码转换为8421码。可以采用任何门电路来实现. 一位教练和三位球迷组成,对裁判员的判罚进行表决。当满足以下 输人与非门设计该表决电路

4.试分析图 4 所示逻辑电路的功能。 A B C D L =1 =1 =1 图 4 5.逻辑电路如图 5 所示,试分析其逻辑功能。 A B L1 L2 1 L3 ≥1 1 ≥1 ≥1 图 5 6.试分析图 6 所示逻辑电路的功能。 A B Ci S Co & =1 =1 & & 图 6 7.试用 2 输入与非门设计一个 3 输入的组合逻辑电路。当输入的二进制码小于 3 时, 输出为 0;输入大于等于 3 时,输出为 1。 8.试设计一个 4 位的奇偶校验器,即当 4 位数中有奇数个 1 时输出为 0,否则输出为 1。 可以采用各种逻辑功能的门电路来实现。 9.试设计一个 4 输入、4 输出逻辑电路。当控制信号 C=0 时,输出状态与输入状态相 反;C=1 时,输出状态与输入状态相同。可以采用各种逻辑功能的门电路来实现。 10.试设计一可逆的 4 位码转换电路。当控制信号 C=1 时,它将 8421 码转换为格雷码; C=0 时,它将格雷码转换为 8421 码。可以采用任何门电路来实现。 11.某足球评委会由一位教练和三位球迷组成,对裁判员的判罚进行表决。当满足以下 条件时表示同意:有三人或三人以上同意,或者有两人同意,但其中一人是教练。试用 2 输入与非门设计该表决电路

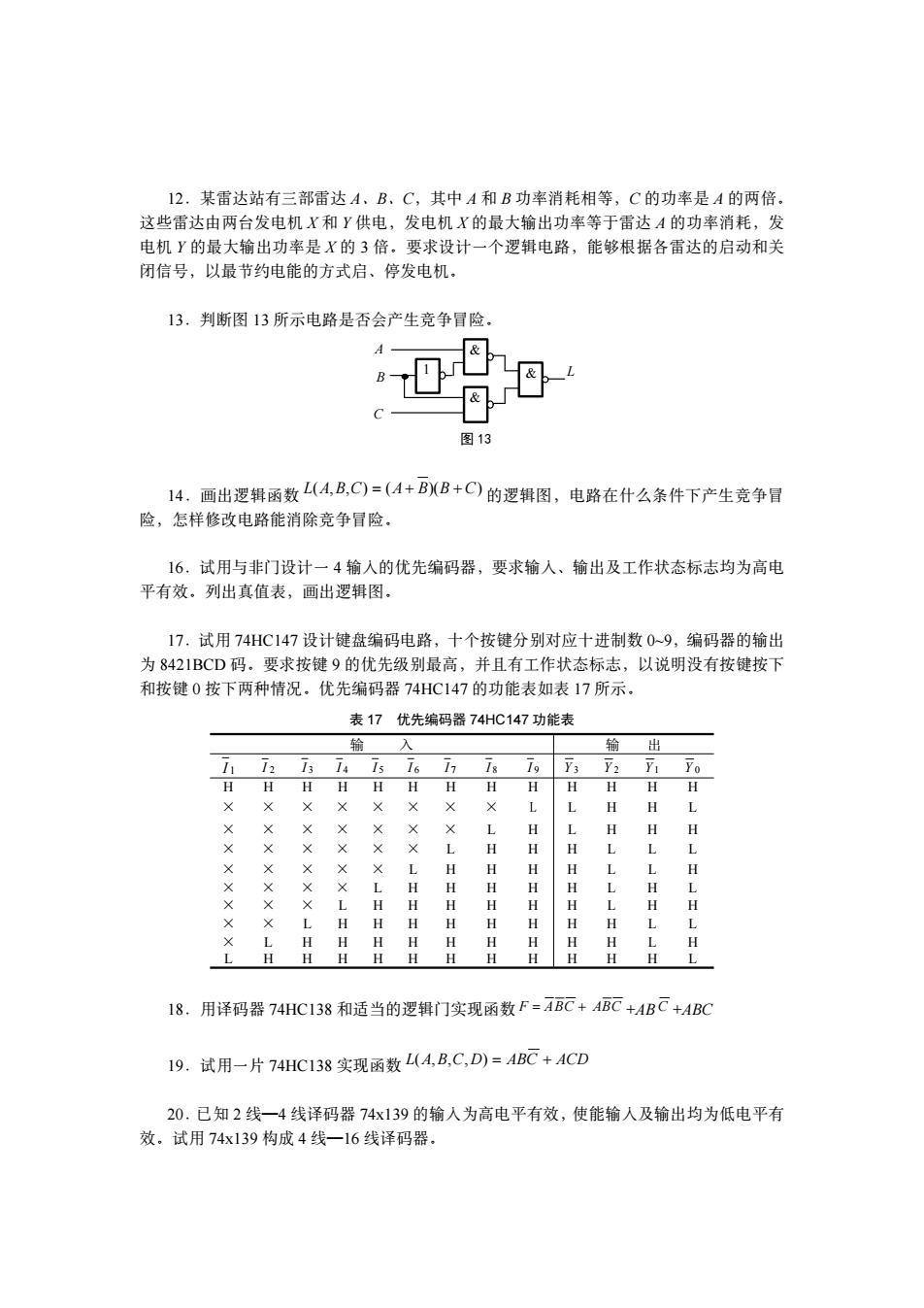

12.某雷达站有三部雷达A、B,C,其中A和B功率消耗相等,C的功率是A的两倍 这些雷达由两台发电机X和Y供电,发电机X的最大输出功率等于雷达A的功率消耗,发 电机Y的最大输出功率是X的3倍。.要求设计一个逻辑电路,能够根据各雷达的启动和关 闭信号,以最节约电能的方式启、停发电机。 13.判断图13所示电路是否会产生竞争冒险 A 图13 14.画出逻辑函数(4B,C)=(+B(B+C的逻辑图, 电路在什么条件下产生竞争目 险,怎样修改电路能消除竞争冒险】 16,试用与非门设计一4输人的优先编码器,要求输入、输出及工作状态标志均为高电 平有效.列出直值表,画出逻辑图。 17.试用74HC147设计键盘编码电路,十个按键分别对应十进制数09,编码器的输出 为8421BCD码,要求按键9的优先级别最高,并且有工作状态标志,以说明没有按键按下 和按健0按下两种情况.优先编码器74HC147的功能表如表17所示. 表17优先编码器74HC147功能表 输出 1723145761797721 H H H HHH H H H + + HH E- XXX H L, HH E-34 L H HH 18,用译码器74HC138和适当的逻辑门实现函数F=BC+ABC+ABC+ABC 19.试用-片74HC138实现函数(4B,C,D)=ABC+ACD 20.已知2线一4线译码器74x139的输人为高电平有效,使能输人及输出均为低电平有 效.试用74x139构成4线 -16线译码器

12.某雷达站有三部雷达 A、B、C,其中 A 和 B 功率消耗相等,C 的功率是 A 的两倍。 这些雷达由两台发电机 X 和 Y 供电,发电机 X 的最大输出功率等于雷达 A 的功率消耗,发 电机 Y 的最大输出功率是 X 的 3 倍。要求设计一个逻辑电路,能够根据各雷达的启动和关 闭信号,以最节约电能的方式启、停发电机。 13.判断图 13 所示电路是否会产生竞争冒险。 A B C 1 L & & & 图 13 14.画出逻辑函数 L(A,B,C) (A B)(B C) 的逻辑图,电路在什么条件下产生竞争冒 险,怎样修改电路能消除竞争冒险。 16.试用与非门设计一 4 输入的优先编码器,要求输入、输出及工作状态标志均为高电 平有效。列出真值表,画出逻辑图。 17.试用 74HC147 设计键盘编码电路,十个按键分别对应十进制数 0~9,编码器的输出 为 8421BCD 码。要求按键 9 的优先级别最高,并且有工作状态标志,以说明没有按键按下 和按键 0 按下两种情况。优先编码器 74HC147 的功能表如表 17 所示。 表 17 优先编码器 74HC147 功能表 输 入 输 出 I 1 I 2 I 3 I 4 I 5 I 6 I 7 I 8 I 9 Y 3 Y 2 Y1 Y 0 H H H H H H H H H H H H H × × × × × × × × L L H H L × × × × × × × L H L H H H × × × × × × L H H H L L L × × × × × L H H H H L L H × × × × L H H H H H L H L × × × L H H H H H H L H H × × L H H H H H H H H L L × L H H H H H H H H H L H L H H H H H H H H H H H L 18.用译码器 74HC138 和适当的逻辑门实现函数 F ABC ABC +AB C +ABC 19.试用一片 74HC138 实现函数 L(A,B,C,D) ABC ACD 20.已知 2 线—4 线译码器 74x139 的输入为高电平有效,使能输入及输出均为低电平有 效。试用 74x139 构成 4 线—16 线译码器

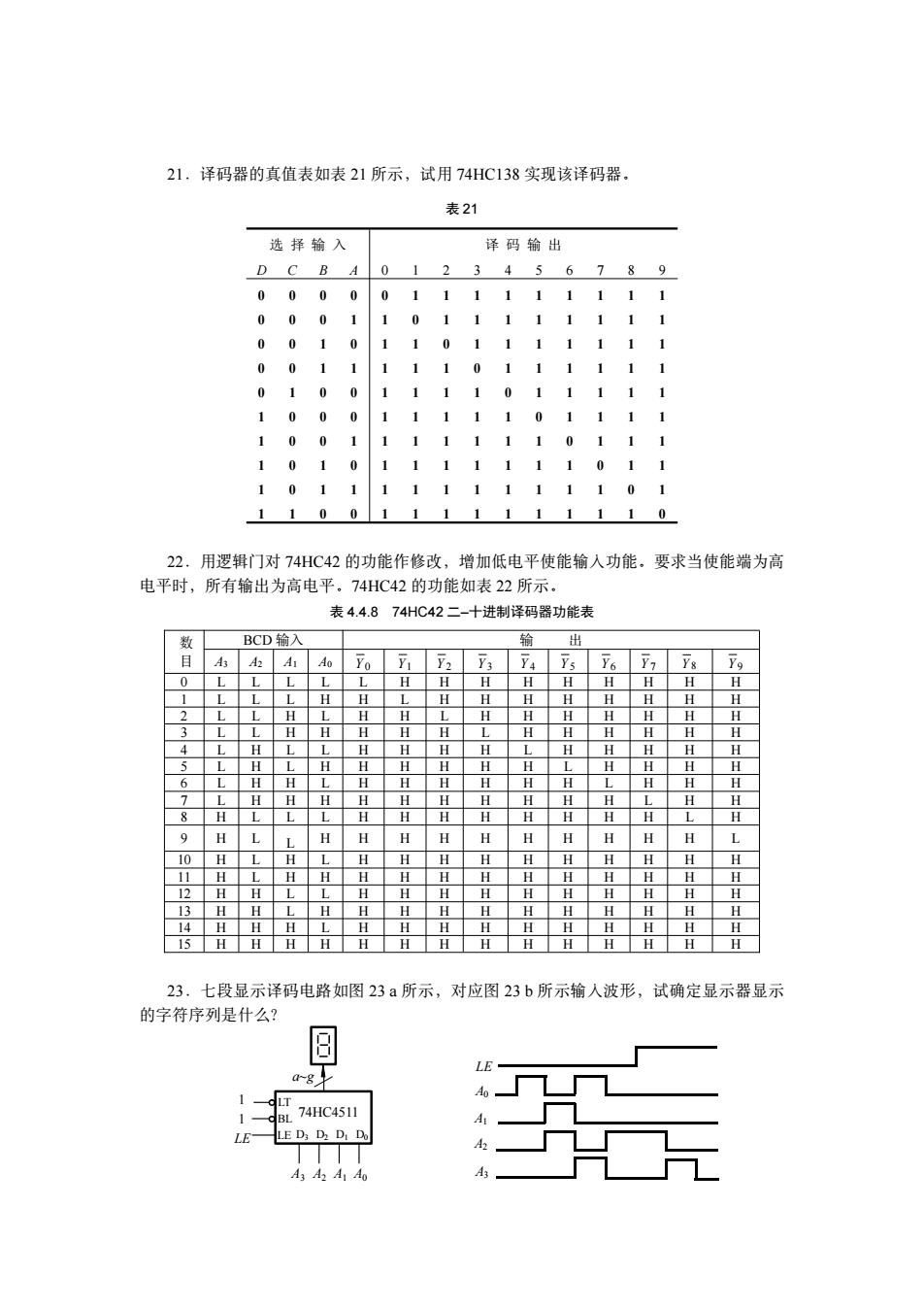

21.译码器的真值表如表21所示,试用74HC138实现该译码器 表21 选择输入 译码输出 D 6789 1 1 1 1 1 01 11001111111110 2。用逻辑门对74HC42的功能作修改,增加低电平使能输入功能.要求当使能端为高 电平时,所有输出为高电平.74HC42的功能如表22所示. 表4.4.874HC42二-十进制译码器功能表 2 23.七段显示译码电路如图23a所示,对应图23b所示输人波形,试确定显示器显示 的字符序列是什么 a-2

21.译码器的真值表如表 21 所示,试用 74HC138 实现该译码器。 表 21 选 择 输 入 译 码 输 出 D C B A 0 1 2 3 4 5 6 7 8 9 0 0 0 0 0 1 1 1 1 1 1 1 1 1 0 0 0 1 1 0 1 1 1 1 1 1 1 1 0 0 1 0 1 1 0 1 1 1 1 1 1 1 0 0 1 1 1 1 1 0 1 1 1 1 1 1 0 1 0 0 1 1 1 1 0 1 1 1 1 1 1 0 0 0 1 1 1 1 1 0 1 1 1 1 1 0 0 1 1 1 1 1 1 1 0 1 1 1 1 0 1 0 1 1 1 1 1 1 1 0 1 1 1 0 1 1 1 1 1 1 1 1 1 1 0 1 1 1 0 0 1 1 1 1 1 1 1 1 1 0 22.用逻辑门对 74HC42 的功能作修改,增加低电平使能输入功能。要求当使能端为高 电平时,所有输出为高电平。74HC42 的功能如表 22 所示。 表 4.4.8 74HC42 二–十进制译码器功能表 数 目 BCD 输入 输 出 A3 A2 A1 A0 Y0 Y1 Y 2 Y3 Y 4 Y5 Y6 Y7 Y8 Y9 0 L L L L L H H H H H H H H H 1 L L L H H L H H H H H H H H 2 L L H L H H L H H H H H H H 3 L L H H H H H L H H H H H H 4 L H L L H H H H L H H H H H 5 L H L H H H H H H L H H H H 6 L H H L H H H H H H L H H H 7 L H H H H H H H H H H L H H 8 H L L L H H H H H H H H L H 9 H L L H H H H H H H H H H L 10 H L H L H H H H H H H H H H 11 H L H H H H H H H H H H H H 12 H H L L H H H H H H H H H H 13 H H L H H H H H H H H H H H 14 H H H L H H H H H H H H H H 15 H H H H H H H H H H H H H H 23.七段显示译码电路如图 23 a 所示,对应图 23 b 所示输入波形,试确定显示器显示 的字符序列是什么? 1 a~g A3 A2 A1 A0 1 LE D3 D2 D1 D0 LT LE BL 74HC4511 A0 LE A1 A2 A3

a 图23 24.数据选择器如图24所示,并行输人数据山山=1010,控制端X-0,A4的态序分 别为00,01,10,11,试画出输出端L的波形, 图24 25.设计一4选1数据选择器,数据输入是6、2、h,数据输出是Y,4个控制信 号为S0、S、S2、S.要求只有当S=1时,山,与y接通,且由另一控制信号E作为该选择器 的使能信号。(①画出由反相器、两输入与门和或门实现的逻辑电路;(2)选择一合适的 态门作为输出级】 26.试用4选1数据选择器74HC153产生逻辑函数 L(A,B,C)=∑m(L,2,6,7) 27.8选1数据选择器74HC151的连接方式和各输入端的输入波形如图27所示,画出 输出端Y的波形. 图27 28.应用8选1数据选择器74HC151实现如下逻辑函数 (1)L=ABC+ABC+ABC (2)L=(AB)Oc

(a) (b) 图 23 24.数据选择器如图 24 所示,并行输入数据 I3I2I1I0=1010,控制端 X=0,A1A0的态序分 别为 00,01,10,11,试画出输出端 L 的波形。 L A1 A0 I3 I2 I1 I0 X 1 1 1 1 1 & ≥1 图 24 25.设计一 4 选 1 数据选择器。数据输入是 I0、I1、I2、I3,数据输出是 Y,4 个控制信 号为 S0、S1、S2、S3。要求只有当 Si=1 时,Ii与 Y 接通,且由另一控制信号 E 作为该选择器 的使能信号。(1) 画出由反相器、两输入与门和或门实现的逻辑电路;(2) 选择一合适的三 态门作为输出级。 26.试用 4 选 1 数据选择器 74HC153 产生逻辑函数 L(A, B,C) m(1, 2, 6, 7) 27.8 选 1 数据选择器 74HC151 的连接方式和各输入端的输入波形如图 27 所示,画出 输出端 Y 的波形。 E C B A 1 1 1 EN S2 S1 S0 D0 D1 D2 D3 D4 D5 D6 D7 A0 A2 74HC151 Y Y Y 1 A B C E A0 A2 (a) (b) 图 27 28.应用 8 选 1 数据选择器 74HC151 实现如下逻辑函数 (1) L ABC ABC ABC (2) L (A ⊙ B)⊙C

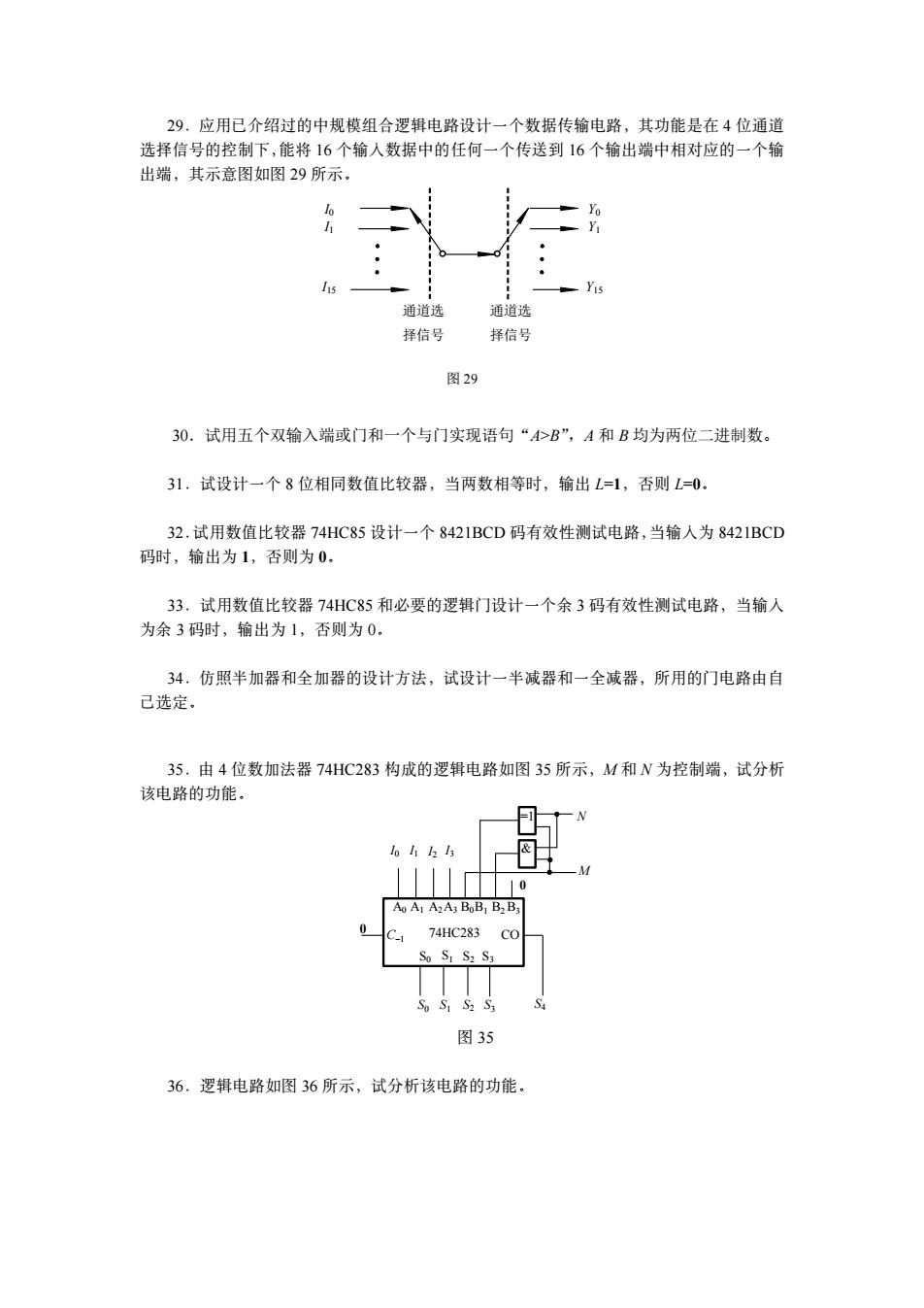

29.应用已介绍时的中规模组合罗辑电路设计一个数据传输电路,其功能是在4位通首 选择信号的控制下,能将16个输入数据中的任何一个传送到16个输出端中相对应的一个输 出端,其示意图如图29所示。 15 通道选通道选 择信号择信号 图29 30.试用五个双输入端或门和一个与门实现语句“4>B”,A和B均为两位二进制数: 3引.试设计一个8位相同数值比较器,当两数相等时,输出L1,否则L0 32.试用数值比较器74HC85设计一个8421BCD码有效性测试电路,当输入为8421BCD 码时,输出为1,否则为0, 3,试用数值比较器74HC85和必要的逻辑门设计一个余3码有效性测试电路,当输入 为余3码时,输出为1,否则为0, 34.仿照半加器和全加器的设计方法,试设计一半减器和一全减器,所用的门电路由自 己选定, 35,由4位数加法器74HC283构成的逻辑电路如图35所示,M和N为控制端,试分析 该电路的功能 h 图35 36.逻辑电路如图36所示,试分析该电路的功能

29.应用已介绍过的中规模组合逻辑电路设计一个数据传输电路,其功能是在 4 位通道 选择信号的控制下,能将 16 个输入数据中的任何一个传送到 16 个输出端中相对应的一个输 出端,其示意图如图 29 所示。 I0 I1 I15 Y0 Y1 Y15 通道选 择信号 通道选 择信号 图 29 30.试用五个双输入端或门和一个与门实现语句“A>B”,A 和 B 均为两位二进制数。 31.试设计一个 8 位相同数值比较器,当两数相等时,输出 L=1,否则 L=0。 32.试用数值比较器 74HC85 设计一个 8421BCD 码有效性测试电路,当输入为 8421BCD 码时,输出为 1,否则为 0。 33.试用数值比较器 74HC85 和必要的逻辑门设计一个余 3 码有效性测试电路,当输入 为余 3 码时,输出为 1,否则为 0。 34.仿照半加器和全加器的设计方法,试设计一半减器和一全减器,所用的门电路由自 己选定。 35.由 4 位数加法器 74HC283 构成的逻辑电路如图 35 所示,M 和 N 为控制端,试分析 该电路的功能。 S0 S1 S2 S3 =1 N M 0 S4 0 I2 I1 I3 I0A0 A1 A2A3 B0B1 B2 S0 S1 S2 S3 C1 74HC283 CO B3 & 图 35 36.逻辑电路如图 36 所示,试分析该电路的功能

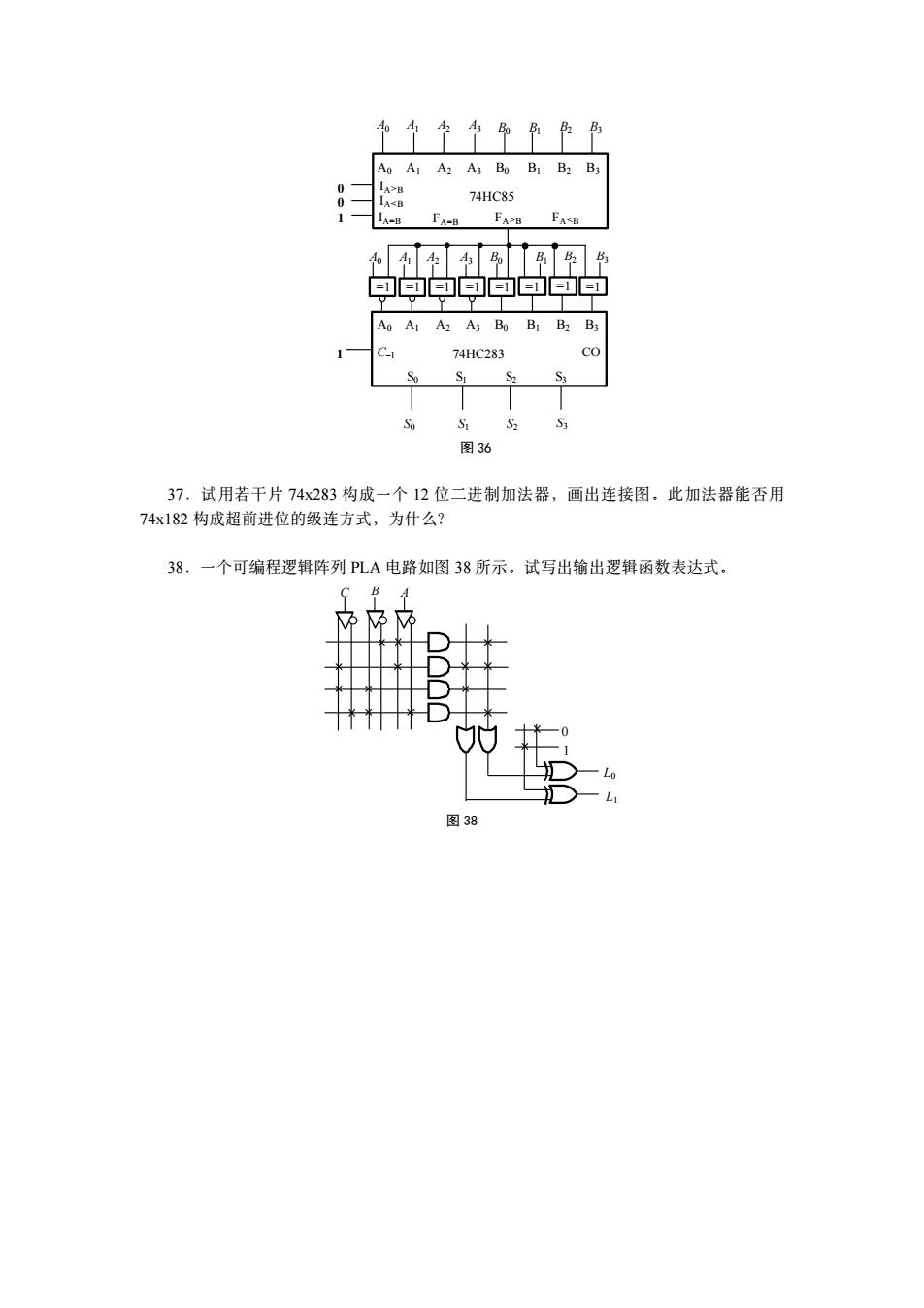

中4中中早色B Ao A A2 A3 Bo B1 B2 B3 0 1A<B 74HC85 1A-B FA-B =11111 Ao A A2 A3 Bo B1 B2 B3 C-1 74HC283 co So So S1 S2 S3 图36 37.试用若干片74x283构成一个12位二进制加法器,画出连接图。此加法器能否用 74x182构成超前进位的级连方式,为什么? 38.一个可编程逻辑阵列PLA电路如图38所示。试写出输出逻辑函数表达式。 B 图38

S0 S1 S2 S3 1 A0 A1 A2 A3 B0 B1 B2 B3 74HC283 S0 S1 S2 S3 0 C1 A0 A1 A2 A3 B0 B1 B2 B3 0 CO A0 A1 A2 A3 B0 B1 B2 B3 1 =1 =1 =1 =1 =1 =1 =1 =1 A0 A1 A2 A3 B0 B1 B2 B3 IA>B IA<B IA=B 74HC85 FA=B FA>B FA<B 图 36 37.试用若干片 74x283 构成一个 12 位二进制加法器,画出连接图。此加法器能否用 74x182 构成超前进位的级连方式,为什么? 38.一个可编程逻辑阵列 PLA 电路如图 38 所示。试写出输出逻辑函数表达式。 B A L1 L0 C 0 1 图 38