新疆大学电气工程学院 单片微机原理及应用课程课件 第2讲 MCS-51系列单片机硬件结构

第 讲 新疆大学电气工程学院 单片微机原理及应用课程课件 2 MCS-51系列单片机硬件结构

本讲主要内容: 2-1.51单片机总体概况 2-2. 微处理器 2-3.存储器 2-4. 定时器/计数器 2-5.并行和串行输入/输出接口 2-6 中断系统 Sichuan Engineering Technical College-1959 2 Copyright Http://mcu.scete.net

SiChuan Engineering Technical College-1959 2 Copyright © Http:// mcu.scetc.net 本讲主要内容: 2-1. 51单片机总体概况 2-2. 微处理器 2-3. 存储器 2-4. 定时器/计数器 2-5. 并行和串行输入/输出接口 2-6 中断系统

§2.1 总体概述 主要功能 51子系列的主要功能为: (1)8位CPU (2)片内带振荡器,振荡频率fsc范围为1.2~12MHz (3)128个字节的片内数据存储器。 (4)4K字节的片内程序存储器(8031无)。 (5)程序存储器的寻址范围为64K字节。 (6)片外数据存储器的寻址范围为64K字节。 (7)21个字节专用寄存器。 (8)4个8位并行1/0接口:P0,P1.P2.P30 (9)1个全双工串行1/0接口,可多机通信。 (10)2个16位定时器/计数器。 (11)中断系统有5个中断源,可编程为两个优先级。 (12)111条指令,含乘法指令和除法指令。 (13)有强的位寻址、位处理能力。 (14)片内采用单总线结构。 (15)用单一+5V电源。 SiChuan Engineering Technical College-1959 3 Copyright Http://mcu.scetc.net

SiChuan Engineering Technical College-1959 3 Copyright © Http:// mcu.scetc.net §2.1 总体概述 一、 主要功能 51子系列的主要功能为: (1)8位CPU (2)片内带振荡器,振荡频率fosc范围为1.2~12MHz (3)128个字节的片内数据存储器。 (4)4K字节的片内程序存储器 (8031无)。 (5)程序存储器的寻址范围为64K字节。 (6)片外数据存储器的寻址范围为64K字节。 (7)21个字节专用寄存器。 (8)4个 8位并行I/O接口:PO, Pl. P2. P30 (9)l个全双工串行 I/O接口,可多机通信。 (10)2个 16位定时器/计数器。 (11)中断系统有 5个中断源,可编程为两个优先级。 (12)111条指令,含乘法指令和除法指令。 (13)有强的位寻址、位处理能力。 (14)片内采用单总线结构。 (15)用单一+5V电源

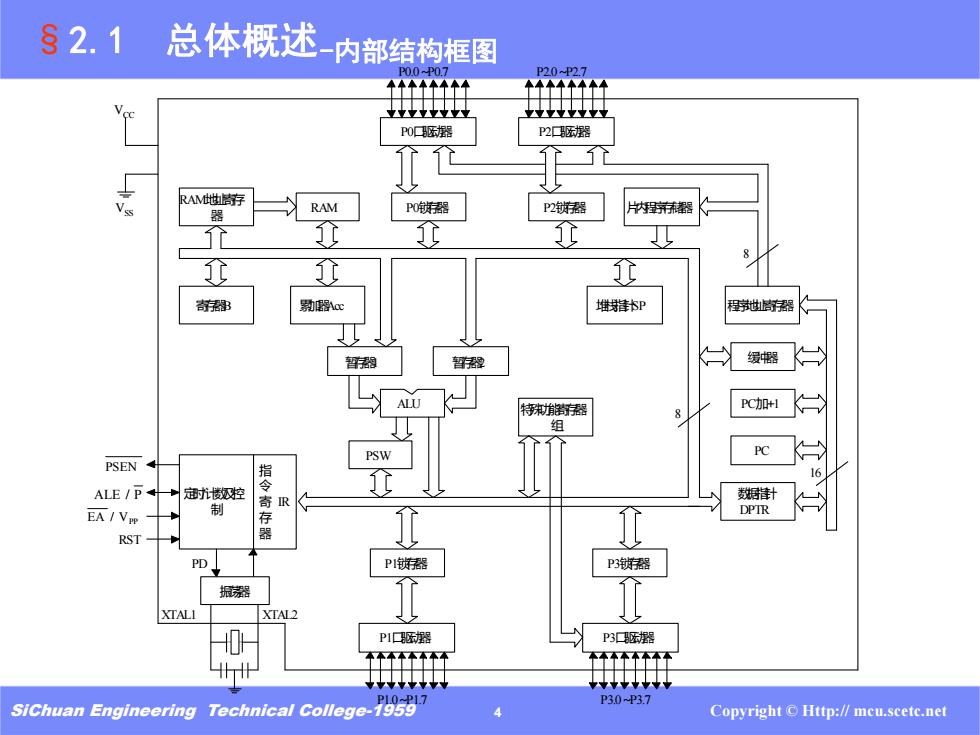

S2.1总体概述 内部结构框图 PU-07 P20-P7 个1个1个1个个 ↑1个个个个11 以 出过 PO胚器 P2☐旺器 RAv地出存 RAM 器 P0锁器 P2锁器 片大程带器 寄都 别E器c 增挂扑P 程地器 智程 智程 缓器 ALU 特能器 PC加+1 组 PSW PC PSEN ALE/P+寇时极控 数针 EA/V 制 存 DPTR RST PD PI锁器 P3锁器 振器 XTALI XTAL2 P1口旺露 P3■胚器 P30-P3.7 Sichuan Engineering Technical College-19597 Copyright Http://mcu.scete.net

SiChuan Engineering Technical College-1959 4 Copyright © Http:// mcu.scetc.net §2.1 总体概述-内部结构框图 P0口驱动器 P0.0~P0.7 RAM P0锁存器 RAM地址寄存 器 寄存器B 累加器Acc 暂存器1 暂存器2 ALU P2锁存器 P2口驱动器 P2.0~P2.7 特殊功能寄存器 组 堆栈指针SP 片内程序存储器 PSW 定时/计数及控 制 指 令 寄 存 器 振荡器 PD RST PSEN ALE / P VPP EA / XTAL1 XTAL2 P1口驱动器 P1.0~P1.7 P1锁存器 P3锁存器 P3口驱动器 P3.0~P3.7 程序地址寄存器 缓冲器 PC加+1 PC 数据指针 DPTR 8 16 8 VCC VSS IR

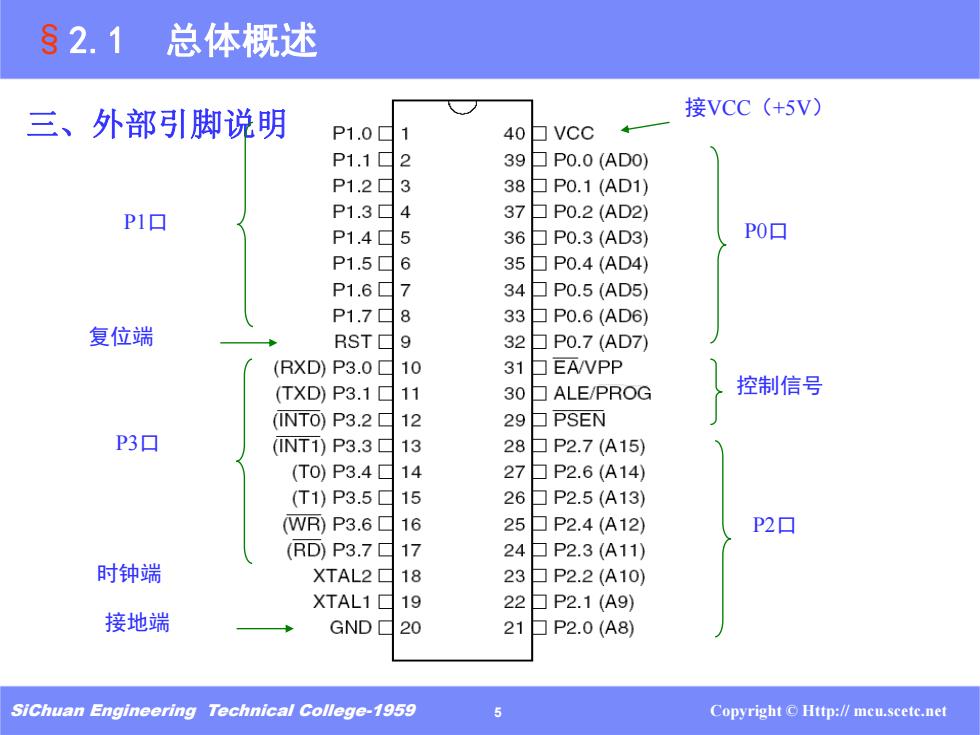

S2.1总体概述 三、外部引脚说明 接VCC(+5V) P1.0日1 40 ▣VCC P1.1日2 39 P0.0(AD0) P1.2日3 38 P0.1(AD1) P1口 P1.3日4 37 ◇ 0.2(AD2) P1.45 36 ▣P0.3(AD3) P0▣ P1.5g 6 35 P0.4(AD4) P1.6d7 34 P0.5(AD5) P1.7日8 33 P0.6(AD6) 复位端 RST□9 32 P0.7(AD7) (RXD)P3.0□10 31 EAPP (TXD)P3.111 30 ALE/PROG 控制信号 (INTO)P3.2 12 29 中PSEN P3口 NT1)P3.3日 13 28口P2.7(A15) (T0)P3.4□ 14 27 P2.6(A14) (T1)P3.5 1 26 ▣P2.5(A13) WP3.6□ 6 25 ▣P2.4(A12) P2▣ RD)P3.7□ 24 口P2.3(A11) 时钟端 XTAL2口 18 23 ▣P2.2(A10) XTAL1日19 2 P2.1(A9) 接地端 GND 20 27 ▣P2.0(A8) SiChuan Engineering Technical College-1959 5 Copyright Http://mcu.scetc.net

SiChuan Engineering Technical College-1959 5 Copyright © Http:// mcu.scetc.net §2.1 总体概述 三、外部引脚说明 P1口 P3口 P0口 P2口 时钟端 复位端 控制信号 接VCC(+5V) 接地端

S2.1总体概述 51架构(51 Architecture) XTAL2 A XTAL1 Vcc 时钟 定时/计数器 电路 ROM RAM n×16bit CPU Vss 串行通信接口 并行通信接口 总线控制 中断系统 全双工1个 4×8bit V RST EA ALE PSEN TXD RXD P0 P1 P2 P3 SiChuan Engineering Technical College-1959 Copyright Http://mcu.scete.net

SiChuan Engineering Technical College-1959 6 Copyright © Http:// mcu.scetc.net §2.1 总体概述 串行通信接口 全双工 1个 ROM TXD RXD 中断系统 并行通信接口 4×8bit 定时/计数器 n×16bit RAM 时 钟 电 路 CPU 总线控制 51架构(51 Architecture)

S2.1总体概述 三、外部引脚说明 ®1.I/0口线功能 4个8位并行1/0接▣引脚 P0.0P.7、P1.0P1.7、P20P2.7和P3.0P3.7 为多功能引脚,可自动切换用作数据总线、地址总线、控制总 线和或I/0接口外部引脚。 2.控制线 ALE/PROG: 地址锁存允许信号端,低电平信号为控制锁存P0输出的 低8位地址。 PSEN:外部程序存储器读选通信号端 EA/N加:程序存储器选择信号端和编程电源输入端(先片内再片外) SiChuan Engineering Technical College-1959 Copyright Http://mcu.scetc.net

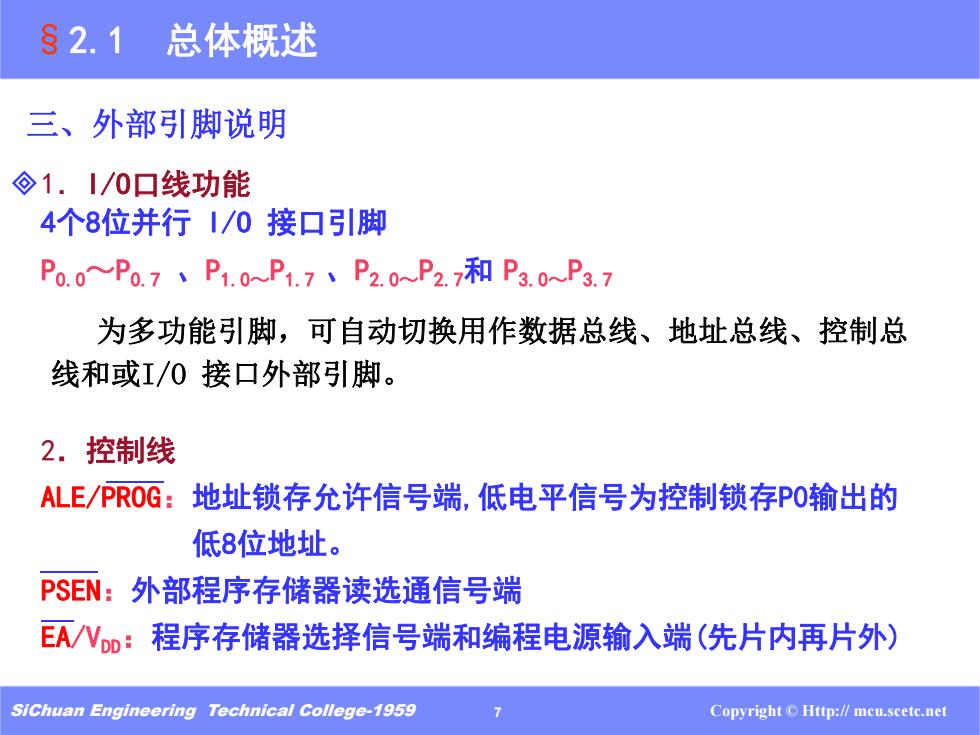

SiChuan Engineering Technical College-1959 7 Copyright © Http:// mcu.scetc.net ³1.I/O口线功能 4个8位并行 I/O 接口引脚 P0.0~P0.7 、P1.0~P1.7 、P2.0~P2.7和 P3.0~P3.7 为多功能引脚,可自动切换用作数据总线、地址总线、控制总 线和或I/O 接口外部引脚。 §2.1 总体概述 三、外部引脚说明 2.控制线 ALE/PROG:地址锁存允许信号端,低电平信号为控制锁存P0输出的 低8位地址。 PSEN:外部程序存储器读选通信号端 EA/VDD:程序存储器选择信号端和编程电源输入端(先片内再片外)

S2.1 总体概述 2.控制线 RST/VpD:复位信号端和后备电源输入端。 ®输入10ms以上高电平脉冲,单片机复位使单片机恢复到初始状态。 ®Vn使用后备电源,可实现掉电保护片内RAM的数据。 复位电路: 1)上电复位 2)外部信号复位 单片机 30uF 3 电源及时钟引线 工作电源:Vco、Vss 2002 RST 时钟输入:XTAL1、XTAL2。 Chuan Engineering Technical College-1959 Copyright Http://mcu.scete.net

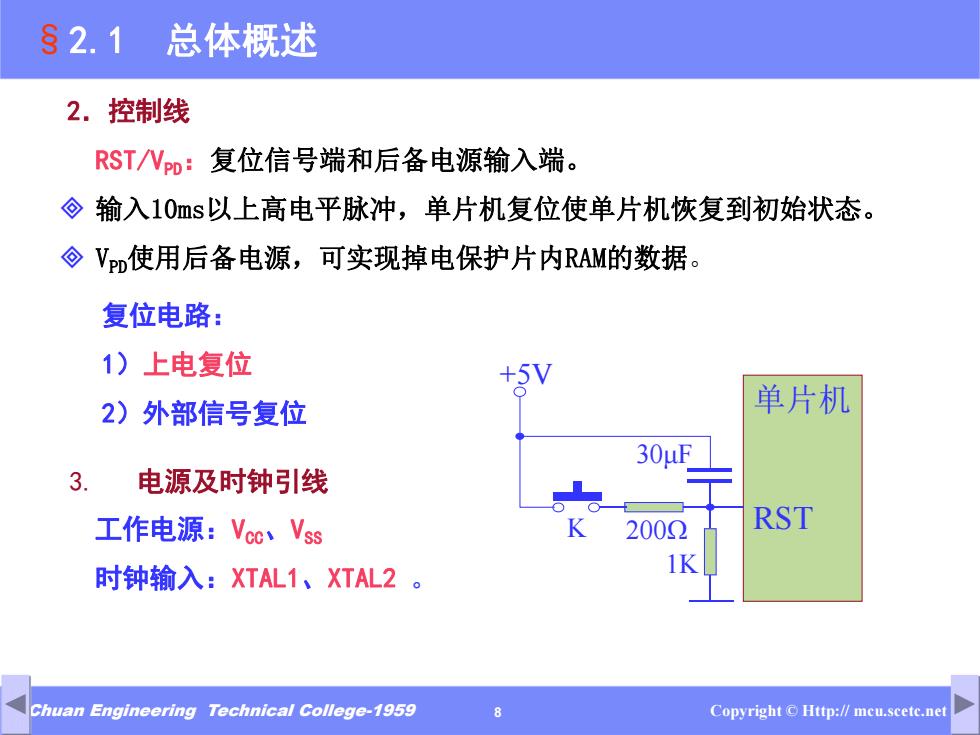

SiChuan Engineering Technical College-1959 8 Copyright © Http:// mcu.scetc.net 2.控制线 RST/VPD:复位信号端和后备电源输入端。 ³ 输入10ms以上高电平脉冲,单片机复位使单片机恢复到初始状态。 ³ VPD使用后备电源,可实现掉电保护片内RAM的数据。 3. 电源及时钟引线 工作电源:VCC、VSS 时钟输入:XTAL1、XTAL2 。 复位电路: 1)上电复位 2)外部信号复位 单片机 K RST +5V 200Ω 1K 30μF §2.1 总体概述

表2-2引脚功能 引脚编号 引脚名称 类 DIP40 LCC44 QFP44 功能说明 Vss 20 22 16 电源地 Vec 40 44 38 电源引脚。正常操作、空闲、掉电以及对EPROM 编程或校验工作电压。2.7~6.0V(89C5X、 89C5XX2电源电压一般为5.0V) P0.0P0.7 39~32 4336 37~30 VO P0口:作为/O口使用时,P0口是漏极开路双 向口,向口锁存器写入1,VO引脚将悬空,可作 高阻输入引脚:在读写外部存储器时,P0口作为 “低8位地址/数据”总线使用 P1.0P1.7 1~8 2~9 40~44 I/O P1口:内部带有弱上拉的双向/O口,作为输 1-3 入引脚使用前,先向P1口锁存器写入1,使P1 口引脚被上拉为高电平 P1.0、P11引脚除了作为一般/0引脚使用外, 还具有第二输入/输出功能: T2(P1.0)一定时器T2的计数输入端或定时器 T2的时钟输出端 T2EXP1.1)一定时器T2外部触发输入端 P2.0P2.7 21-28 24~31 18-25 P2口:内部带有弱上拉的双向/0口,作为输 入引脚使用前,先向P2口锁存器写入1,使P2 口引脚被上拉为高电平 在读写外部存储器时,P2口输出高8位地址 A15~A8 SiChuan Engineering Technical College-1959 Copyright O Http://mcu.scete.net

SiChuan Engineering Technical College-1959 9 Copyright © Http:// mcu.scetc.net 表2-2 引脚功能

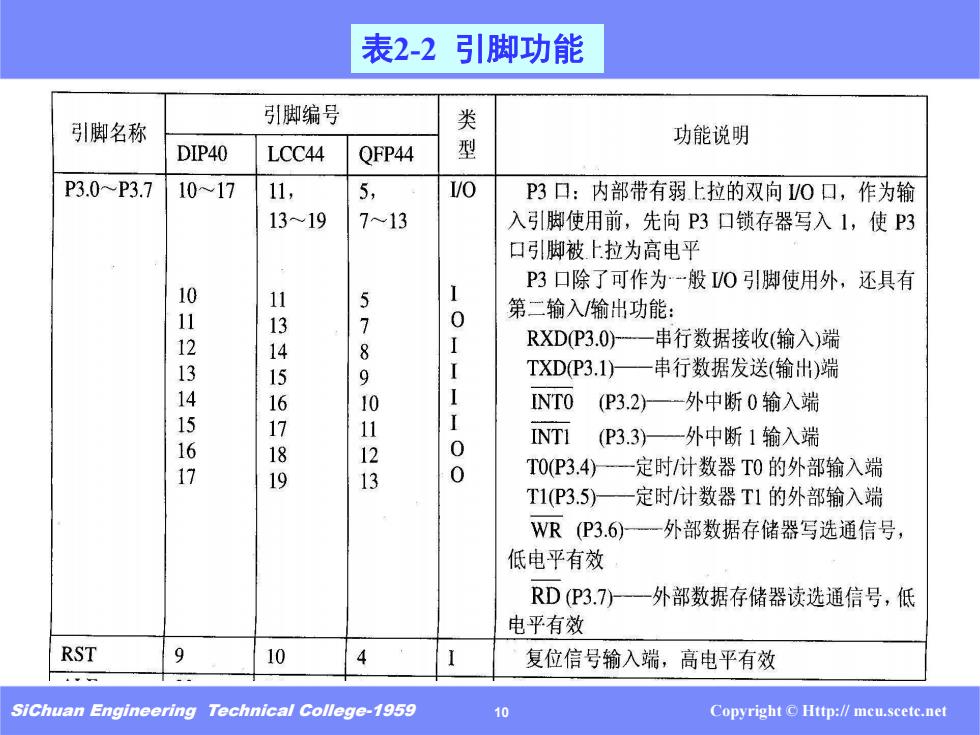

表2-2引脚功能 引脚名称 引脚编号 DIP40 LCC44 QFP44 型 功能说明 P3.0~P3.7 1017 11, 5, V/O P3口:内部带有弱上拉的双向/O口,作为输 1319 7~13 入引脚使用前,先向P3口锁存器写入1,使P3 口引脚被上拉为高电平 P3口除了可作为一般/O引脚使用外,还具有 11 5 0 第二输入输出功能: 01234567 3456789 8 I RXDP3.0)—串行数据接收(输入)端 9 TXD(P3.1) 串行数据发送(输出)端 10 INTO (P3.2)一外中断0输入端 I 11213 0 NT1(P3.3)一外中断1输入端 0 T0P3.4)一定时计数器T0的外部输入端 T1P3.5)—定时/计数器T1的外部输入端 W℉(P3.6)一外部数据存储器写选通信号, 低电平有效 RD(P3.7)一外部数据存储器读选通信号,低 电平有效 RST 9 10 复位信号输入端,高电平有效 Sichuan Engineering Technical College-1959 Copyright Http://mcu.scete.net

SiChuan Engineering Technical College-1959 10 Copyright © Http:// mcu.scetc.net 表2-2 引脚功能