freescale semiconductor 第8章队列式串行外设接口QSPI V1.0 2009.2

第8章 队列式串行外设接口QSPI V1.0 2009.2

本章目录 8.1 SPI的基本工作原理 8.2 MCF52233队列串行外设接▣QSPI模块编程 结构 8.3 MCF52233的串行外设接口QSPI模块编程实 例

本章目录 8.1 SPI的基本工作原理 MCF52233队列串行外设接口QSPI模块编程 结构 8.2 MCF52233的串行外设接口QSPI模块编程实 例 8.3

8.1SPI的基本工作原理 8.1.1SPI基本概念 串行外设接口(SPI,Serial Peripheral Interface)是Freescale:公司推出的一种同 步串行通讯接口,用于微处理器和外围扩展芯片之间的串行连接,现已发展成为一种工 业标准。 1.主机-从机(Master-Slave) 提供sPI串行时钟的SPI设备称为SPI主机或主设备(Master),其它设备则称为SPI 从机或从设备(Slave)。 2.从机选择引脚(Slave Select) 若一个MCU的SPI工作于主机方式,则置该MCU的为高电平。若一个MCU的SPI工 作于从机方式,当=0时表示主机选中了该从机,反之则未选中该从机。 3.主出从入引脚MoSI(Master Out/Slave In) 主出从入引脚MOS是主机输出、从机输入数据线。 4.主入从出引脚MISO(Master In/Slave Out) 主入从出引脚MISO是主机输入、从机输出数据线。 5.SPI串行时钟引脚SPSCK(SPI Serial Clock) SPI串行时钟引脚SPSCK用于控制主机与从机之间的数据传输。 6.时钟极性 表示时钟信号在空闲时是高电平还是低电平。 7.时钟相位 决定数据是在SPSCK的上升沿采样还是在SPSCK的下降沿采样

8.1 SPI的基本工作原理 8.1.1 SPI基本概念 串行外设接口(SPI,Serial Peripheral Interface)是Freescale公司推出的一种同 步串行通讯接口,用于微处理器和外围扩展芯片之间的串行连接,现已发展成为一种工 业标准。 1.主机-从机(Master-Slave) 提供SPI串行时钟的SPI设备称为SPI主机或主设备(Master),其它设备则称为SPI 从机或从设备(Slave)。 2.从机选择引脚 (Slave Select) 若一个MCU的SPI工作于主机方式,则置该MCU的 为高电平。若一个MCU的SPI工 作于从机方式,当 =0时表示主机选中了该从机,反之则未选中该从机。 3.主出从入引脚MOSI(Master Out/Slave In) 主出从入引脚MOSI是主机输出、从机输入数据线。 4.主入从出引脚MISO(Master In/Slave Out) 主入从出引脚MISO是主机输入、从机输出数据线。 5.SPI串行时钟引脚SPSCK(SPI Serial Clock) SPI串行时钟引脚SPSCK用于控制主机与从机之间的数据传输。 6.时钟极性 表示时钟信号在空闲时是高电平还是低电平。 7.时钟相位 决定数据是在SPSCK的上升沿采样还是在SPSCK的下降沿采样

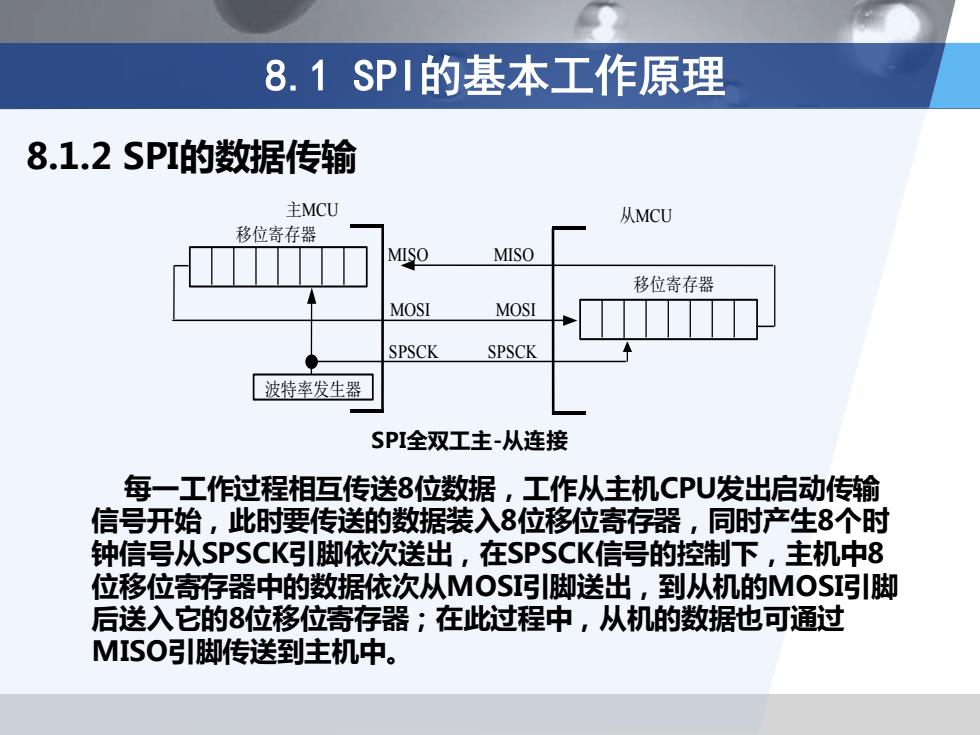

8.1SPI的基本工作原理 8.1.2SPI的数据传输 主MCU 从MCU 移位寄存器 MISO MISO 移位寄存器 MOSI MOSI SPSCK SPSCK 波特率发生器 SPI全双工主-从连接 每一工作过程相互传送8位数据,工作从主机CPU发出启动传输 信号开始,此时要传送的数据装入8位移位寄存器,同时产生8个时 钟信号从SPSCK引脚依次送出,在SPSCK信号的控制下,主机中8 位移位寄存器中的数据依次从MOS1引脚送出,到从机的MOSI引脚 后送入它的8位移位寄存器;在此过程中,从机的数据也可通过 MISO引脚传送到主机中

8.1.2 SPI的数据传输 8.1 SPI的基本工作原理 MISO MISO 主MCU MOSI MOSI 波特率发生器 从MCU SPSCK SPSCK 移位寄存器 移位寄存器 SPI全双工主-从连接 每一工作过程相互传送8位数据,工作从主机CPU发出启动传输 信号开始,此时要传送的数据装入8位移位寄存器,同时产生8个时 钟信号从SPSCK引脚依次送出,在SPSCK信号的控制下,主机中8 位移位寄存器中的数据依次从MOSI引脚送出,到从机的MOSI引脚 后送入它的8位移位寄存器;在此过程中,从机的数据也可通过 MISO引脚传送到主机中

8.1SPI的基本工作原理 8.1.3SPI模块的时序 SPI的数据传输是在时钟信号SPSCK(同步信号) 的控制下完成的。 数据传输过程涉及到时钟相位与时钟极性两个概念。 CPHA表达时钟相位,CPOL表达时钟极性。 总体要求是:确保发送数据在一周期开始的时刻上 线,接收方在1/2周期的时刻从线上取数,这样是最 稳定的通信方式

8.1.3 SPI模块的时序 8.1 SPI的基本工作原理 SPI的数据传输是在时钟信号SPSCK(同步信号) 的控制下完成的。 数据传输过程涉及到时钟相位与时钟极性两个概念。 CPHA表达时钟相位,CPOL表达时钟极性。 总体要求是:确保发送数据在一周期开始的时刻上 线,接收方在1/2周期的时刻从线上取数,这样是最 稳定的通信方式

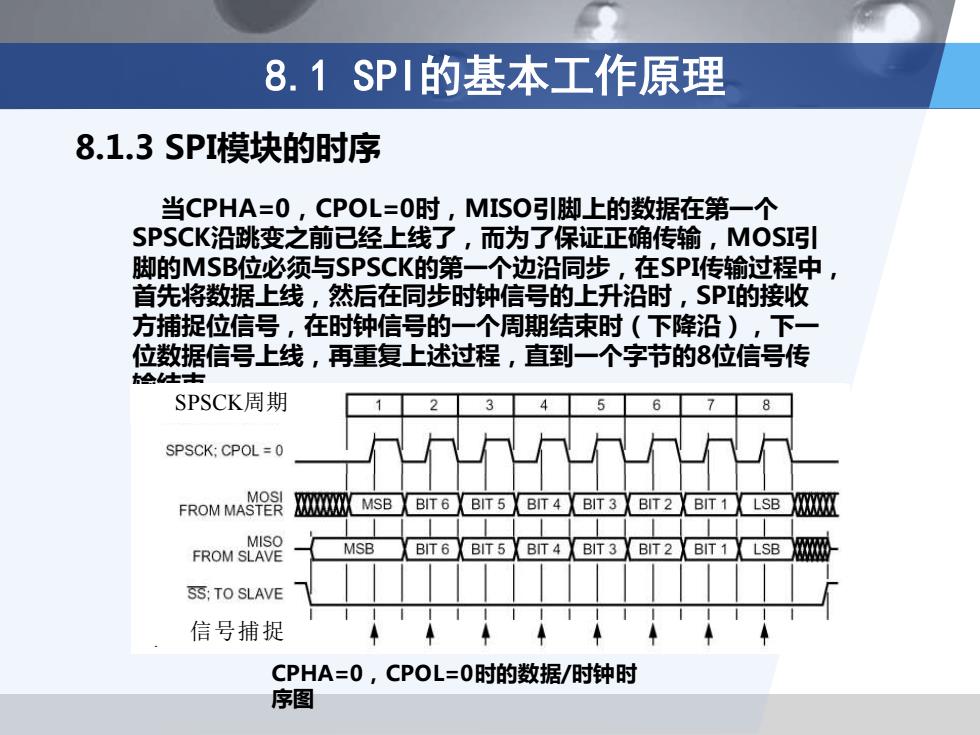

8.1SPI的基本工作原理 8.1.3SPI模块的时序 当CPHA=0,CPOL=0时,MISO引脚上的数据在第一个 SPSCK沿跳变之前已经上线了,而为了保证正确传输,MOSI引 脚的MSB位必须与SPSCK的第一个边沿同步,在SPI传输过程中, 首先将数据上线,然后在同步时钟信号的上升沿时,SPI的接收 方捕捉位信号,在时钟信号的一个周期结束时(下降沿),下一 位数据信号上线,再重复上述过程,直到一个字节的8位信号传 h△士-与 SPSCK周期 3 4 5 6 SPSCK:CPOL =0 FROM MAST2器 XX MSB BITG (BIT 5 BIT 4 MIsO FROM SLAVE MSB (BIT 6X BIT 5 BIT 4 BIT 3 X BIT 2 X BIT 1 LSB SS:TO SLAVE 信号捕捉 CPHA=0,CPOL=0时的数据/时钟时 序图

8.1.3 SPI模块的时序 当CPHA=0,CPOL=0时,MISO引脚上的数据在第一个 SPSCK沿跳变之前已经上线了,而为了保证正确传输,MOSI引 脚的MSB位必须与SPSCK的第一个边沿同步,在SPI传输过程中, 首先将数据上线,然后在同步时钟信号的上升沿时,SPI的接收 方捕捉位信号,在时钟信号的一个周期结束时(下降沿),下一 位数据信号上线,再重复上述过程,直到一个字节的8位信号传 输结束。 SPSCK周期 信号捕捉 点 CPHA=0,CPOL=0时的数据/时钟时 序图 8.1 SPI的基本工作原理

8.1SPI的基本工作原理 8.1.3SPI模块的时序 3 4 5 6 8 SPSCK:CPOL =1 MOSI FROM MASTER BIT 6 BIT 5 BIT 4 BIT 3 BIT2 BIT 1 LSB MISO FROM SLAVE MSB BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 LSB SS:TO SLAVE 信号捕捉 CPHA=0,CPOL=1时的数据/时钟时序 图

8.1.3 SPI模块的时序 8.1 SPI的基本工作原理 信号捕捉 CPHA=0,CPOL=1时的数据/时钟时序 图

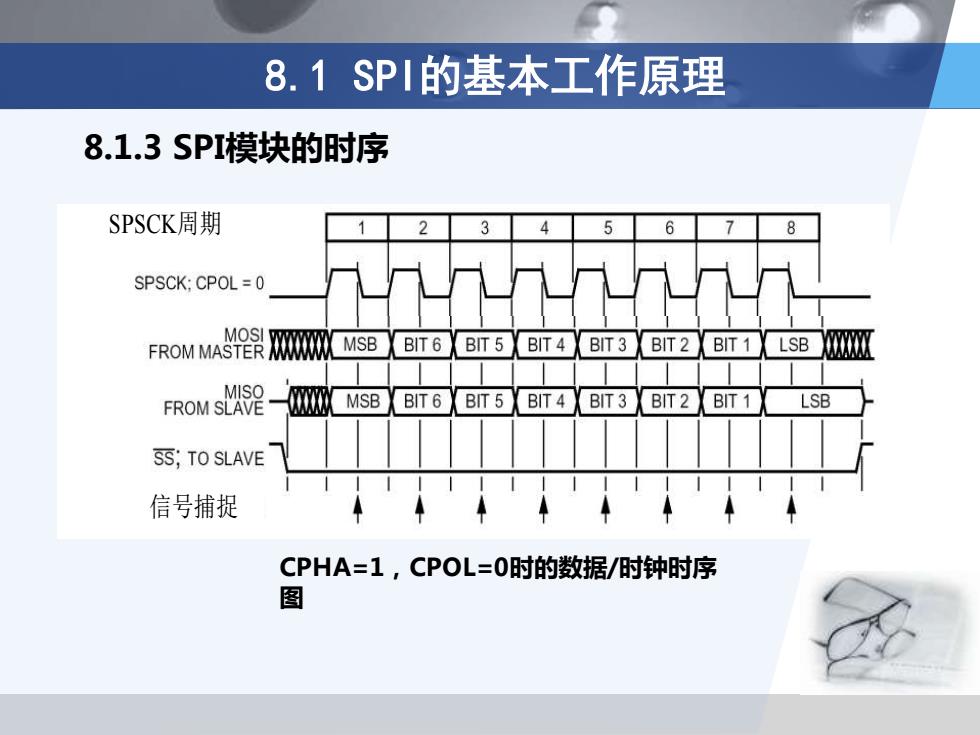

8.1SPI的基本工作原理 8.1.3SPI模块的时序 SPSCK)周期 5 6 8 SPSCK:CPOL=0 FROM MAS MSB BIT 6X BIT 5 BIT 4 X BIT 3 BIT 2 BIT 1 LSB M MISO FROM SLAVE LSB SS;TO SLAVE 信号捕捉 CPHA=1,CPOL=O时的数据/时钟时序 图

8.1.3 SPI模块的时序 8.1 SPI的基本工作原理 SPSCK周期 信号捕捉 CPHA=1,CPOL=0时的数据/时钟时序 图

8.1SPI的基本工作原理 8.1.3SPI模块的时序 SPSCK周期 2 4 6 8 SPSCK:CPOL =1 FROM MASMSB XBIT 6X BIT 5 BIT 4 BIT 3 X BIT 2 BIT 1X LSB FROM S然e-MSBBIT6BT5 BIT 4 X BIT 3 X BIT 2 BIT 1 LSB SS;TO SLAVE 信号捕捉 CPHA=1,CPOL=1时的数据/时钟时 序图

8.1.3 SPI模块的时序 8.1 SPI的基本工作原理 SPSCK周期 信号捕捉 点 CPHA=1,CPOL=1时的数据/时钟时 序图

8.1SPI的基本工作原理 8.1.4模拟SPI 对于不带SPI串行总线接口的MCU来 说,可以使用软件来模拟SPI的操作。 举例说明,我们可以使用三个普通/O 口,分别定义为pin_SPSCK、 pin_MISO、pin_MOSI来模拟SPI器件 的SPSCK、MISO、MOSI

8.1.4 模拟SPI 对于不带SPI串行总线接口的MCU来 说,可以使用软件来模拟SPI的操作。 举例说明,我们可以使用三个普通I/O 口,分别定义为pin_SPSCK、 pin_MISO、pin_MOSI来模拟SPI器件 的SPSCK、MISO、MOSI。 8.1 SPI的基本工作原理