第七章 基本逻辑电路设计

第七章 基本逻辑电路设计

主要内容 。组合逻辑电路和时序逻辑的概念; ·组合逻辑电路设计实例; ·时序逻辑电路设计实例

主要内容 • 组合逻辑电路和时序逻辑的概念; • 组合逻辑电路设计实例; • 时序逻辑电路设计实例

基本概念 数逻辑电路主要分为组合逻辑电路与时序逻辑 电路两类 ·两者都拥有一个或者多个输入信号和输出信号, 但是组合逻辑电路的输出只与当前的输入相关, 而时序逻辑电路的输出不仅与现在的输入信号相 关,而且与过去的输入信号相关: ● 两种逻辑电路都是数字电路系统的重要基本组成 部分,是数字系统电路的基本元素

基本概念 • 数字逻辑电路主要分为组合逻辑电路与时序逻辑 电路两类 ; • 两者都拥有一个或者多个输入信号和输出信号, 但是组合逻辑电路的输出只与当前的输入相关, 而时序逻辑电路的输出不仅与现在的输入信号相 关,而且与过去的输入信号相关; • 两种逻辑电路都是数字电路系统的重要基本组成 部分,是数字系统电路的基本元素

7.1组合逻辑电路设计 7,7,1、译码器 界养星靠警鲍萨鼠霸湾 制地址码作为输入」 译码需和416译码器。 3-8译码器的核心代码如下: ENTITY decoder IS PORT(A,B,C,Enable IN STD_LOGIC; Y:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END decoder; ARCHITECTURE fun OF decoder IS SIGNAL input:STD_LOGIC_VECTOR(2 DOWNTO 0); BEGIN input<=C&B&A; PROCESS(input,Enable) BEGIN IF(Enable:='1)THEN-使能输入高电平有效

7.1 组合逻辑电路设计 7.7.1、译码器 译码器通常用来产生存储器或者外设的片选信号,也就是说将二进 制地址码作为输入,并产生多个选择信号输出 。典型的译码器有3-8 译码器和4-16译码器 。 3-8译码器的核心代码如下: ENTITY decoder IS PORT(A,B,C,Enable : IN STD_LOGIC; Y: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END decoder; ARCHITECTURE fun OF decoder IS SIGNAL input: STD_LOGIC_VECTOR(2 DOWNTO 0); BEGIN input<=C&B&A; PROCESS(input,Enable) BEGIN IF (Enable='1') THEN --使能输入高电平有效

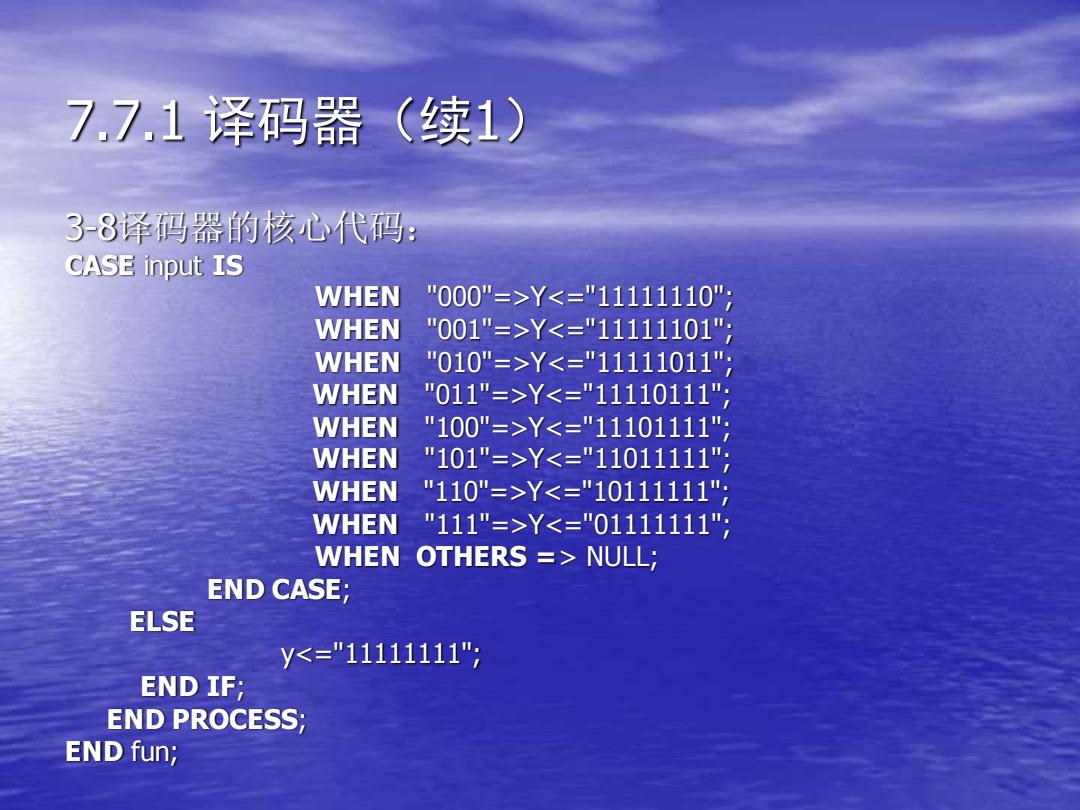

7.7.1译码器 (续1) 3-8译码器的核心代码: CASE input IS WHEN"000"=>YYYYYYYY<="01111111" WHEN OTHERS =NULL; END CASE; ELSE y<="11111111": END IF; END PROCESS; END fun;

7.7.1 译码器(续1) 3-8译码器的核心代码: CASE input IS WHEN "000"=>YYYYYYYY NULL; END CASE; ELSE y<="11111111"; END IF; END PROCESS; END fun;

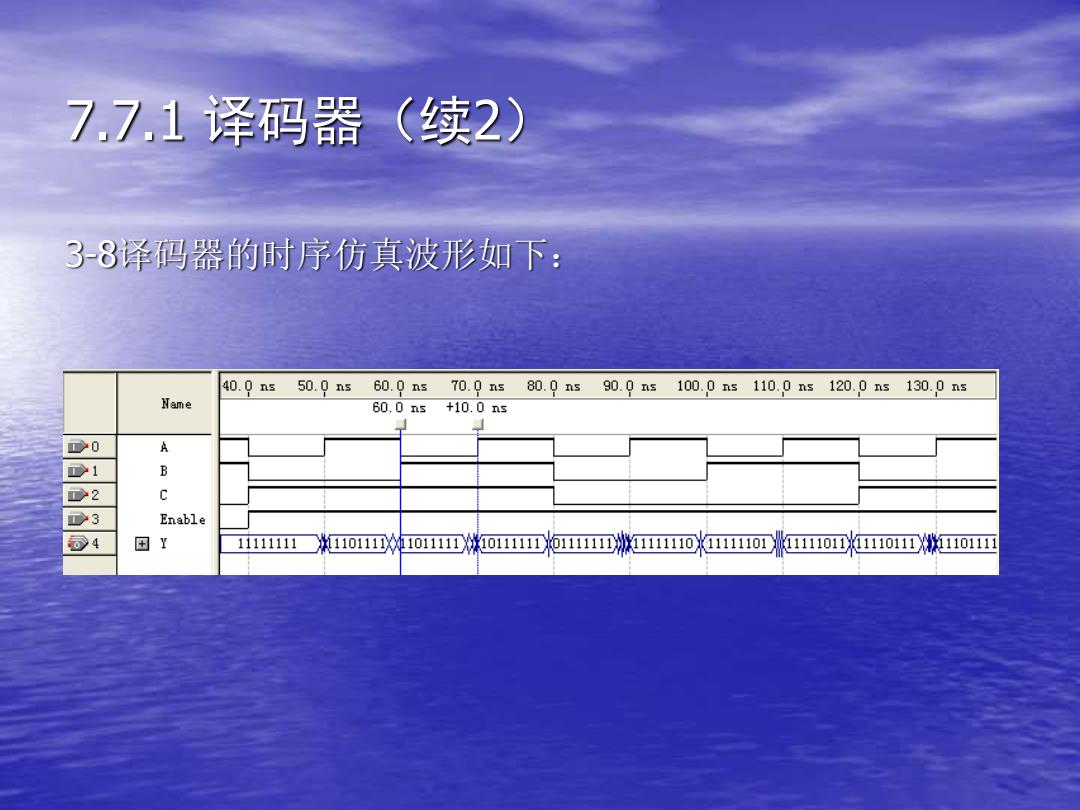

7.7.1译码器(续2) 3-8泽码器的时序仿真波形如下: 40.0s50.9ns60.0ns70.9ns80.9ns90.9ns100.0ns110.0ns120.0ns130.0s Name 60.0ns+10,0ns 0 A 1 B 工2 3 Enable 司4 国Y 11111111☐11011①1101111四o11111四111111搬1111110111110四111101四111011四11011工

7.7.1 译码器(续2) 3-8译码器的时序仿真波形如下:

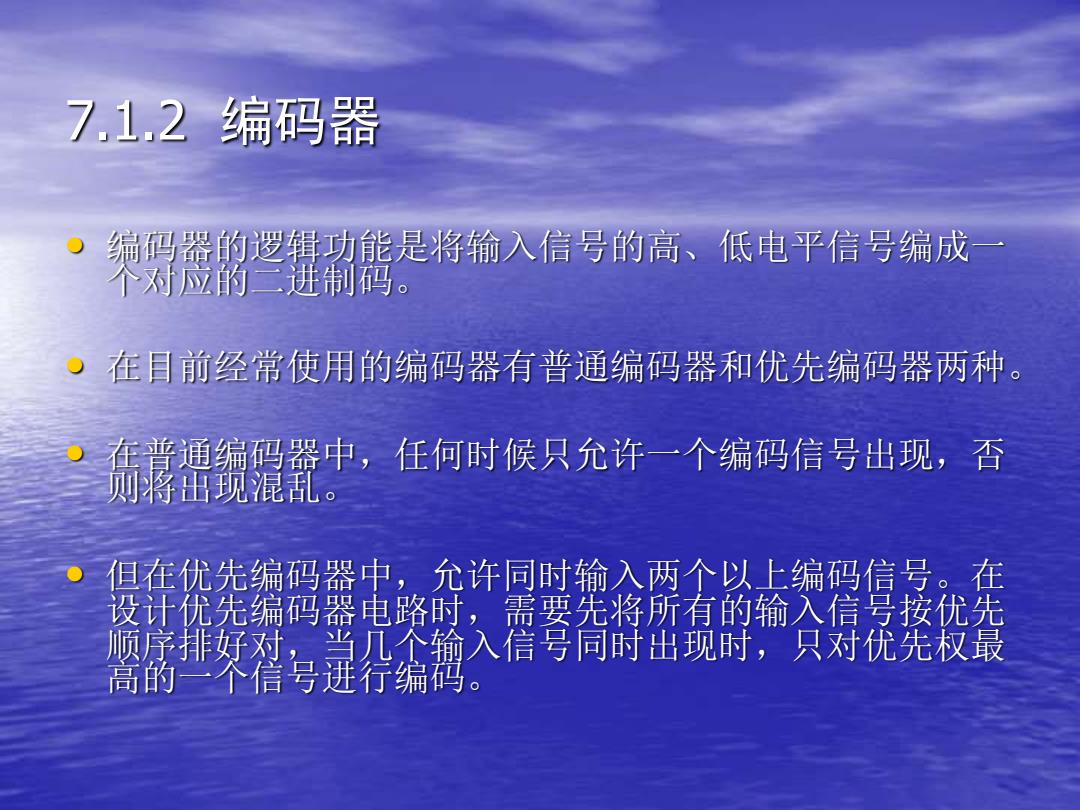

7.1.2编码器 编码器的逻辑功能是将输入信号的高、低电平信号编成 个对应的三进制码。 ·在目前经常使用的编码器有普通编码器和优先编码器两种。 ·在普通编码器中,任何时候只允许一个编码信号出现,否 测将出现混乱。 ·但在优先编码器中,允许同时输入两个以上编码信号。在 设计优先编码器电路时,需要先将所有的输入信号按优先 顺序排好对,当几个输入信号同时出现时,只对优先权最 高的一个信号进行编码

7.1.2 编码器 • 编码器的逻辑功能是将输入信号的高、低电平信号编成一 个对应的二进制码。 • 在目前经常使用的编码器有普通编码器和优先编码器两种。 • 在普通编码器中,任何时候只允许一个编码信号出现,否 则将出现混乱。 • 但在优先编码器中,允许同时输入两个以上编码信号。在 设计优先编码器电路时,需要先将所有的输入信号按优先 顺序排好对,当几个输入信号同时出现时,只对优先权最 高的一个信号进行编码

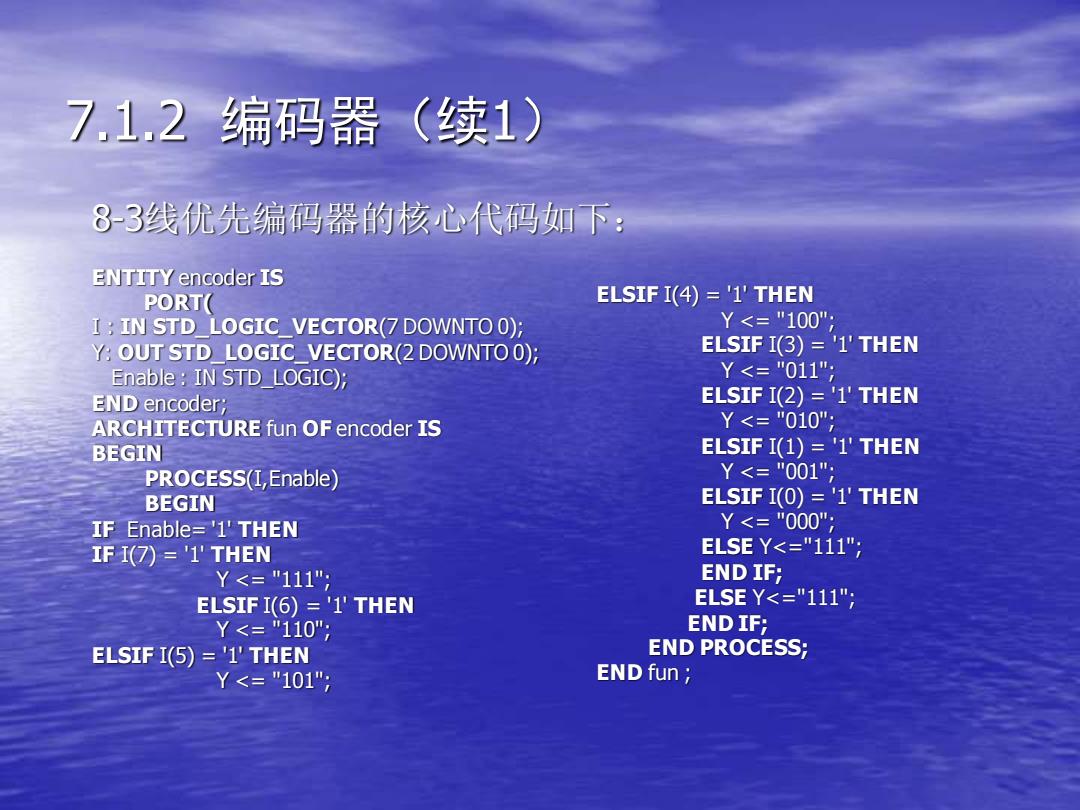

7.1.2编码器(续1) 8-3线优先编码器的核心代码如下: ENTITY encoder IS PORT ELSIF I(4)='1'THEN I:IN STD LOGIC VECTOR(7 DOWNTO 0); Y<="100", Y:OUT STD LOGIC VECTOR(2 DOWNTO0); ELSIF I(3)=1'THEN Enable IN STD_LOGIC); Y<="011" END encoder; ELSIF I(2)='1'THEN ARCHITECTURE fun OF encoder IS Y<="010": BEGIN ELSIFI(1)='1'THEN PROCESS(I,Enable) Y<="001" BEGIN ELSIF I(O)='1'THEN IF Enable='1'THEN Y<="000" IFI(7)='1'THEN ELSE Y<="111"; Y<="111" END IF; ELSIFI(6)='1'THEN ELSE Y<="111": Y<="110" END IF; ELSIF I(5)='1'THEN END PROCESS; Y<="101" END fun;

7.1.2 编码器(续1) 8-3线优先编码器的核心代码如下: ENTITY encoder IS PORT( I : IN STD_LOGIC_VECTOR(7 DOWNTO 0); Y: OUT STD_LOGIC_VECTOR(2 DOWNTO 0); Enable : IN STD_LOGIC); END encoder; ARCHITECTURE fun OF encoder IS BEGIN PROCESS(I,Enable) BEGIN IF Enable= '1' THEN IF I(7) = '1' THEN Y <= "111"; ELSIF I(6) = '1' THEN Y <= "110"; ELSIF I(5) = '1' THEN Y <= "101"; ELSIF I(4) = '1' THEN Y <= "100"; ELSIF I(3) = '1' THEN Y <= "011"; ELSIF I(2) = '1' THEN Y <= "010"; ELSIF I(1) = '1' THEN Y <= "001"; ELSIF I(0) = '1' THEN Y <= "000"; ELSE Y<="111"; END IF; ELSE Y<="111"; END IF; END PROCESS; END fun ;

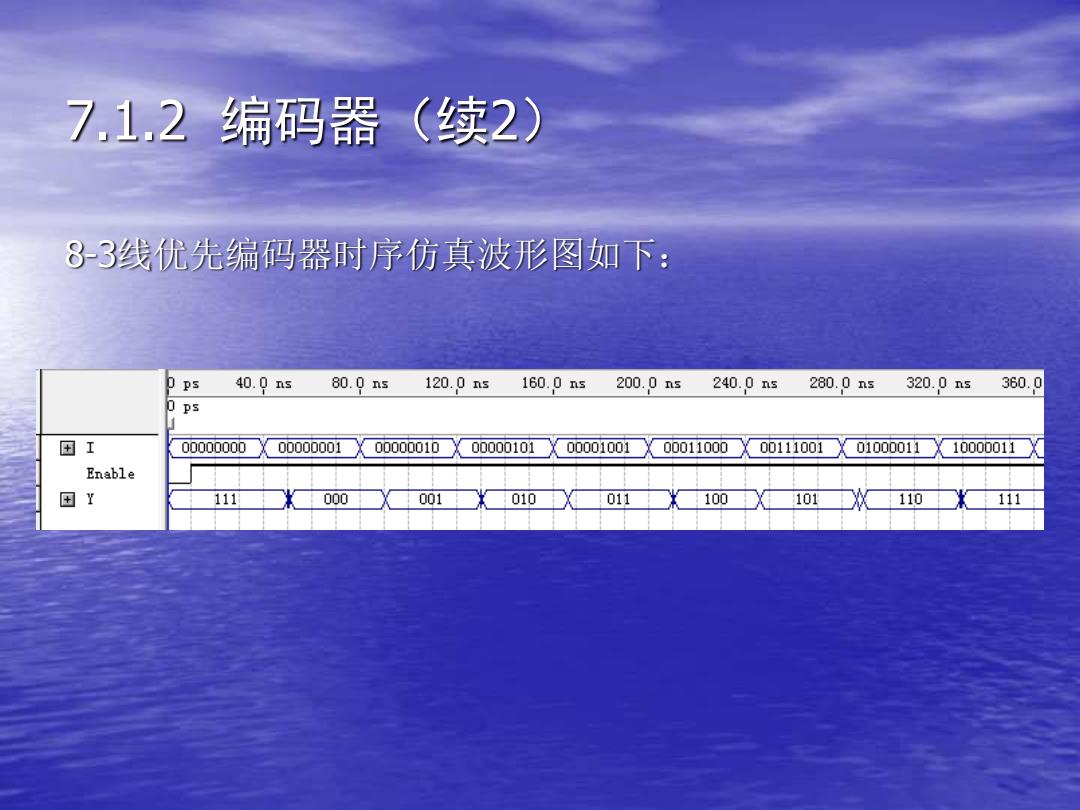

7.1.2编码器(续2) 8-3线优先编码器时序仿真波形图如下: ps 40.0ns80.0ns120.0ns160.0ns200.0ns 240.0ns280.0ns320.0ns360.0 0 ps 田I 00000000X00000001X00000010¥00000101X00001001X00011000X00111001¥01000011X10000011X Enable 田Y 111 000 001 010W 011 100 101 110 111

7.1.2 编码器(续2) 8-3线优先编码器时序仿真波形图如下:

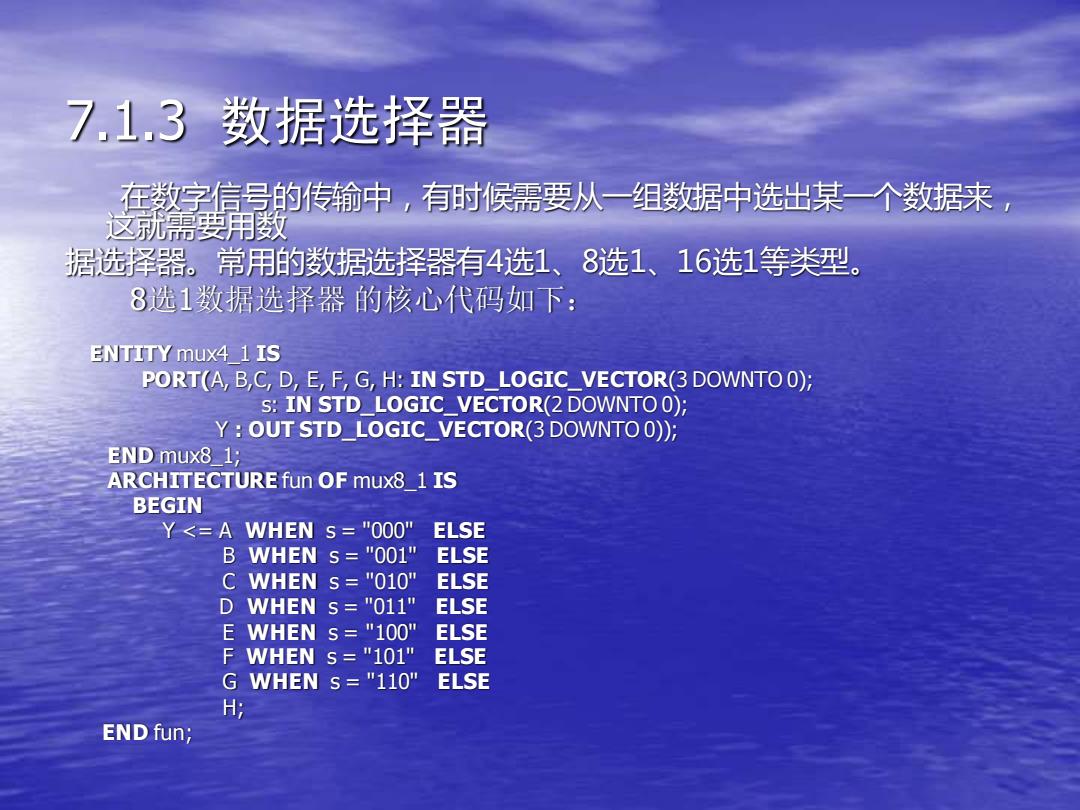

7.1.3 数据选择器 在数字信号的传输中,有时候需要从一组数据中选出某一个数据来 这就需要数 据选择器。 常用的数据选择器有4选1、8选1、16选1等类型! 8选1数据选择器的核心代码如下: ENTITY mux4 1 IS PORT(A,B,C,D,E,F,G,H:IN STD_LOGIC_VECTOR(3 DOWNTO0); s:IN STD LOGIC_VECTOR(2 DOWNTO0); Y:OUT STD LOGIC_VECTOR(3 DOWNTO0)); END mux8 1; ARCHITECTURE fun OF mux8_1 IS BEGIN Y<=A WHEN s="000"ELSE B WHEN s="001"ELSE C WHEN S="010"ELSE D WHEN s="011"ELSE E WHEN s="100"ELSE F WHEN s="101"ELSE G WHEN s="110"ELSE H出 END fun;

7.1.3 数据选择器 在数字信号的传输中,有时候需要从一组数据中选出某一个数据来, 这就需要用数 据选择器。常用的数据选择器有4选1、8选1、16选1等类型。 8选1数据选择器 的核心代码如下: ENTITY mux4_1 IS PORT(A, B,C, D, E, F, G, H: IN STD_LOGIC_VECTOR(3 DOWNTO 0); s: IN STD_LOGIC_VECTOR(2 DOWNTO 0); Y : OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); END mux8_1; ARCHITECTURE fun OF mux8_1 IS BEGIN Y <= A WHEN s = "000" ELSE B WHEN s = "001" ELSE C WHEN s = "010" ELSE D WHEN s = "011" ELSE E WHEN s = "100" ELSE F WHEN s = "101" ELSE G WHEN s = "110" ELSE H; END fun;