第四章 VHDL编程基础

第四章 VHDL编程基础

主要内容 硬件描述语言及其特点 ·HDL程序基本结构 ·VHDL语言要素 ·VHDL结构体描述方式

主要内容 • 硬件描述语言及其特点 • VHDL程序基本结构 • VHDL语言要素 • VHDL结构体描述方式

4.1 硬件描述语言及其特点 4,1,1硬件描述语言的基本概念 硬件描述语言很好地解决了文本语言描述和逻辑图描述存在 的不足。它 长】 子逼过精定义的句描述网量工 司以通过纤算机仿真设计好的逻辑网络,而直仿真中包含了硬 件特性。 4,1.2常用硬件描述语言简介 具前常用的硬件描述语言有VHDL、Verilog、.AHDL和ABEL 语言。 VHDL的英文全名是VHSIC(Very High Speed Integrated Circuit)Hardware Description Language,l982年发源于美 国防部一1987年底被和美国防部认为标准硬件语言。 1993年EEE对VHDL进行了修订,公布了新版本的VHDL 即IEEE标准的1076-1993版本

4.1 硬件描述语言及其特点 4.1.1 硬件描述语言的基本概念 硬件描述语言很好地解决了文本语言描述和逻辑图描述存在 的不足。它是一种类似于C、C++的计算机高级语言,允许设 计者通过精确定义的语句描述逻辑网络的任何操作,更重要的 可以通过计算机仿真设计好的逻辑网络,而且仿真中包含了硬 件特性。 4.1.2 常用硬件描述语言简介 目前常用的硬件描述语言有 VHDL、Verilog、AHDL和 ABEL 语言。 VHDL 的英文全名是VHSIC(Very High Speed Integrated Circuit)Hardware Description Language, 1982年发源于美 国国防部,1987年底被和美国国防部确认为标准硬件描述语言。 1993年,IEEE 对 VHDL 进行了修订,公布了新版本的 VHDL, 即 IEEE 标准的1076-1993版本

4.1 硬件描述语言及其特点(续) 4,1.3 DL特点 ·DL具有更强的行为描述能力 支持团队设计模式 ·系统设计与硬件结构无关 ·具有较强的预测能力 ·自动化程度高 ·具有极强的移植能力

4.1 硬件描述语言及其特点(续) 4.1.3 VHDL特点 • VHDL具有更强的行为描述能力 • 支持团队设计模式 • 系统设计与硬件结构无关 • 具有较强的预测能力 • 自动化程度高 • 具有极强的移植能力

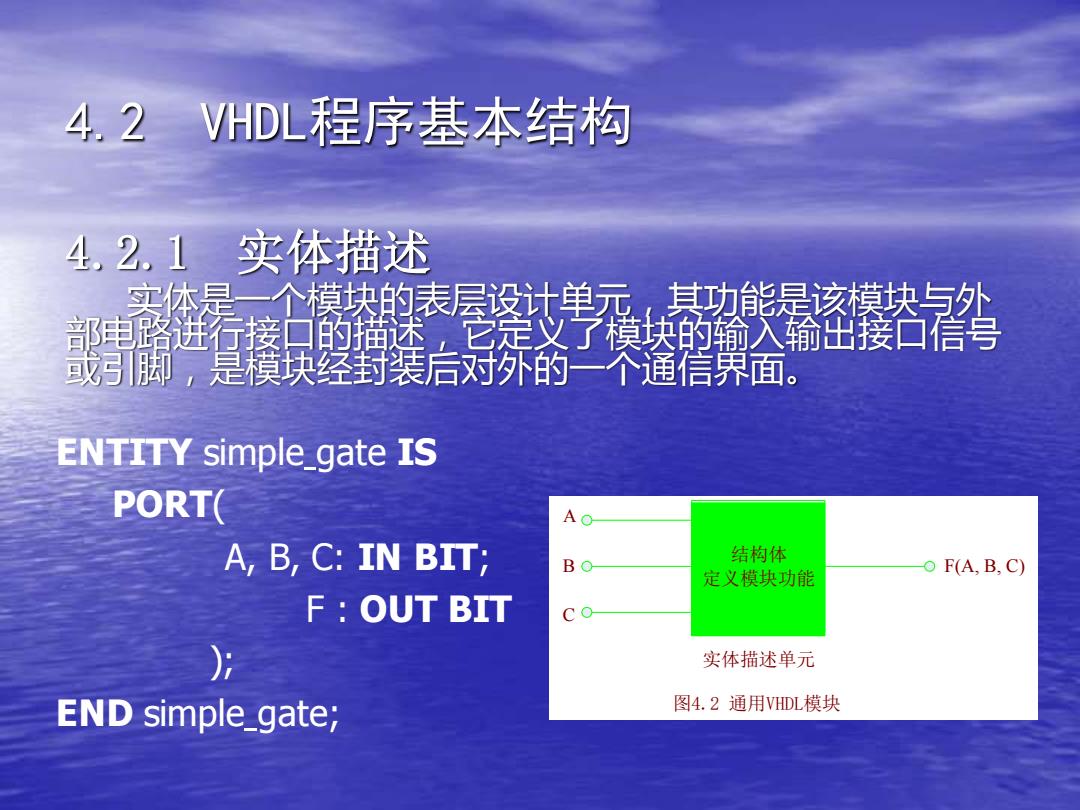

4.2 DL程序基本结构 4,2.1实体描述 实烋是一个模块的表层设计单元,其功能是该模块与外 部电进石接口的塍一 它差义了模块的输人输世接合信号 或,是模块经封裹后对你的一个通信面。 ENTITY simple_gate IS PORT( AO A,B,C:IN BIT; 结构体 定义模块功能 F(A,B,C) F:OUT BIT ) 实体描述单元 END simple_gate; 图4.2通用VHDL模块

4.2 VHDL程序基本结构 4.2.1 实体描述 实体是一个模块的表层设计单元,其功能是该模块与外 部电路进行接口的描述,它定义了模块的输入输出接口信号 或引脚,是模块经封装后对外的一个通信界面。 ENTITY simple gate IS PORT( A, B, C: IN BIT; F : OUT BIT ); END simple gate; 结构体 定义模块功能 图4.2 通用VHDL模块 A B C 实体描述单元 F(A, B, C)

4.2.1 实体描述(续) 端口声明的语句格式是: 标识符:端口模式数据类型; VDL可综合的端口模式有以下四种: ·N”通道为单向只读模式,规定数据只能通过此端口被 读入实体中。 ·“OUT”通道为单向输出模式,规定数据只能通过此端口 从实体向外流出,或者说可以将实体中的数据向此端口赋值 ·INOUT”定义的通道确定为输入输出双向端口,即从端 ▣的内部看,可以对此端口进行赋值,也可以通过此端口读 入外部的数据;而从端口的外部看,信号既可以从此端口流 出,也可以向此端口输入信号,如RAM的数据端口。 ·“BUFFER”功能与NOUT类似,区别在于当需要输入数 据时,只允许内部回读输出的信号,即允许反馈

4.2.1 实体描述(续) 端口声明的语句格式是: 标识符:端口模式 数据类型; VHDL可综合的端口模式有以下四种: •“IN”通道为单向只读模式,规定数据只能通过此端口被 读入实体中。 •“OUT”通道为单向输出模式,规定数据只能通过此端口 从实体向外流出,或者说可以将实体中的数据向此端口赋值 。 •“INOUT” 定义的通道确定为输入输出双向端口,即从端 口的内部看,可以对此端口进行赋值,也可以通过此端口读 入外部的数据;而从端口的外部看,信号既可以从此端口流 出,也可以向此端口输入信号,如RAM的数据端口。 •“BUFFER” 功能与INOUT类似,区别在于当需要输入数 据时,只允许内部回读输出的信号,即允许反馈

4.2.2 结构体描述 定义好模块的实体以后,就可以用结构体声明描述模块 具体做什么,实现怎样的逻辑功能。最典型的结构体描述方 式有以下三种: •行为描述:不考虑硬件实现的途径,直接建立输入与输出 之间的关系。 ·结构描述:通过组合如基本逻辑门电路等更初级的部件构 造实现逻辑功能。 ·数据流描述:通过定义模块中信号的流动方向描述模块功 能,也可以看作一种特殊的行为描述模式

4.2.2 结构体描述 定义好模块的实体以后,就可以用结构体声明描述模块 具体做什么,实现怎样的逻辑功能。最典型的结构体描述方 式有以下三种: •行为描述:不考虑硬件实现的途径,直接建立输入与输出 之间的关系。 •结构描述:通过组合如基本逻辑门电路等更初级的部件构 造实现逻辑功能。 •数据流描述:通过定义模块中信号的流动方向描述模块功 能,也可以看作一种特殊的行为描述模式

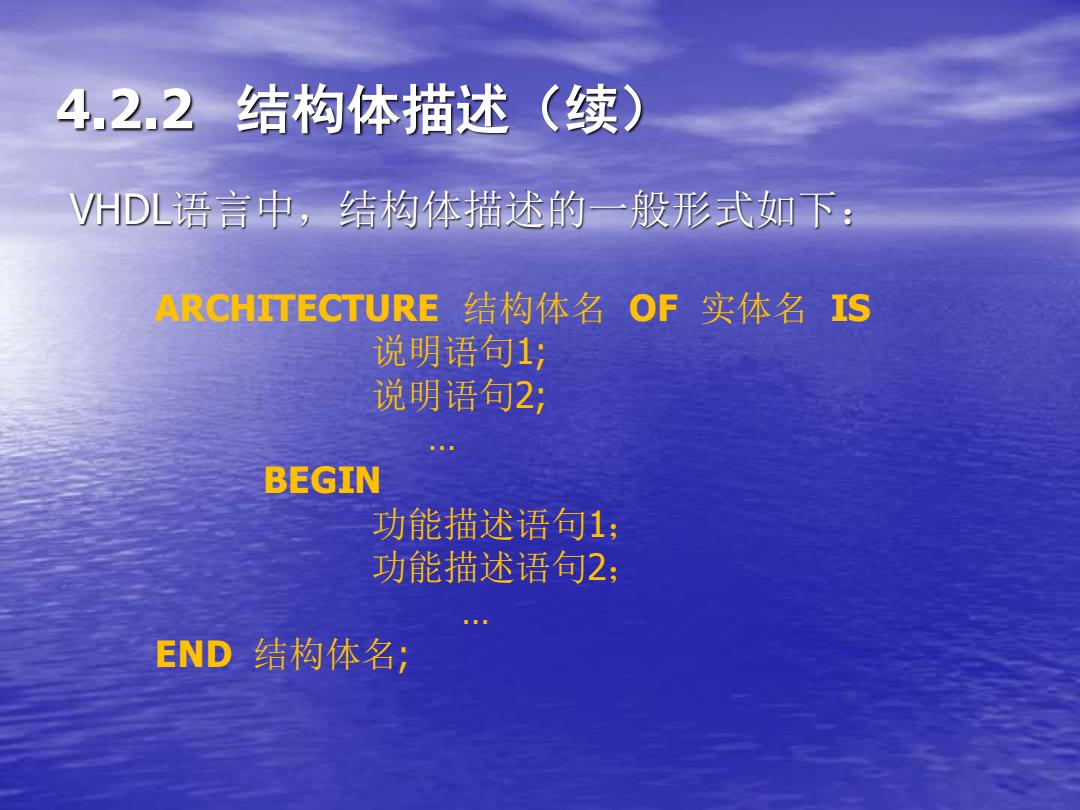

4.2.2结构体描述(续) V付DL语言中,结构体描述的一般形式如下: ARCHITECTURE结构体名OF实体名IS 说明语句1; 说明语句2; BEGIN 功能描述语句1; 功能描述语句2: END结构体名;

4.2.2 结构体描述(续) VHDL语言中,结构体描述的一般形式如下: ARCHITECTURE 结构体名 OF 实体名 IS 说明语句1; 说明语句2; … BEGIN 功能描述语句1; 功能描述语句2; … END 结构体名;

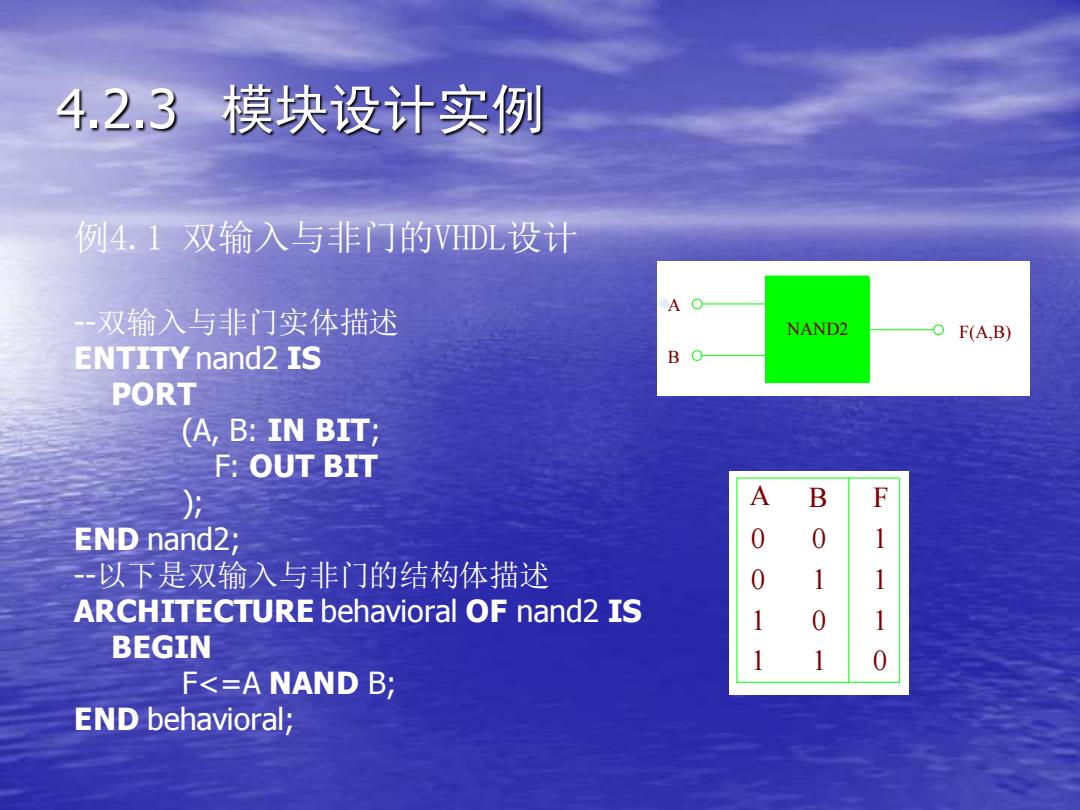

4.2.3 模块设计实例 例4.1双输入与非门的VDL设计 AO 一双输入与非门实体描述 NAND2 F(A,B) ENTITY nand2 IS PORT (A,B:IN BIT; F:OUT BIT ) A B F END nand2; 0 -以下是双输入与非门的结构体描述 ARCHITECTURE behavioral OF nand2 IS 0 BEGIN 0 F<=A NAND B; END behavioral;

4.2.3 模块设计实例 --双输入与非门实体描述 ENTITY nand2 IS PORT (A, B: IN BIT; F: OUT BIT ); END nand2; --以下是双输入与非门的结构体描述 ARCHITECTURE behavioral OF nand2 IS BEGIN F<=A NAND B; END behavioral; 例4.1 双输入与非门的VHDL设计 图4.3 双输入与非门模块 A B NAND2 F(A,B) 0 1 A B F 0 0 1 0 1 1 1 0 1 1 图4.3 双输入与非门模块 A B NAND2 F(A,B) 0 1 A B F 0 0 1 0 1 1 1 0 1 1

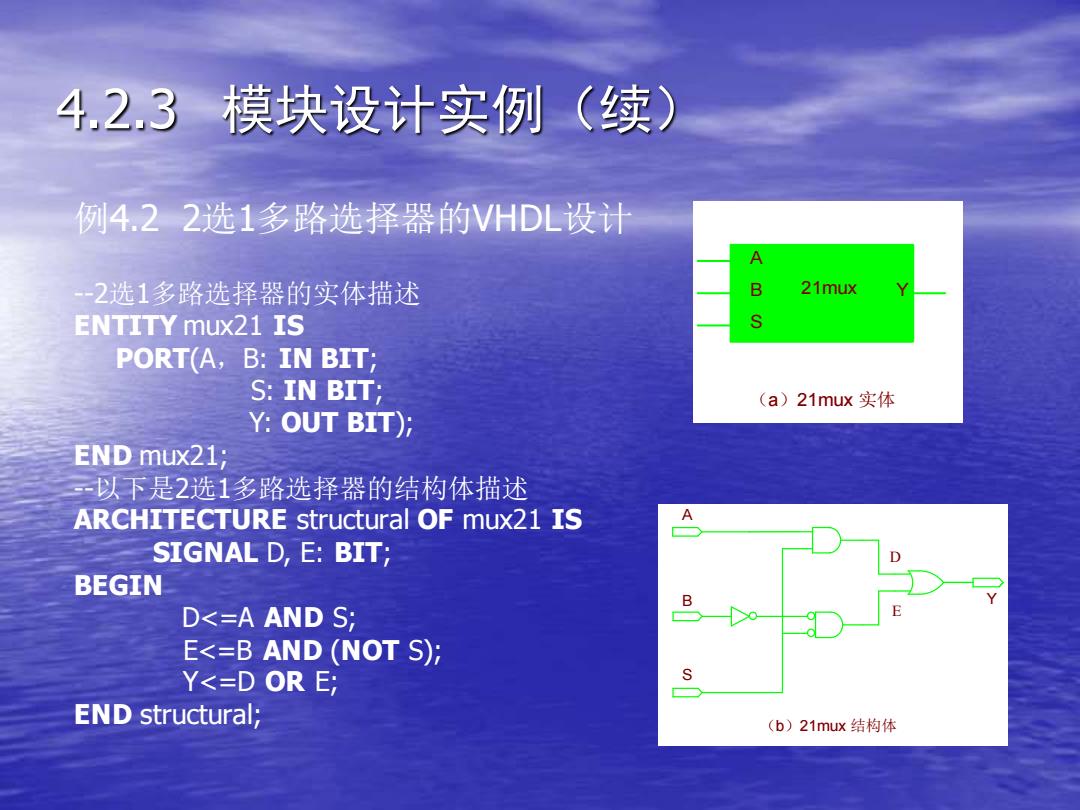

4.2.3 模块设计实例(续) 例4.22选1多路选择器的VHDL设计 A -2选1多路选择器的实体描述 21mux ENTITY mux21 IS PORT(A,B:IN BIT; S:IN BIT; (a)21mux实体 Y:OUT BIT); END mux21; -以下是2选1多路选择器的结构体描述 ARCHITECTURE structural OF mux21 IS A SIGNAL D,E:BIT; BEGIN D<=A AND S; E<=B AND(NOT S); Y<=D OR E; END structural; (b)21mux结构体

4.2.3 模块设计实例(续) --2选1多路选择器的实体描述 ENTITY mux21 IS PORT(A,B: IN BIT; S: IN BIT; Y: OUT BIT); END mux21; --以下是2选1多路选择器的结构体描述 ARCHITECTURE structural OF mux21 IS SIGNAL D, E: BIT; BEGIN D<=A AND S; E<=B AND (NOT S); Y<=D OR E; END structural; 例4.2 2选1多路选择器的VHDL设计 图4.4 2选1多路选择器 A B S Y S B A 21mux Y (a)21mux 实体 (b)21mux 结构体 D E 图4.4 2选1多路选择器 A B S Y S B A 21mux Y (a)21mux 实体 (b)21mux 结构体 D E