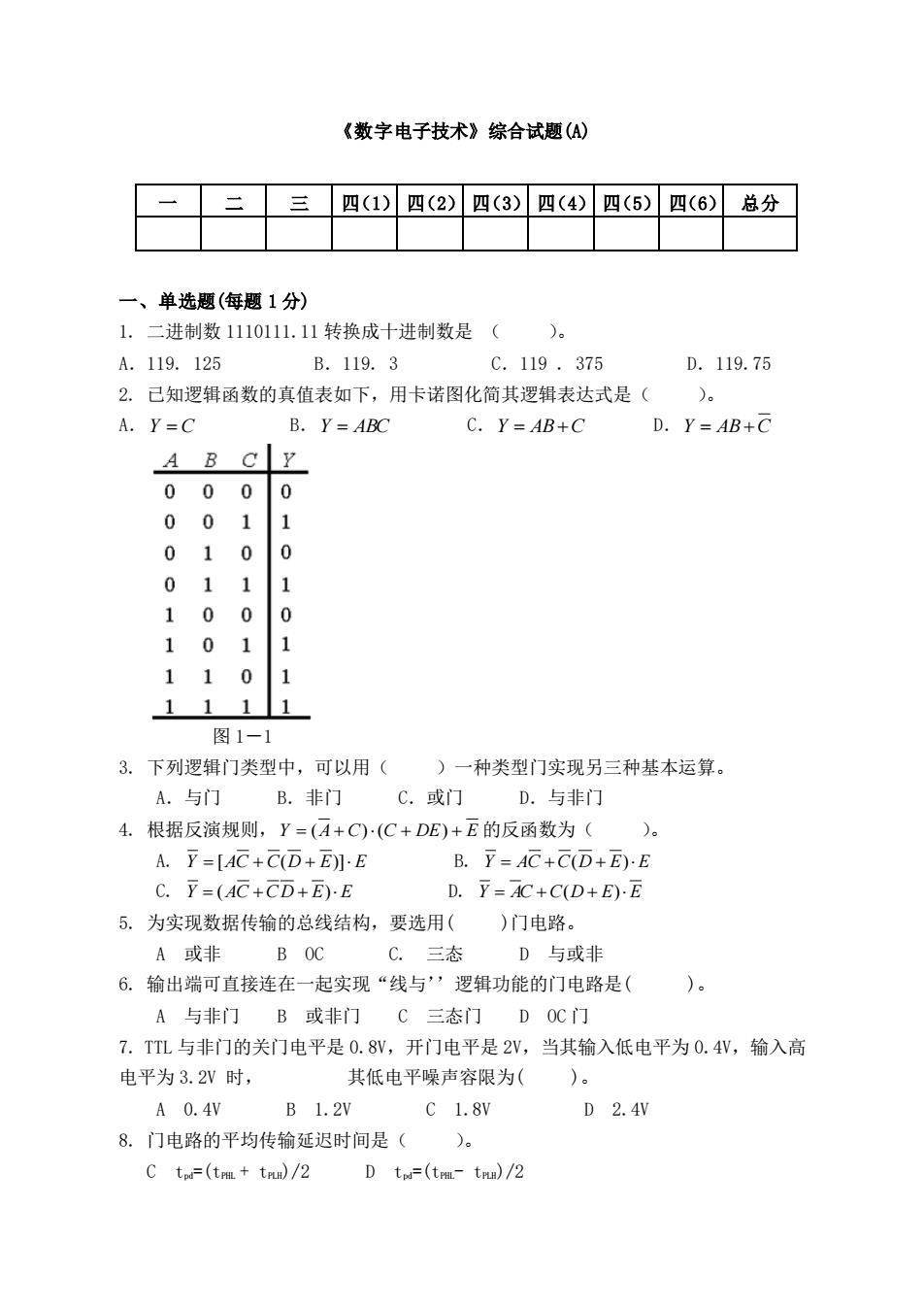

《数字电子技术》综合试题() 一 三四(1)四(2)四(3)四(4)四(5)四(6)总分 一、单选题(每题1分) 1.二进制数1110111.11转换成十进制数是( A.119.125 B.119.3 C.119.375 D.119.75 2.已知逻辑函数的真值表如下,用卡诺图化简其逻辑表达式是( A.Y=C B.Y=ARC C.Y=AB+C D.Y=AB+C A B CY 0000 001 1 010 0 1 1 00 0 101 110 1 1111 图1一1 3.下列逻辑门类型中,可以用( )一种类型门实现另三种基本运算。 A.与门 B.非门 C.或门 D.与非门 4.根据反演规则,Y=(A+C)(C+DE)+E的反函数为( A.Y=[4C+C(D+E)].E B.Y=AC+C(D+E).E C.Y=(AC+CD+E).E D.Y=AC+C(D+E)E 5.为实现数据传输的总线结构,要选用()门电路。 A或非 B OC C.三态 D与或非 6。输出端可直接连在一起实现“线与”逻辑功能的门电路是( A与非门B或非门C三态门DOC门 7.TTL与非门的关门电平是0.8V,开门电平是2V,当其输入低电平为0.4Y,输入高 电平为3.2V时, 其低电平噪声容限为( )。 A0.4Y B1.2V C1.8v D2.4W 8.门电路的平均传输延迟时间是( )。 c tp=(tm.+tnu)/2 Dt(tm-tn)/2

《数字电子技术》综合试题(A) 一、单选题(每题 1 分) 1. 二进制数 1110111.11 转换成十进制数是 ( )。 A.119. 125 B.119. 3 C.119 . 375 D.119.75 2. 已知逻辑函数的真值表如下,用卡诺图化简其逻辑表达式是( )。 A.Y = C B.Y = ABC C.Y = AB+C D.Y = AB +C 图 1-1 3. 下列逻辑门类型中,可以用( )一种类型门实现另三种基本运算。 A.与门 B.非门 C.或门 D.与非门 4. 根据反演规则, Y = (A + C)(C + DE) + E 的反函数为( )。 A. Y = [AC + C(D + E)] E B. Y = AC +C(D + E) E C. Y = (AC +CD + E) E D. Y = AC +C(D + E)E 5. 为实现数据传输的总线结构,要选用( )门电路。 A 或非 B OC C. 三态 D 与或非 6. 输出端可直接连在一起实现“线与’’逻辑功能的门电路是( )。 A 与非门 B 或非门 C 三态门 D OC 门 7. TTL 与非门的关门电平是 0.8V,开门电平是 2V,当其输入低电平为 0.4V,输入高 电平为 3.2V 时, 其低电平噪声容限为( )。 A 0.4V B 1.2V C 1.8V D 2.4V 8. 门电路的平均传输延迟时间是( )。 C tpd=(tPHL + tPLH)/2 D tpd=(tPHL- tPLH)/2 一 二 三 四(1) 四(2) 四(3) 四(4) 四(5) 四(6) 总分

9.维持一阻塞D触发器是( )。 A下降沿触发 B上升沿触发 C高电平触发 D低电平触发 10.能把缓慢变化的输入信号转换成矩形波的电路是( A单稳态触发器: B多谐振荡器: C施密特触发器: D边沿触发器 二、判断题(每题1分) 1.格雷码具有任意两组相邻代码之间只有一位不同的特性。 2.逻辑函数表达式的化简结果是唯一的。( 3.逻辑函数的化简是为了使表达式简化而与硬件电路无关。 4.单稳态触发器不需要外加触发信号,就可产生脉冲信号, 5.用施密特触发器可以构成多谐振荡器。( 6.CM0S门电路的多余输入端浮空时,在逻辑上等效于输入高电平。( 7.555定时器外接少量阻容元件便可构成施密特触发器、单稳态触发器和多谐振荡器。 8。竞争冒险现象是可以消除的。 9.半加器与全加器的主要区别:是否考虑来自低位的进位: 10.没有专门的数据分配器,一般是用译码器改接的。 三、填空题(每题2分) 1.数字电路根据半导体的导电类型不同,可分为( )电路和( )电路。 2.常用的BCD码有( )码、( )码、( )码、( )码等。常 用的可靠性代码有( )码、( )码。 3.逻辑代数又称为( )代数。最基本的逻辑运算有( )、( )、( 三种。常用的导出逻辑运算为( )、( )、( )、( )、( 4.逻辑函数的常用表示方法有( )入( )、( )、( 其中( )和( )具有唯一性。 5.在TTL门电路中,输入端悬空在逻辑上等效于输入()电平。 6.标准TTL门输出高电平典型值是()伏,低电平典型值是()伏。 7.TTL、CMOS电路的抗干扰能力是( )强于( 8.把JK触发器转换为T'触发器的方法是( 9.由与非门构成的基本RS触发器的输入端是Rd和Sd,其约束条件是

9. 维持一阻塞 D 触发器是( )。 A 下降沿触发 B 上升沿触发 C 高电平触发 D 低电平触发 10. 能把缓慢变化的输入信号转换成矩形波的电路是 ( )。 A 单稳态触发器; B 多谐振荡器; C 施密特触发器; D 边沿触发器 二、判断题(每题 1 分) 1. 格雷码具有任意两组相邻代码之间只有一位不同的特性。 ( ) 2. 逻辑函数表达式的化简结果是唯一的。( ) 3. 逻辑函数的化简是为了使表达式简化而与硬件电路无关。 ( ) 4. 单稳态触发器不需要外加触发信号,就可产生脉冲信号。 ( ) 5. 用施密特触发器可以构成多谐振荡器。( ) 6. CMOS 门电路的多余输入端浮空时,在逻辑上等效于输入高电平。( ) 7. 555 定时器外接少量阻容元件便可构成施密特触发器、单稳态触发器和多谐振荡器。 ( ) 8. 竞争冒险现象是可以消除的。 ( ) 9. 半加器与全加器的主要区别:是否考虑来自低位的进位。 ( ) 10. 没有专门的数据分配器,一般是用译码器改接的。 ( ) 三、填空题(每题 2 分) 1. 数字电路根据半导体的导电类型不同,可分为 ( )电路和( )电路。 2. 常用的 BCD 码有( )码、( )码、( )码、( )码等。常 用的可靠性代码有( )码、( )码。 3. 逻辑代数又称为 ( )代数。最基本的逻辑运算有( )、( )、( ) 三种。常用的导出逻辑运算为 ( )、( )、( )、( )、( ) 。 4. 逻辑函数的常用表示方法有( )、( )、( )、( ); 其中( )和( )具有唯一性。 5. 在 TTL 门电路中,输入端悬空在逻辑上等效于输入 ( ) 电平。 6. 标准 TTL 门输出高电平典型值是 ( ) 伏,低电平典型值是 ( ) 伏。 7. TTL、CMOS 电路的抗干扰能力是 ( ) 强于 ( ) 。 8. 把 JK 触发器转换为 T’触发器的方法是( )。 9. 由与 非门构 成的 基本 RS 触发 器的 输入端 是 Rd 和 Sd ,其 约束条 件是 ( )

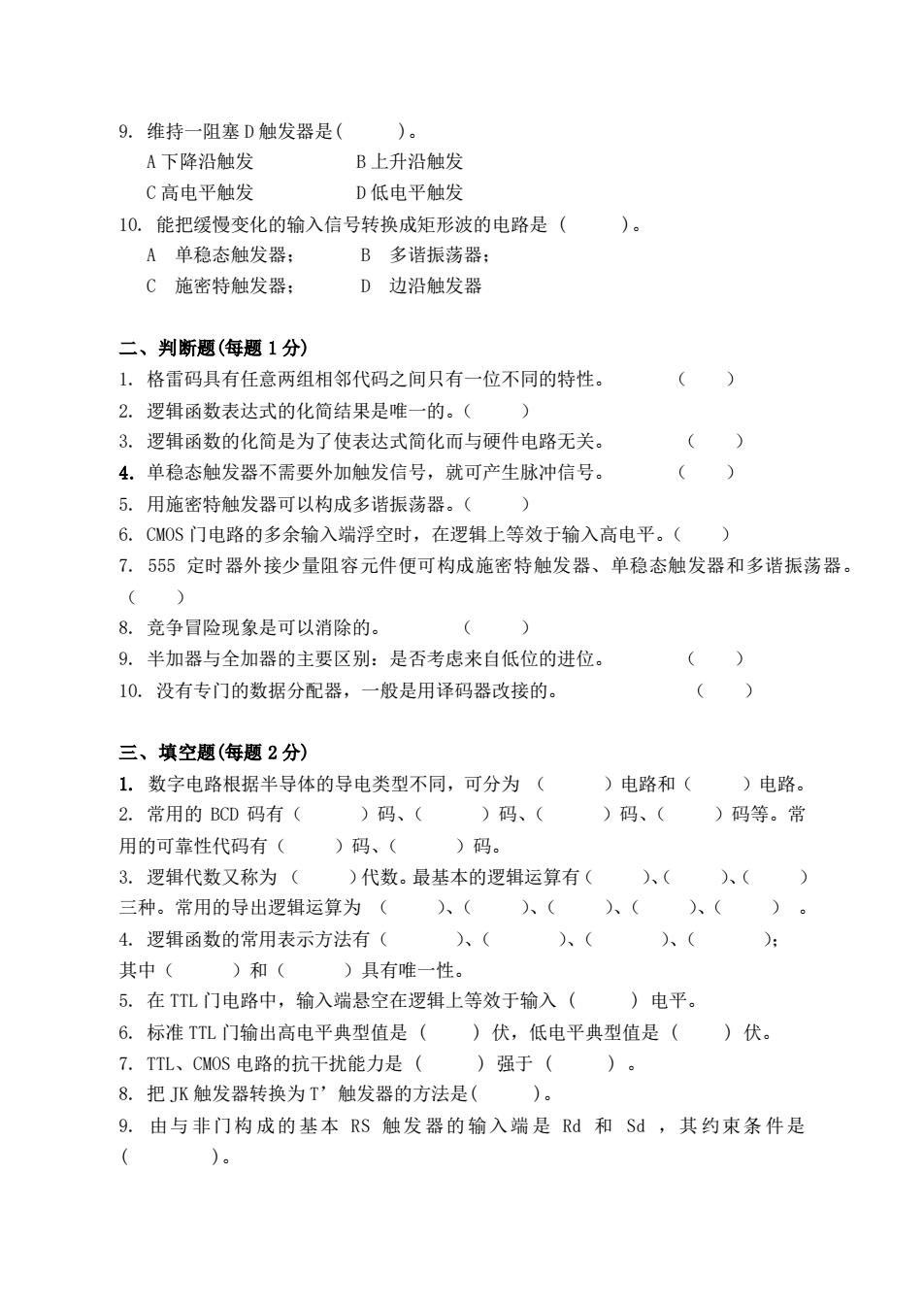

10.施密特触发器有()个稳定状态,多谐振荡器有()个稳定状态。 四、计算分析题(每题10分) 1.已知电路如图4-1示,要求: 1)说明它是什么电路:试画出uc和uo的波形。 2)若增大电阻R2,或增加电容C容量,对输出信号频率有何影响? +Ucc R148 uc 0 R20 DIS 3 -IHGHD 0

10. 施密特触发器有( )个稳定状态,多谐振荡器有( )个稳定状态。 四、计算分析题(每题 10 分) 1. 已知电路如图 4-1 示,要求: 1) 说明它是什么电路;试画出 uc 和 uo 的波形。 2) 若增大电阻 R2,或增加电容 C 容量,对输出信号频率有何影响?

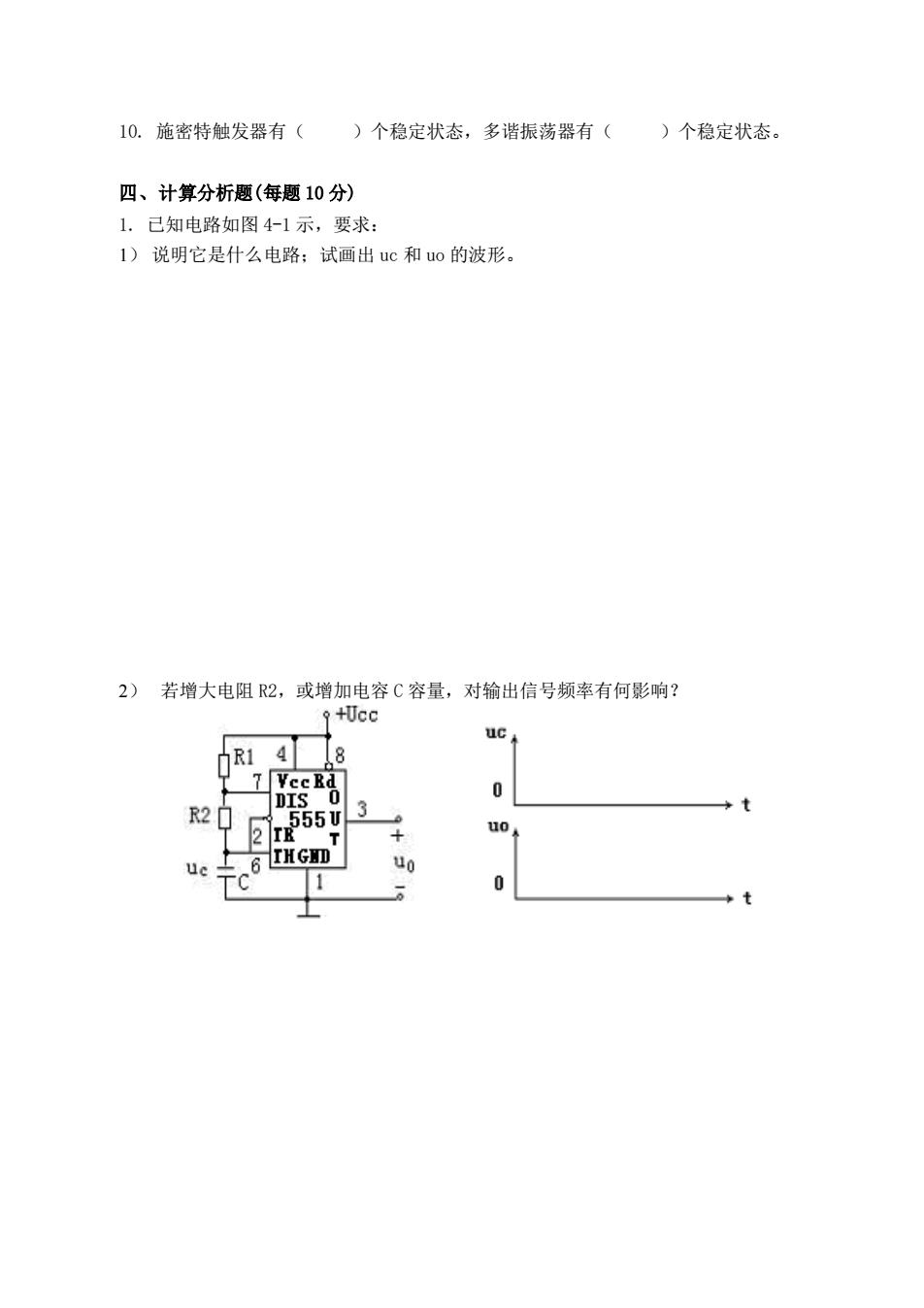

2.在一个射击游戏中,射手可打三枪,一枪打鸟,一枪打鸡,一枪打兔子,规则是命中 不少于两枪者获奖。 试用与非门设计一个判别得奖电路。写出真值表、逻辑函数并用卡诺图化简、逻辑电 路。 3.1)试用译码器CT74LS138实现下列逻辑函数Y=ABC+ABC+ABC。 TO TI T2 T3 Y4T5 TGT7 ]STa CT74LS138 STe A0 A1 A2 图4-3.1

2. 在一个射击游戏中,射手可打三枪,一枪打鸟,一枪打鸡,一枪打兔子,规则是命中 不少于两枪者获奖。 试用与非门设计一个判别得奖电路。写出真值表、逻辑函数并用卡诺图化简、逻辑电 路。 3. 1)试用译码器 CT74LS138 实现下列逻辑函数 Y = ABC + ABC + ABC 。 图 4-3.1

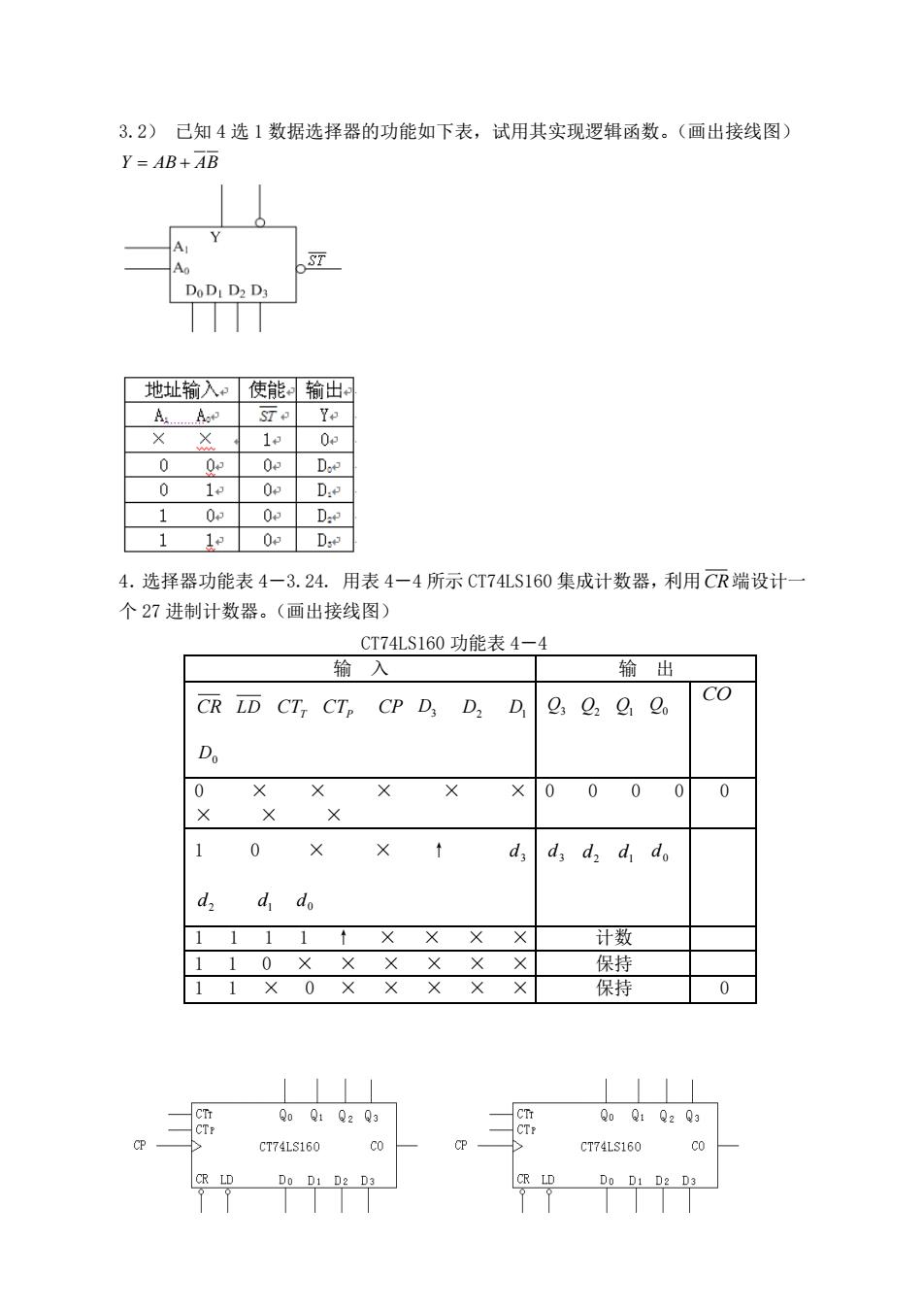

3.2)己知4选1数据选择器的功能如下表,试用其实现逻辑函数。(画出接线图) Y=AB+AB DoD:D2 D 地址输入p使能输出 100 00 0 D:e 01303D.3 00D 1 1o 0 D.o 4.选择器功能表4-3.24.用表4-4所示CT74LS160集成计数器,利用CR端设计一 个27进制计数器。(画出接线图) CT74LS160功能表4-4 输入 输出 CR LD CT CT, CP D D:D.e 2:e 0 ×0000 0 0 + d,d,dd do d. d do 1111↑XXXX 计新 保持 保持 C774LS160C0 T74L160

3.2) 已知 4 选 1 数据选择器的功能如下表,试用其实现逻辑函数。(画出接线图) Y AB AB = + 4.选择器功能表 4-3.24. 用表 4-4 所示 CT74LS160 集成计数器,利用 CR 端设计一 个 27 进制计数器。(画出接线图) CT74LS160 功能表 4-4 输 入 输 出 CR LD CTT CTP CP D3 D2 D1 D0 Q3 Q2 Q1 Q0 CO 0 × × × × × × × × 0000 0 1 0 × × ↑ 3 d 2 d 1 d 0 d 3 d 2 d 1 d 0 d 1111 ↑×××× 计数 110 ×××××× 保持 1 1 × 0 ××××× 保持 0 ST

5.分析如图4-5电路,说明此扭环计数器是几分频电路。 Q0Q1Q2 Q29 74LS194 74LS194 Do D:D2 D 平 图4-5 附CT74LS194功能表4-5 输 入 输出 CRM1M。CP Ds Dsg D。D,DD 2.9g22 0× ×××××000 0 0 保持 do d do d dz d. X 1 e2. 0。 g 0 0 + 1 0 0 0 0 保持

5. 分析如图 4-5 电路,说明此扭环计数器是几分频电路。 图 4-5 附 CT74LS194 功能表 4-5 输 入 输 出 CR M1 M0 CP DSL DSR D0 D1 D2 D3 Q0 Q1 Q2 Q3 0 ××××××××× 0000 1 × × 0 ×××××× 保 持 1 1 1 ↑ × × 0 d d1 d2 3 d 0 d d1 d2 3 d 1 0 1 ↑ × 1 × × × × 1 Q0 Q1 Q2 1 0 1 ↑ × 0 × × × × 0 Q0 Q1 Q2 1 1 0 ↑ 1 × × × × × Q1 Q2 Q3 1 1 1 0 ↑ 0 × × × × × Q1 Q2 Q3 0 1 0 0 × × × × × × × 保 持

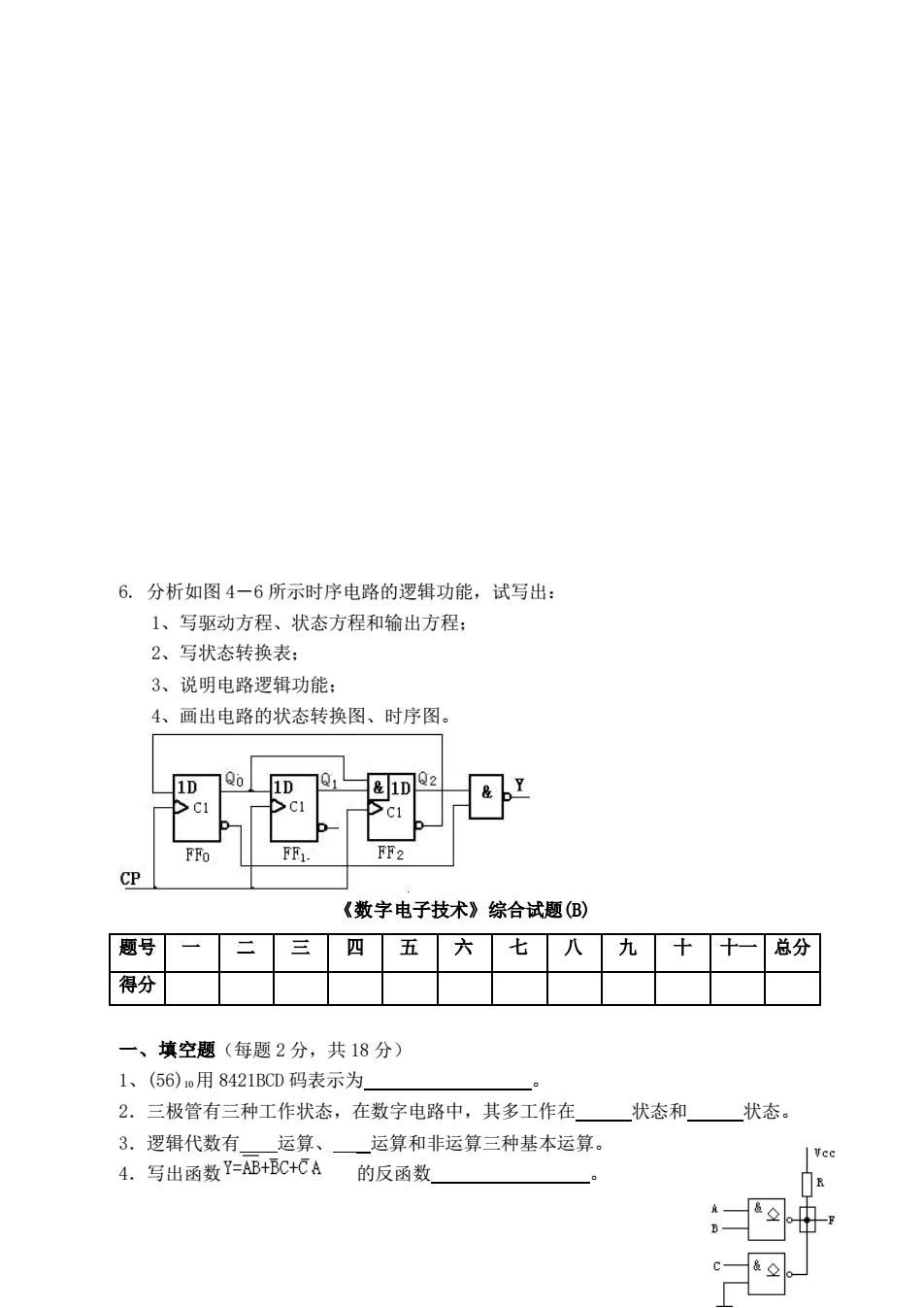

6.分析如图4一6所示时序电路的逻辑功能,试写出: 1、写驱动方程、状态方程和输出方程: 2、写状态转换表: 3、说明电路逻辑功能: 4、画出电路的状态转换图、时序图 D CP 《数字电子技术》综合试题(®) 题号一 三四五六七八九十十一总分 得分 一、填空题(每题2分,共18分》 1、(56)用8421BCD码表示为 2.三极管有三种工作状态,在数字电路中,其多工作在状态和状态。 3.罗组代数有 运算、」 运算和非运算三种基本运算。 4.写出函数=AB+BC+CA 的反函数 c&父

6. 分析如图 4-6 所示时序电路的逻辑功能,试写出: 1、写驱动方程、状态方程和输出方程; 2、写状态转换表; 3、说明电路逻辑功能; 4、画出电路的状态转换图、时序图。 《数字电子技术》综合试题(B) 一、填空题(每题 2 分,共 18 分) 1、(56)10用 8421BCD 码表示为 。 2.三极管有三种工作状态,在数字电路中,其多工作在 状态和 状态。 3.逻辑代数有 运算、 运算和非运算三种基本运算。 4.写出函数 的反函数 。 题号 一 二 三 四 五 六 七 八 九 十 十一 总分 得分

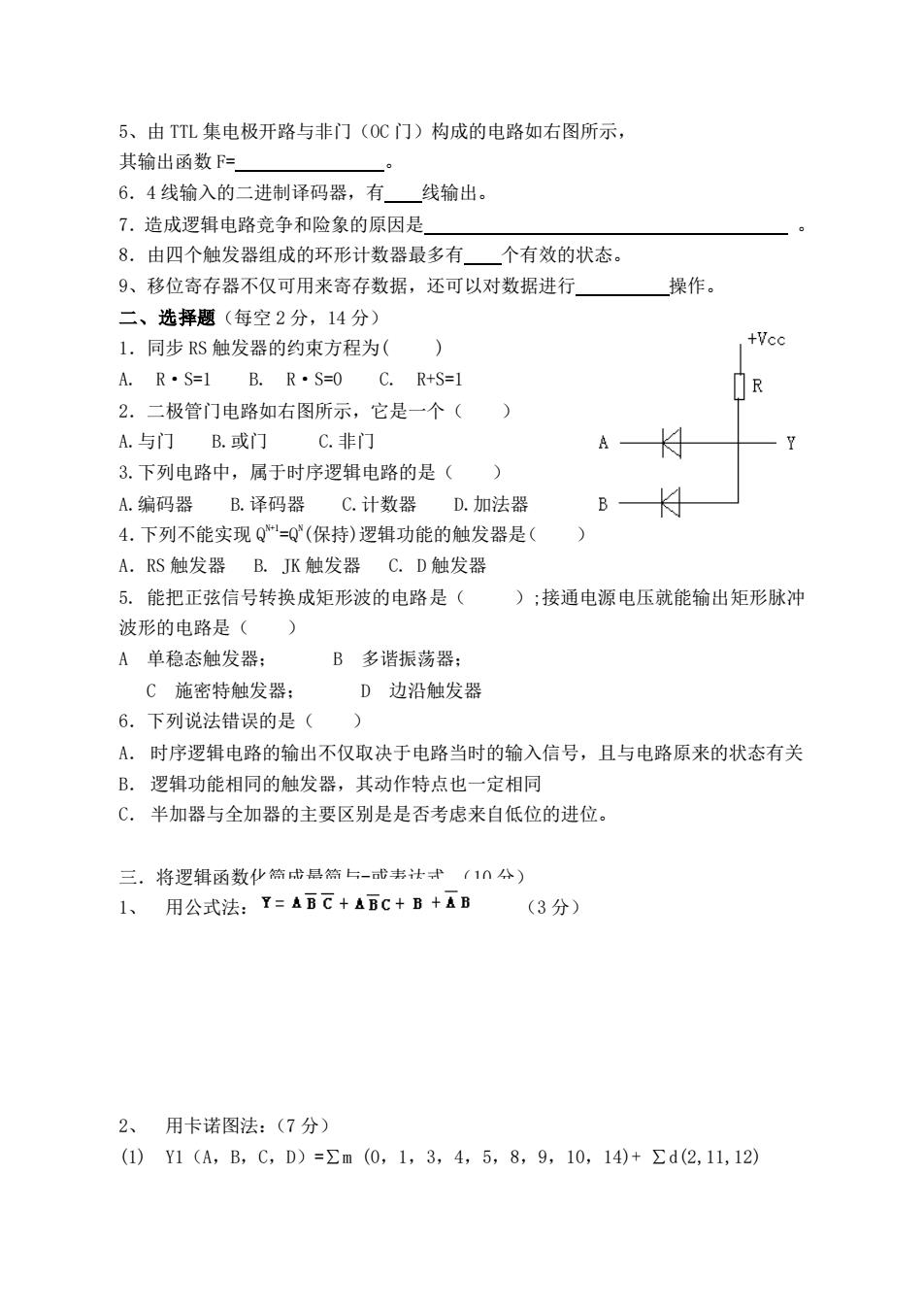

5、由TTL集电极开路与非门(0C门)构成的电路如右图所示, 其输出函数下= 6.4线输入的二进制译码器,有_线输出 7.造成逻辑电路竞争和险象的原因是 8.由四个触发器组成的环形计数器最多有个有效的状态。 9、移位寄存器不仅可用来寄存数据,还可以对数据进行】 操作。 二、选择题(每空2分,14分) 1.同步S触发器的约束方程为( +Vcc A.R·S=1B.R·S=0C.R+S=1 R 2.二极管门电路如右图所示,它是一个( A.与门B.或门 C.非门 3.下列电路中,属于时序逻辑电路的是() A.编码器B.译码器C.计数器D.加法器 4.下列不能实现Q-Q(保持)逻辑功能的触发器是( A.RS触发器B.JK触发器C.D触发器 5.能把正弦信号转换成矩形波的电路是( ):接通电源电压就能输出矩形脉冲 波形的电路是( A单稳态触发器: B多谐振荡器: C施密特触发器: D边沿触发器 6,下列说法错误的是( A.时序逻辑电路的输出不仅取决于电路当时的输入信号,且与电路原来的状态有关 B.逻辑功能相同的触发器,其动作特点也一定相同 C.半加器与全加器的主要区别是是否考虑来自低位的进位 三.将逻辑函数化筒成品篇上-成岁汝术11n公) 1、用公式法:T=aEC+A万C+B+AB (3分) 2、用卡诺图法:(7分) (1)Y1(A,B,C,D)=∑m(0,1,3,4,5,8,9,10,14)+∑d(2,11,12)

5、由 TTL 集电极开路与非门(OC 门)构成的电路如右图所示, 其输出函数 F= 。 6.4 线输入的二进制译码器,有 线输出。 7.造成逻辑电路竞争和险象的原因是 。 8.由四个触发器组成的环形计数器最多有 个有效的状态。 9、移位寄存器不仅可用来寄存数据,还可以对数据进行 操作。 二、选择题(每空 2 分,14 分) 1.同步 RS 触发器的约束方程为( ) A. R·S=1 B. R·S=0 C. R+S=1 2.二极管门电路如右图所示,它是一个( ) A.与门 B.或门 C.非门 3.下列电路中,属于时序逻辑电路的是( ) A.编码器 B.译码器 C.计数器 D.加法器 4.下列不能实现 Q N+1=QN (保持)逻辑功能的触发器是( ) A.RS 触发器 B. JK 触发器 C. D 触发器 5. 能把正弦信号转换成矩形波的电路是( );接通电源电压就能输出矩形脉冲 波形的电路是( ) A 单稳态触发器; B 多谐振荡器; C 施密特触发器; D 边沿触发器 6.下列说法错误的是( ) A. 时序逻辑电路的输出不仅取决于电路当时的输入信号,且与电路原来的状态有关 B. 逻辑功能相同的触发器,其动作特点也一定相同 C. 半加器与全加器的主要区别是是否考虑来自低位的进位。 三.将逻辑函数化简成最简与-或表达式。(10 分) 1、 用公式法: (3 分) 2、 用卡诺图法:(7 分) (1) Y1(A,B,C,D)=∑m (0,1,3,4,5,8,9,10,14)+ ∑d(2,11,12)

(②)Y2=aB+AC+BC 三画出图中各门电路输出端的电压波形.输入端A、B电压波形如图所示:(4 分) 'in. B1 丹”回 11 +t 四.判断下列逻辑门电路的输出状态。 注:(1)(2)为TTL门电路,(3)(4)为CM0S门电路。(8分) 10K0 5102中 1x (1) (2) (3) (4)

(2) 三. 画出图中各门电路输出端的电压波形.输入端 A、B 电压波形如图所示: (4 分) 四. 判断下列逻辑门电路的输出状态。 注:(1)(2)为 TTL 门电路,(3)(4)为 CMOS 门电路。(8 分)

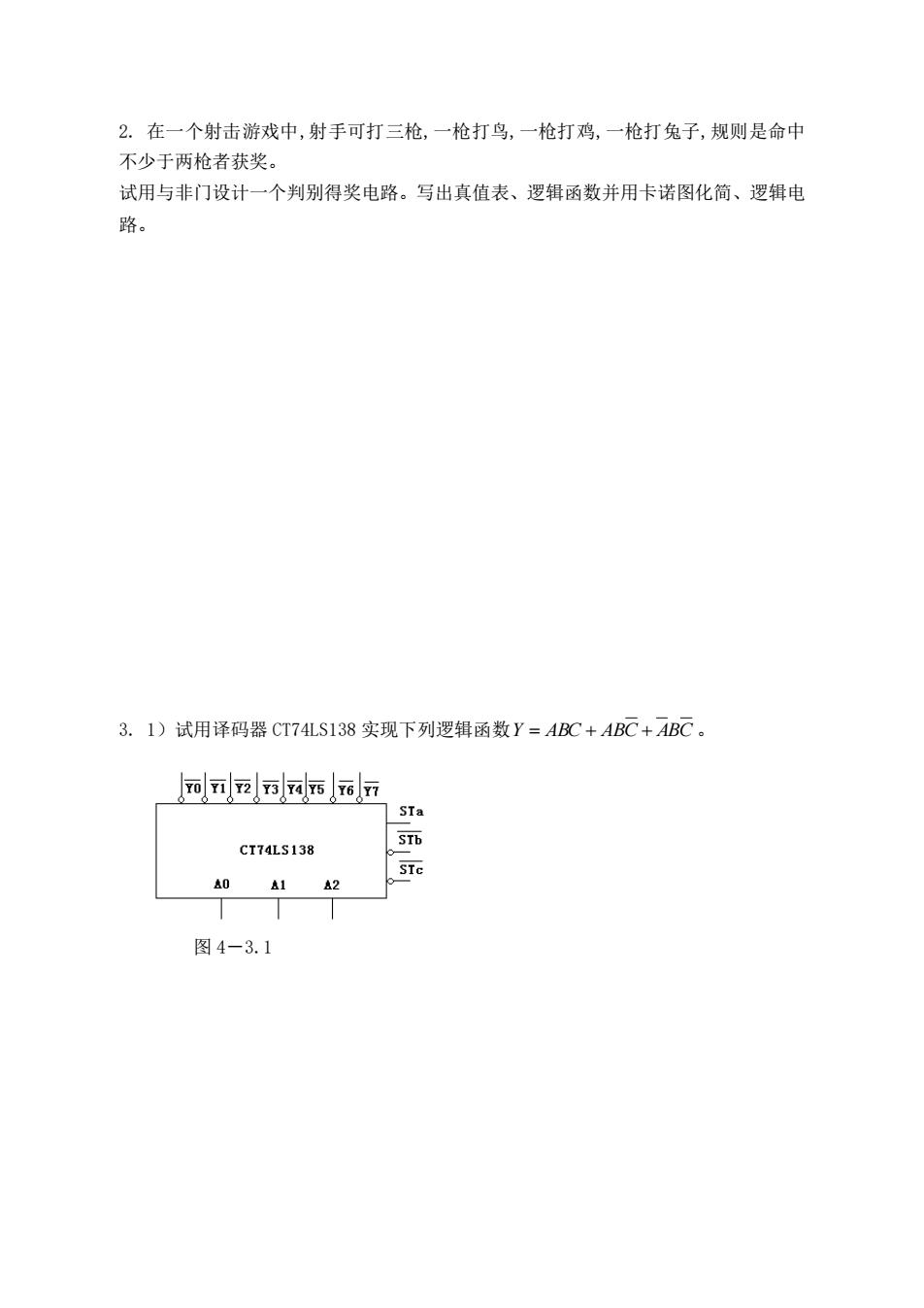

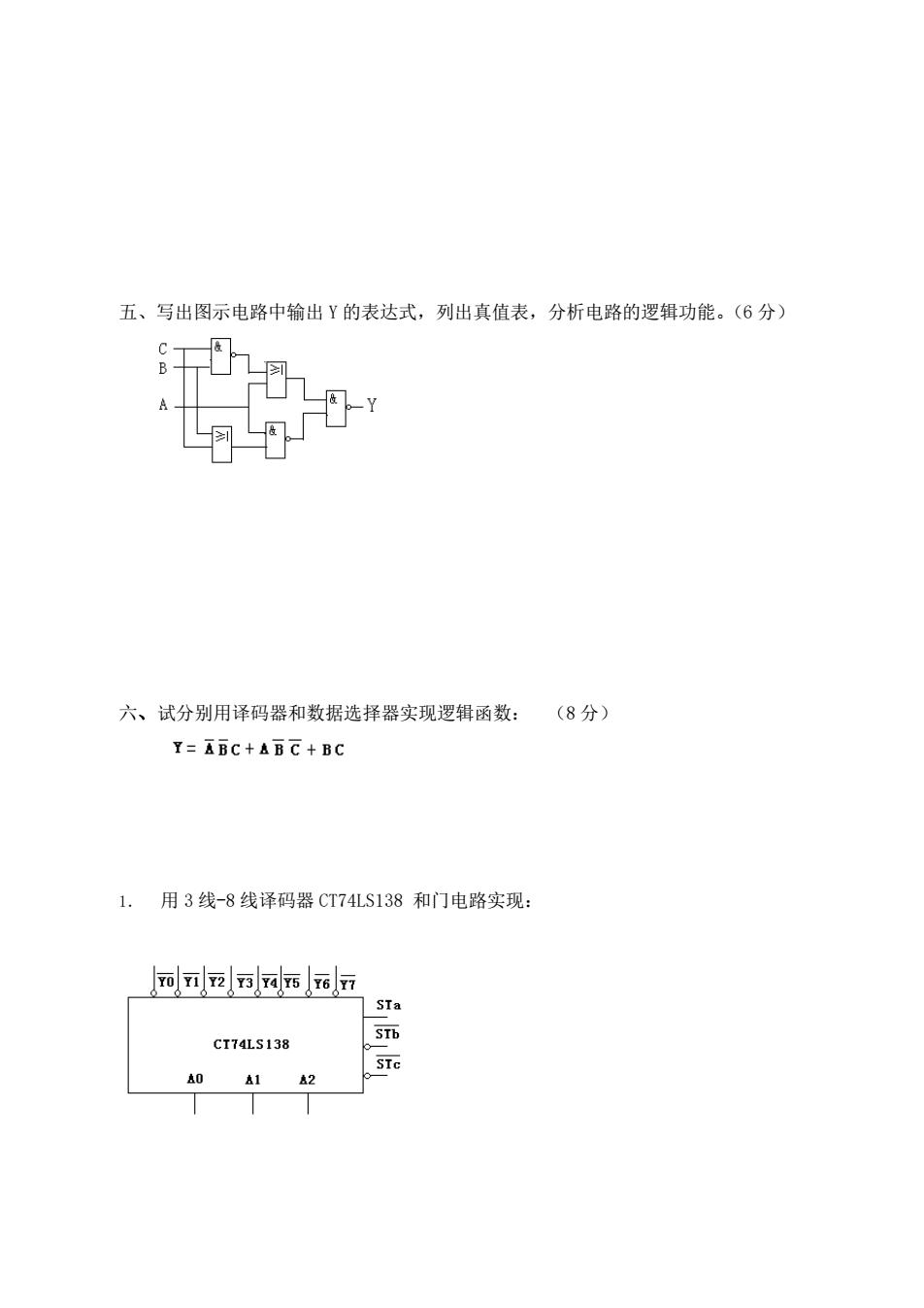

五、写出图示电路中输出Y的表达式,列出真值表,分析电路的逻辑功能。(6分) 六、试分别用译码器和数据选择器实现逻辑函数:(8分) Y=ABC+ABC+BC 1,用3线-8线译码器CT74LS138和门电路实现: o五2万ō6 STa CT74L5138 STb STe A0 Al A2

五、写出图示电路中输出 Y 的表达式,列出真值表,分析电路的逻辑功能。(6 分) 六、试分别用译码器和数据选择器实现逻辑函数: (8 分) 1. 用 3 线-8 线译码器 CT74LS138 和门电路实现: