第六章 时序逻辑电路

第 六 章 时序逻辑电路

主要内容 时序逻辑电路的分析方法、设计方法 ■ 时序逻辑电路的工作原理 ■常用时序逻辑电路介绍

主要内容 ◼ 时序逻辑电路的分析方法、设计方法 ◼ 时序逻辑电路的工作原理 ◼ 常用时序逻辑电路介绍

教学要求 重点掌握:时序逻辑电路的分析方法、设 计方法;双向移位集成寄存器、中规模集 成计数器的功能和应用;任意进制计数器 构成及其状态图。 一般了解:常用时序逻辑部件寄存器、移 位寄存器、同步计数器、异步计数器的电 路结构

重点掌握:时序逻辑电路的分析方法、设 计方法;双向移位集成寄存器、中规模集 成计数器的功能和应用;任意进制计数器 构成及其状态图。 一般了解:常用时序逻辑部件寄存器、移 位寄存器、同步计数器、异步计数器的电 路结构。 教学要求

6.1概述 什么是时序逻辑电路? 任一时刻的输出信号不仅取决于当时 的输入信号,而且还取决于电路的原状态, 或者说还与以前的输入信号有关

6.1 概述 什么是时序逻辑电路? 任一时刻的输出信号不仅取决于当时 的输入信号,而且还取决于电路的原状态, 或者说还与以前的输入信号有关

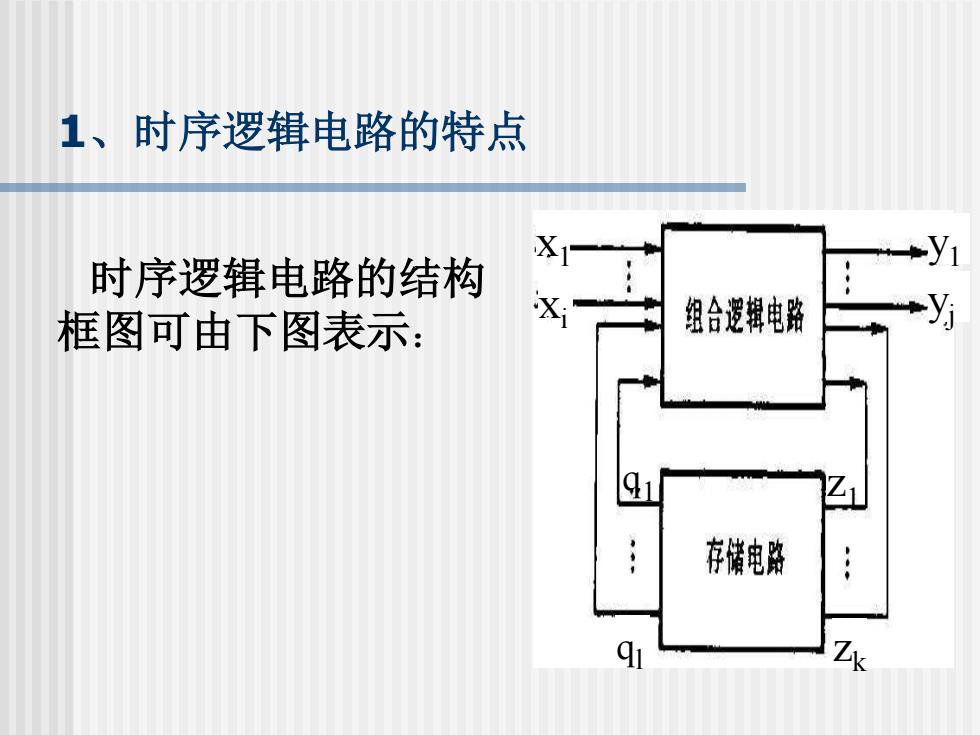

1、时序逻辑电路的特点 X 时序逻辑电路的结构 X 框图可由下图表示: 组合逻辑电路 y 91 存储电路 Zk

1、时序逻辑电路的特点 时序逻辑电路的结构 框图可由下图表示: x1 xi y1 yj z1 zk q1 ql

时序逻辑电路的两个特点: 1)包含组合电路和存储电路两个组成部 分,且存储电路是必不可少的; 2)存储电路的输出状态必须反馈到组合 电路的输入端,与输入信号一起,共同决定 电路的输出

时序逻辑电路的两个特点: 1)包含组合电路和存储电路两个组成部 分,且存储电路是必不可少的; 2)存储电路的输出状态必须反馈到组合 电路的输入端,与输入信号一起,共同决定 电路的输出

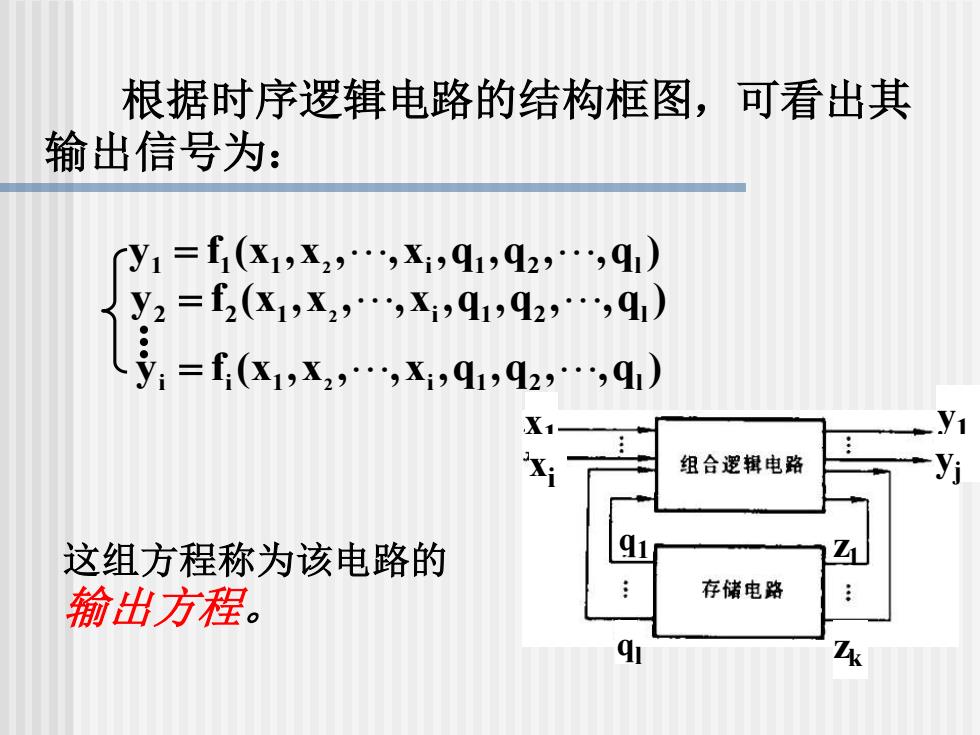

根据时序逻辑电路的结构框图,可看出其 输出信号为: ry1=f1(X1,x2,X1,91,q2,.,q1) y2=f2(X13X2,3X1q1,q23qi) 月1=f(K1,X,X,41,924) X 组合逻辑电路 这组方程称为该电路的 91 输出方程。 存储电路

根据时序逻辑电路的结构框图,可看出其 输出信号为: 这组方程称为该电路的 输出方程。 x1 xi y1 yj z1 zk q1 ql y f (x ,x , ,x ,q ,q , ,q ) 1 = 1 1 2 i 1 2 l y f (x ,x , ,x ,q ,q , ,q ) 2 = 2 1 2 i 1 2 l y f (x ,x , ,x ,q ,q , ,q ) i = i 1 2 i 1 2 l

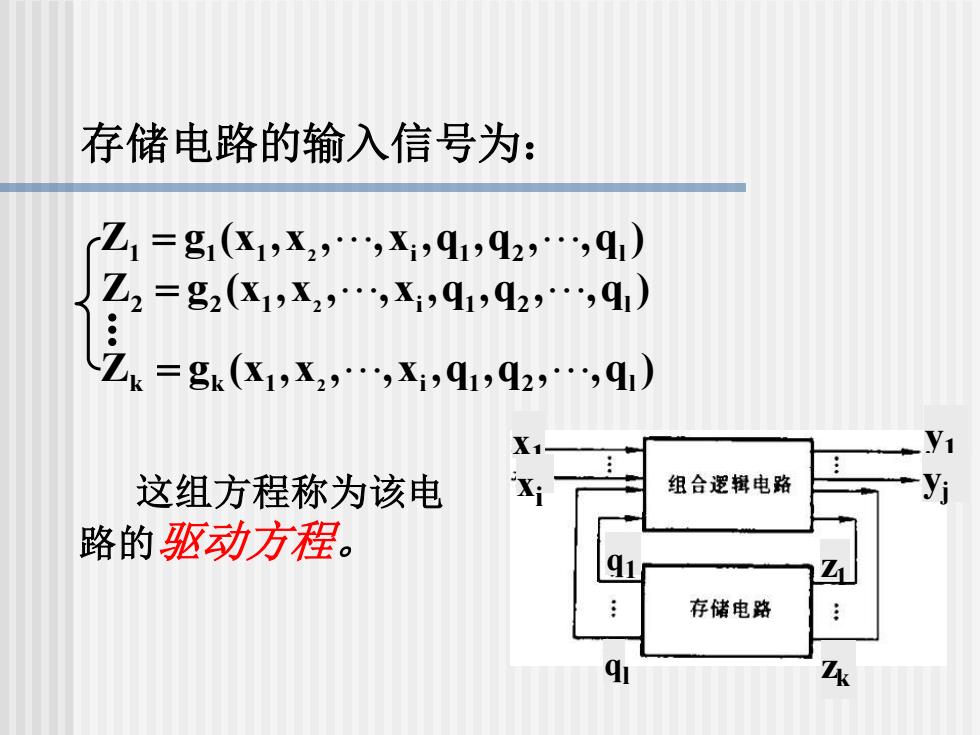

存储电路的输入信号为: Z1=g1(X13X22.,X1q13q2,.,q1) Z2=g2(X1,X2,3X1,q1,q2,q1) 号=g《X,4,9,q2g.,9 这组方程称为该电 X 组合逻辑电路 路的驱动方程。 91 存储电路 q

x1 xi y1 yj z1 zk q1 ql 这组方程称为该电 路的驱动方程。 Z g (x ,x , ,x ,q ,q , ,q ) 1 = 1 1 2 i 1 2 l Z g (x ,x , ,x ,q ,q , ,q ) 2 = 2 1 2 i 1 2 l Z g (x ,x , ,x ,q ,q , ,q ) k = k 1 2 i 1 2 l 存储电路的输入信号为:

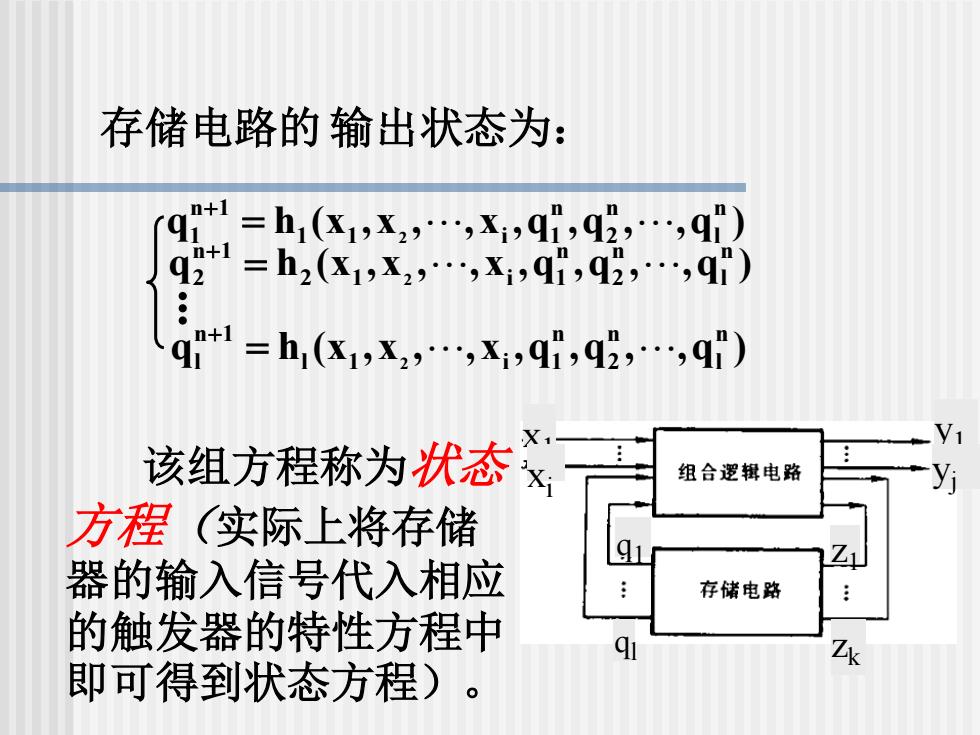

存储电路的输出状态为: =h1(区1,x,X,qi,q2,q) n+1 =h2(X1,X2,.,X,qi,92,.,q) q+1=h1(K1,X2,X,qi,q2,q)) 该组方程称为状态x 组合逻辑电路 方程(实际上将存储 91 器的输入信号代入相应 存储电路 的触发器的特性方程中 即可得到状态方程)

存储电路的 输出状态为: 该组方程称为状态 方程(实际上将存储 器的输入信号代入相应 的触发器的特性方程中 即可得到状态方程)。 x1 xi y1 yj z1 zk q1 ql q h (x ,x , ,x ,q ,q , ,q ) n l n 2 n 1 1 i 1 n 1 1 + = 2 q h (x ,x , ,x ,q ,q , ,q ) n l n 2 n 2 1 i 1 n 1 2 + = 2 q h (x ,x , ,x ,q ,q , ,q ) n l n 2 n l 1 i 1 n 1 l + = 2

如果附序电路上述三个方程 确定,则电路的逻辑功能就确定 了

如果时序电路上述三个方程 确定,则电路的逻辑功能就确定 了