第五章 触发器

第五章 触发器

教学要求 ·了解触发器的电路结构和动作特点 ·掌握触发器的逻辑功能、触发方式

教学要求 了解触发器的电路结构和动作特点 掌握触发器的逻辑功能、触发方式

5.1概述 触发器是具有记忆功能的基本逻辑电 路,它能够存贮一位二值信号。 基本特点: 1)具有两个能自行保持的稳定逻辑状 态0和1。 2)根据不同的输入信号可以置成1或0 状态。 3)在输入信号消失后,能将获得的新 状态保存下来

5.1 概述 触发器是具有记忆功能的基本逻辑电 路,它能够存贮一位二值信号。 基本特点: 1)具有两个能自行保持的稳定逻辑状 态0和1。 2)根据不同的输入信号可以置成1或0 状态。 3)在输入信号消失后,能将获得的新 状态保存下来

5.2SR锁存器

5.2 SR锁存器

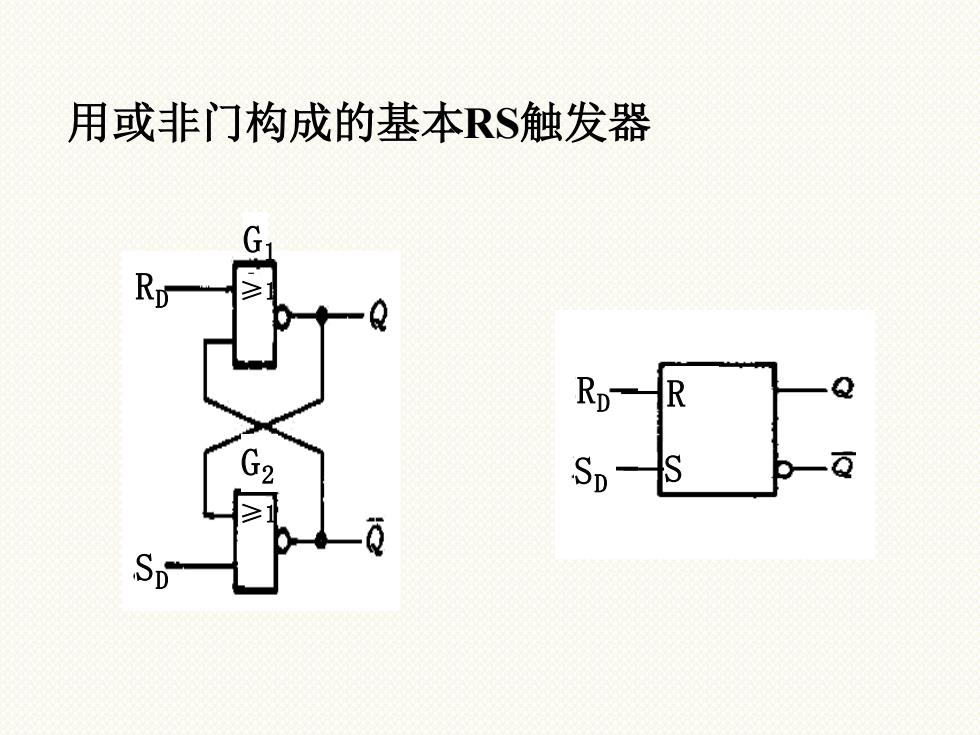

用或非门构成的基本RS触发器 R R Sp S

用或非门构成的基本RS触发器 SD RD G1 G2 ≥1 ≥1 SD RD R S

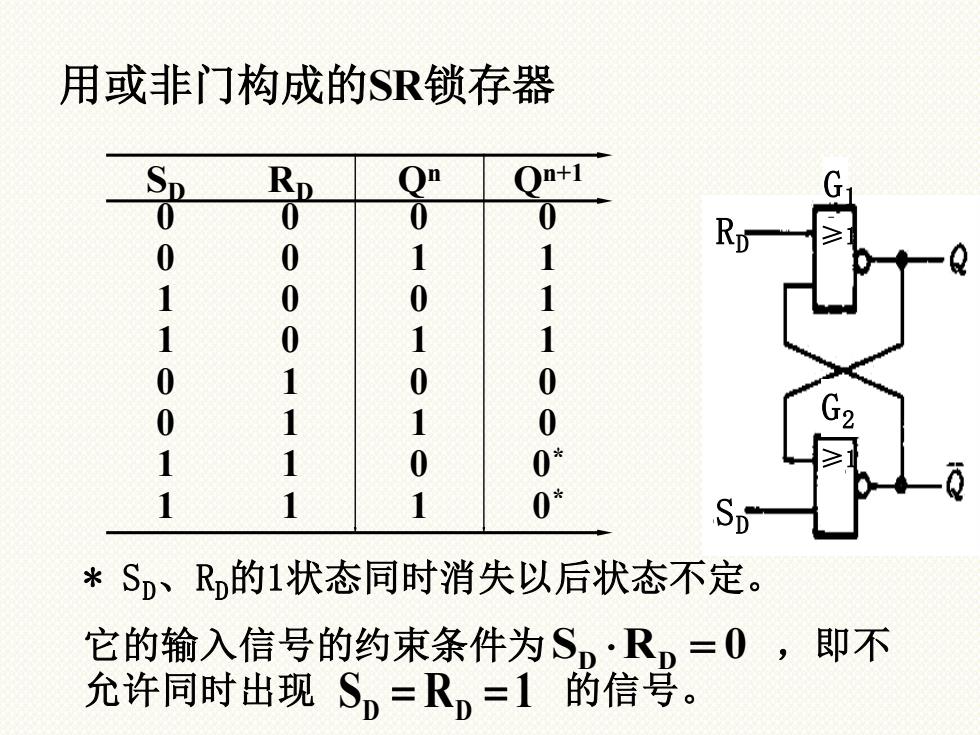

用或非门构成的SR锁存器 Sp On On+ 0 0 0 0 0 1 1 1 0 0 1 1 0 1 1 0 1 0 0 0 1 1 0 1 1 0 * 1 1 1 0* 米 S、R,的1状态同时消失以后状态不定。 它的输入信号的约束条件为SD·R。=0,即不 允许同时出现S,=R,=1的信号

用或非门构成的SR锁存器 * SD、RD的1状态同时消失以后状态不定。 SD RD G1 G2 ≥1 ≥1 SD RD Qn Qn+1 0 0 0 0 0 0 1 1 1 0 0 1 1 0 1 1 0 1 0 0 0 1 1 0 1 1 0 0 * 1 1 1 0 * 它的输入信号的约束条件为 ,即不 允许同时出现 的信号。 SD RD = 0 S R 1 D D = =

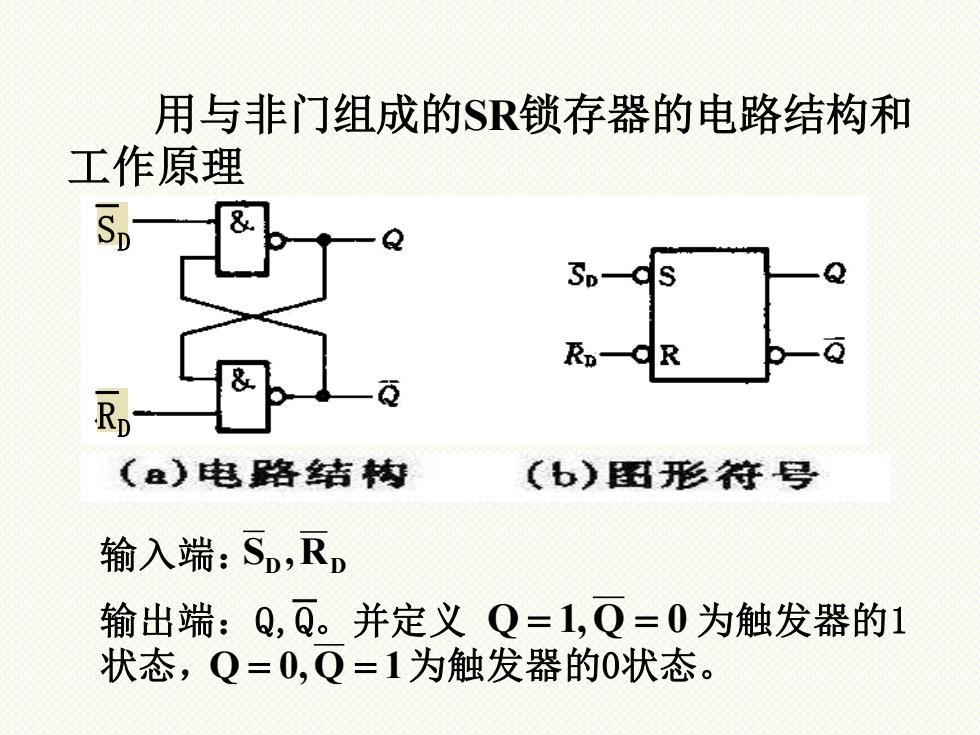

用与非门组成的SR锁存器的电路结构和 工作原理 Sp- R ()电路结肉 (b)团形符号 输入端:SD,下D 输出端:Q,Q。并定义Q=1,Q=0为触发器的1 状态,Q=0,Q=1为触发器的0状态

用与非门组成的SR锁存器的电路结构和 工作原理 SD RD 输入端: D RD S , 输出端:Q,Q。并定义 为触发器的1 状态,Q = 0,Q = 1为触发器的0状态。 Q = 1,Q = 0

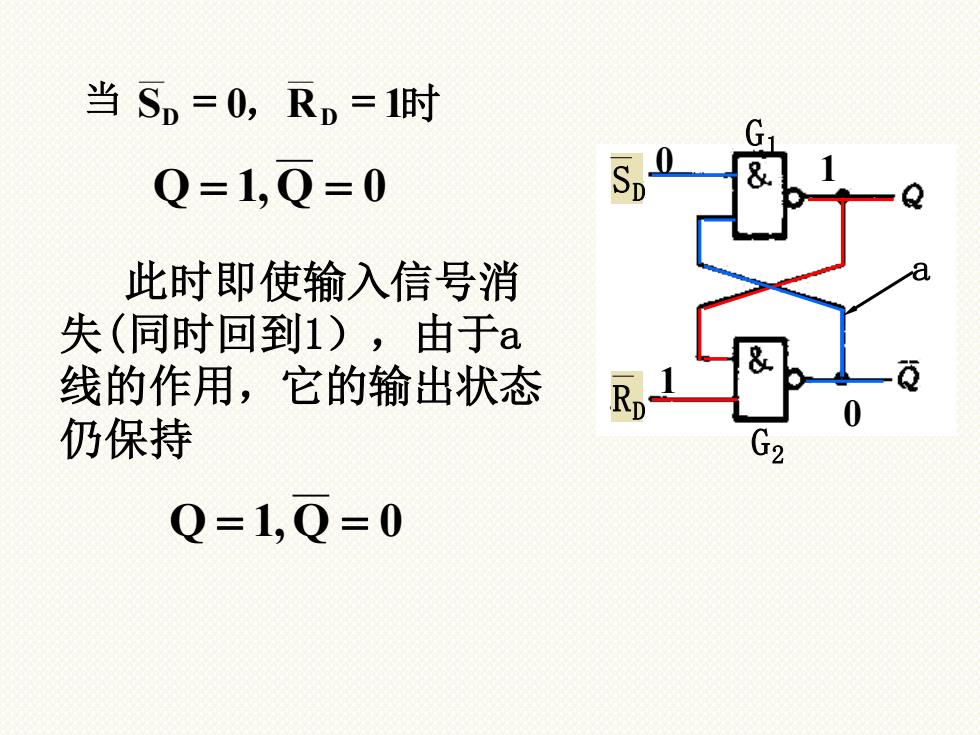

当S,=0,RD=1时 Q=1,Q=0 此时即使输入信号消 失(同时回到1),由于a 线的作用,它的输出状态 仍保持 G52 Q=1,Q=0

此时即使输入信号消 失 (同时回到 1),由于 a 线的作用,它的输出状态 仍保持 S D R D G 1G2 a Q = 1 , Q = 0 01 1 0 S D = 0 , R D = 1 时 Q = 1 , Q = 0 当

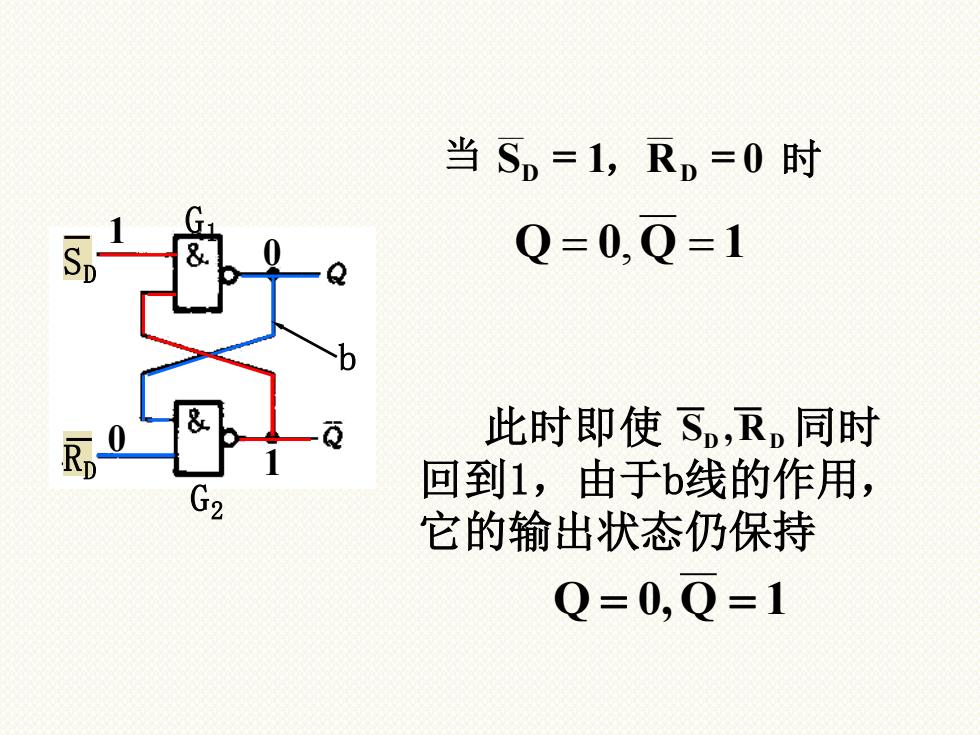

当SD=1,RD=0时 Q=0,Q=1 此时即使S,下,同时 回到1,由于b线的作用, 它的输出状态仍保持 Q=0,Q=1

此时即使 S R 同时 回到 1,由于 b线的作用, 它的输出状态仍保持 Q = 0 , Q = 1 S D R D G 1G2 b D D , 10 01 S D = 1 , R D = 0 时 Q = 0 , Q = 1 当

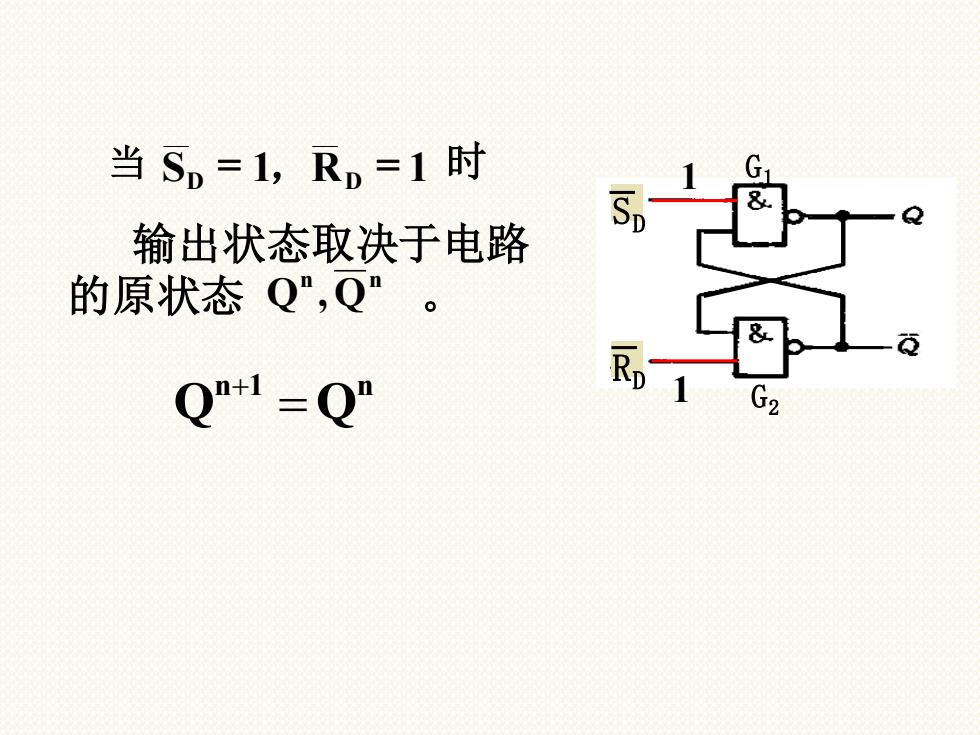

当SD=1,D=1时 输出状态取决于电路 的原状态Q”,Q”。 Q+1=Q

输出状态取决于电路 的原状态 。 n n Q , Q S D R D G 1G2 1 Q n 1 Q n 1 = + 当 S D = 1 , R D = 1 时