CP1=1,CPI≥1? Pipelining Idealism: 平衡,重复,无冲突 L1⊥23456⊥7891011⊥121314 指令1,pool,lwo Speedup =k 指令2 FL L DL ICOLFO LELWO 指令3 FLDL ICO FOLEL WO CPI≤1,IPC≥1? 指令4 FLDLCOFO卧hw9 指令5 FL DL CO FOL EL WO 指令6 FL DI ICO FO EL WO 指令7 4PL9404巴w9 指令8 1P449404马y9 指令9 Load Ifetch Reg Exec Mem Wr Store Ifetch Reg Exec Mem R-type Ifetch Reg Exec Mem Wr

CPI = 1,CPI ≥ 1? Pipelining Idealism: 平衡,重复,无冲突 Speedup = k CPI ≤1,IPC ≥ 1?

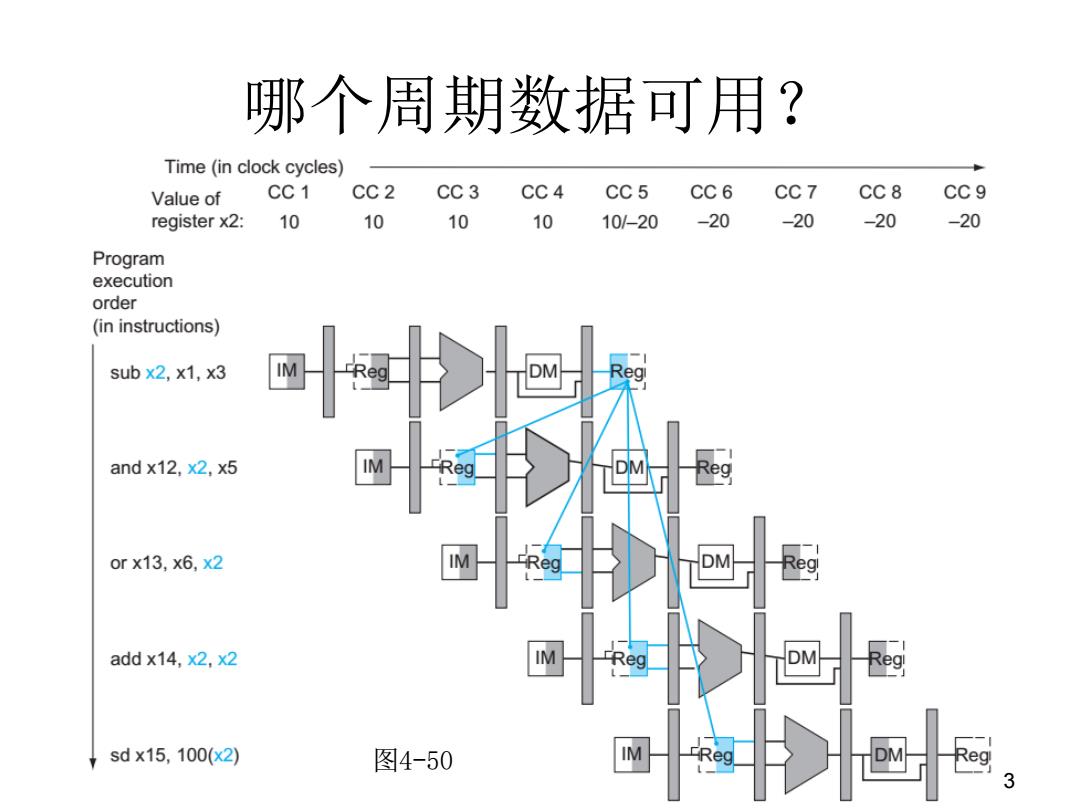

哪个周期数据可用? Time(in clock cycles) Value of CC1 CC2 CC3 CC4 CC5 CC6 CC7 CC8 CC 9 register x2: 10 10 10 10 10/-20 -20 -20 -20 -20 Program execution order (in instructions) sub x2,x1,x3 and x12,x2,x5 or x13,x6,x2 add x14,x2,x2 M sd×15,100(x2) 图4-50 Reg

3 哪个周期数据可用? 图4-50

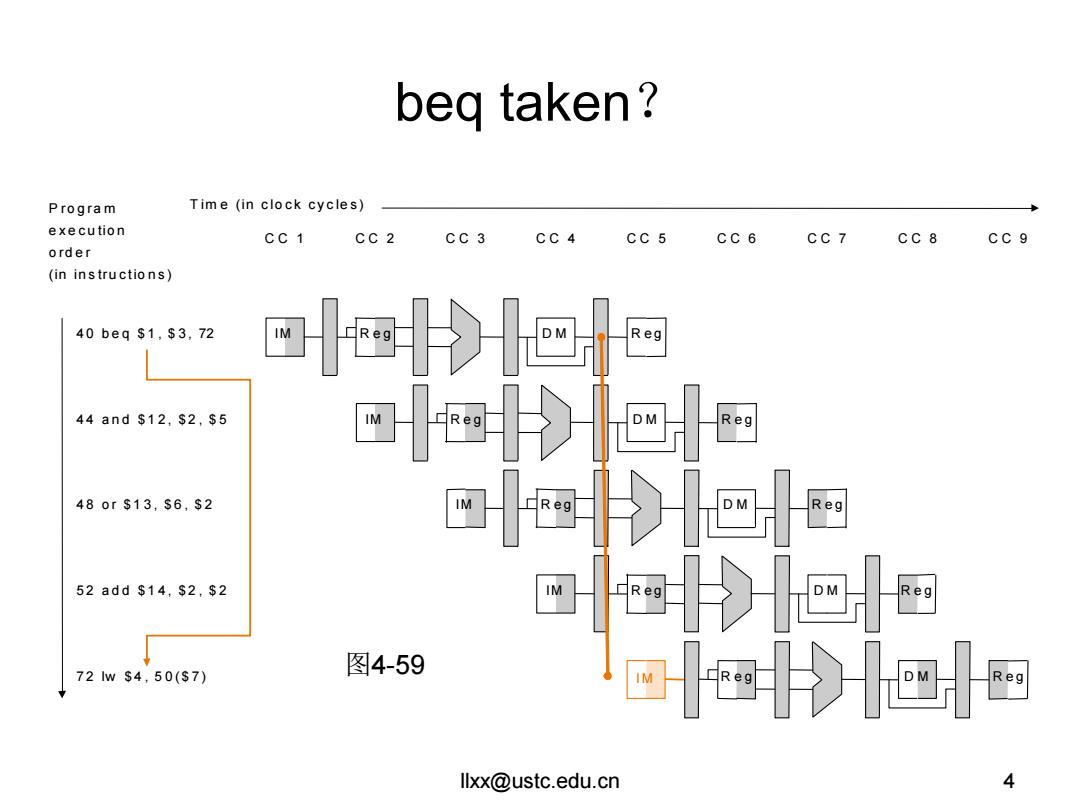

beq taken? Program Time (in clock cycles) execution CC 1 CC2 CC3 CC 5 C C6 CC 7 CC 8 CC9 order (in instructions) 40beq$1,$3,72 Reg 44and$12,$2,$5 Reg Reg 480r$13,s6,$2 IM DM Reg 52add$14,s2,$2 IM Reg Reg 72lw$4,50(s7) 图4-59 Reg llxx@ustc.edu.cn 4

llxx@ustc.edu.cn 4 beq taken? R e g R e g C C 1 T im e (in c lo c k c y c le s ) 4 0 b e q $ 1 , $ 3 , 72 P ro g ra m e x e c u tio n o rd e r (in in s tru c tio n s ) IM R e g IM D M IM D M IM D M D M D M R e g R e g R e g R e g R e g IM R e g 4 4 a n d $ 1 2 , $ 2 , $ 5 4 8 o r $ 1 3 , $ 6 , $ 2 5 2 a d d $ 1 4 , $ 2 , $ 2 7 2 lw $ 4 , 5 0 ($ 7 ) C C 2 C C 3 C C 4 C C 5 C C 6 C C 7 C C 8 C C 9 R e g 图4-59

内容提要 ·流水线技术原理:4.5 ·RV的五级流水线实现:4.6 ·Hazard问题:4.5.2 -结构冲突:stall语义,哈佛结构 -数据依赖:4.7 ·编译技术:插入nop,指令重排,寄存器重命名 ·forwarding技术:RAW ·Interlock技术:Stall -控制相关:4.8 ·编译技术:ush语义,延迟分支 ·硬件优化:提前完成,投机,预测 。多发射技术:4.10 ·硬件多线程:7.5

内容提要 • 流水线技术原理:4.5 • RV的五级流水线实现:4.6 • Hazard问题:4.5.2 – 结构冲突:stall语义,哈佛结构 – 数据依赖:4.7 • 编译技术:插入nop,指令重排,寄存器重命名 • forwarding技术:RAW • Interlock技术:Stall – 控制相关:4.8 • 编译技术:flush语义,延迟分支 • 硬件优化:提前完成,投机,预测 • 多发射技术:4.10 • 硬件多线程:7.5

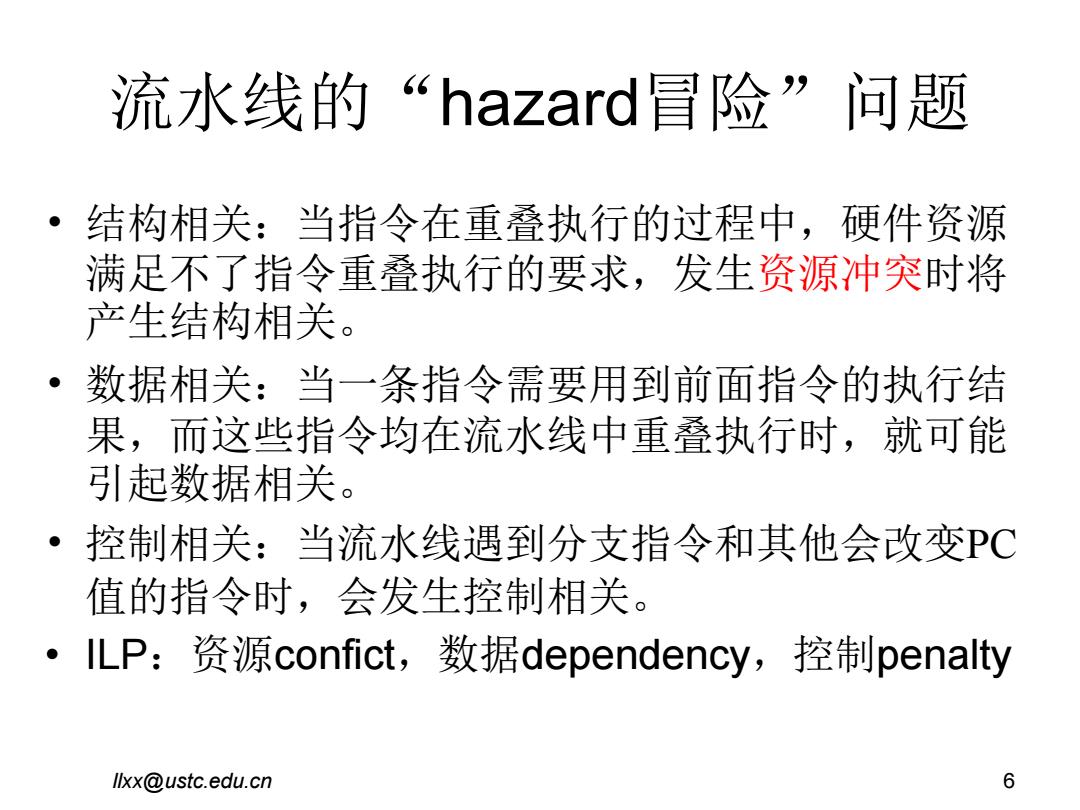

流水线的“hazard冒险”问题 结构相关:当指令在重叠执行的过程中,硬件资源 满足不了指令重叠执行的要求,发生资源冲突时将 产生结构相关。 数据相关:当一条指令需要用到前面指令的执行结 果,而这些指令均在流水线中重叠执行时,就可能 引起数据相关。 ·控制相关:当流水线遇到分支指令和其他会改变P℃ 值的指令时,会发生控制相关。 ·LP:资源confict,数据dependency,控制penalty llxx@ustc.edu.cn 6

llxx@ustc.edu.cn 6 流水线的“hazard冒险”问题 • 结构相关:当指令在重叠执行的过程中,硬件资源 满足不了指令重叠执行的要求,发生资源冲突时将 产生结构相关。 • 数据相关:当一条指令需要用到前面指令的执行结 果,而这些指令均在流水线中重叠执行时,就可能 引起数据相关。 • 控制相关:当流水线遇到分支指令和其他会改变PC 值的指令时,会发生控制相关。 • ILP:资源confict,数据dependency,控制penalty

访存结构相关 ·假设单存储器,则单周期内并发取指与读写数据存 在冲突 C2 C4 C5 C6 C7 C8 Data Lines Control Lines ALU Address Lines LOAD 正 REG 正 REG M Do Do : P 指令1 ALU A正 REG REG Da-l Dol M M 0 Ao Ao m e 0 ALU A 指令 正 REG E REG M r Am-1 Am-1 y r 指令3 ALU 正 REG 正 REG RW M xI Clock Clock llxx@ustc.edu.cn 7

llxx@ustc.edu.cn 7 访存结构相关 • 假设单存储器,则单周期内并发取指与读写数据存 在冲突

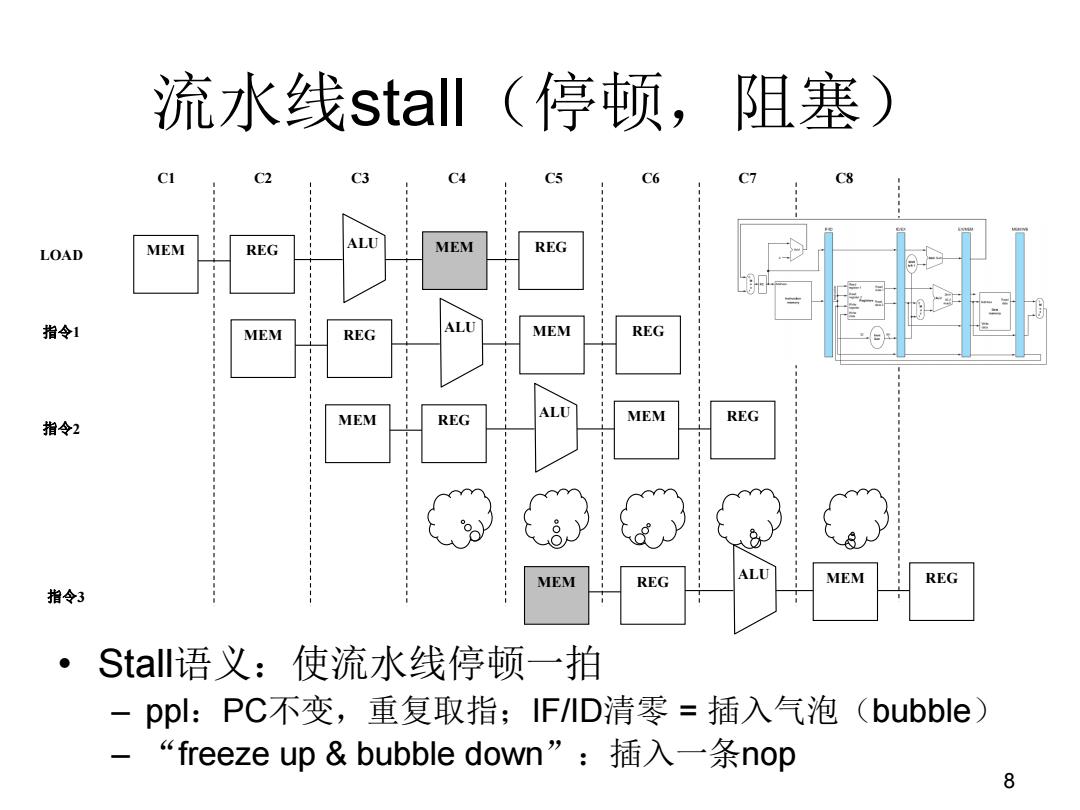

流水线stall(停顿,阻塞) C C3 C C6 C C8 LOAD MEM REG ALU MEM REG 指令1 MEM REG ALU MEM REG ALU 指令2 MEM REG MEM REG ALU MEM REG MEM REG 指令3 Stal语义:使流水线停顿一拍 -ppl:PC不变,重复取指;FID清零=插入气泡 (bubble) “freeze up&bubble down”:插入一条nop 8

8 流水线stall(停顿,阻塞) • Stall语义:使流水线停顿一拍 – ppl:PC不变,重复取指;IF/ID清零 = 插入气泡(bubble) – “freeze up & bubble down”:插入一条nop MEM REG ALU MEM REG MEM REG ALU MEM REG MEM REG ALU MEM REG MEM REG ALU MEM REG C1 C2 C3 C4 C5 C6 C7 C8 LOAD 指令1 指令2 指令3

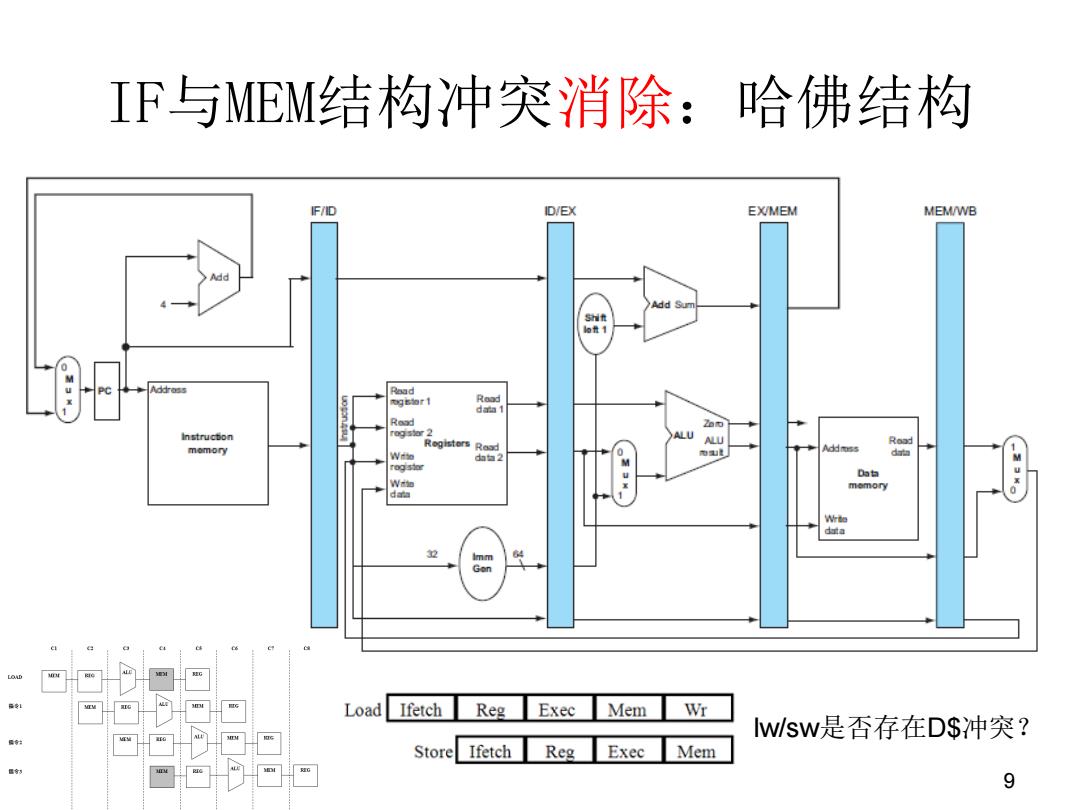

IF与MEM结构冲突消除:哈佛结构 F/D ID/EX EX/ME日M MEM/WB Add Su 51h e ag如r1 d Instructon ALU momory memory d由 Wrte dta Gon Load Ifetch Reg Exec Mem W wSw是否存在D$冲突? Store Ifetch Reg Exec Mem 9

llxx@ustc.edu.cn 9 IF与MEM结构冲突消除:哈佛结构 lw/sw是否存在D$冲突?

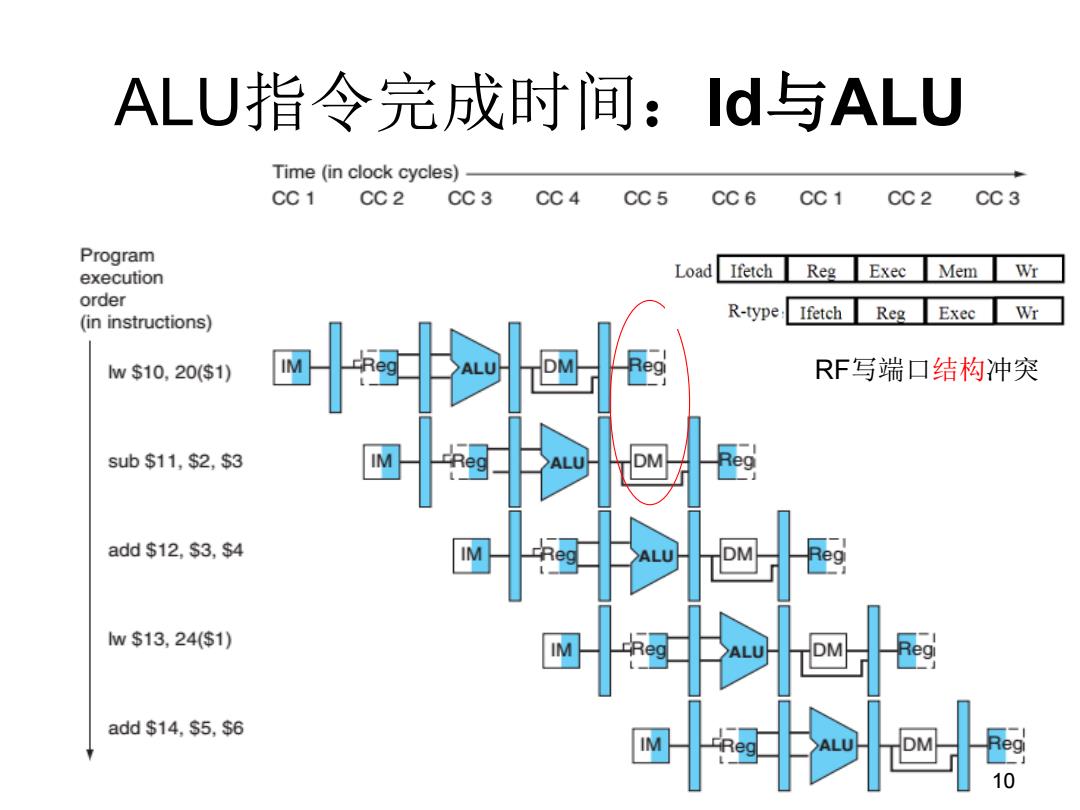

ALU指令完成时间:Id与ALU Time (in clock cycles) CC1 CC2 CC3 CC4 CC5 CC6 CC 1 CC2 CC3 Program execution Load Ifetch Reg Exec Mem Wr order (in instructions) R-type Ifetch Reg Exec Wr w$10,20($1) RF写端口结构冲突 sub$11,$2,$3 add$12,s3,$4 w$13,24($1) add$14,s5,$6 M ALU 10

10 ALU指令完成时间:ld与ALU RF写端口结构冲突

数据相关分类 ·写后读(RAW) -的执行要用到的计算结果,但可能在写入其计算结果之前 就先行对保存该结果的寄存器进行读操作。 类型:ID段依赖于EXE或MEM段 ·写后写(WAW) -和的目的操作数一样,写入顺序错误,在目标寄存器中留 下的是的值而不是的值。 ·读后写(WAR) 一可能在读取某个源寄存器的内容之前就先对该寄存器进行 写操作,导致读出的是错误的数据。 o1 哪些会发生? add ro,r2,r1 in-order,out-of-order? 1 2 and r2,ro, r1 3 sub r2,r3,#1;

11 数据相关分类 • 写后读(RAW) – j的执行要用到i的计算结果,但j可能在i写入其计算结果之前 就先行对保存该结果的寄存器进行读操作。 – 类型:ID段依赖于EXE或MEM段 • 写后写(WAW) –j和i的目的操作数一样,写入顺序错误,在目标寄存器中留 下的是i的值而不是j的值。 • 读后写(WAR) –j可能在i读取某个源寄存器的内容之前就先对该寄存器进行 写操作,导致i读出的是错误的数据。 • 哪些会发生? – in-order, out-of-order? 1 add r0,r2,r1 2 and r2,r0,r1 3 sub r2,r3,#1;