内容提要 ● 多周期设计优势:CSC采用 -时钟周期对性能的影响 一复用功能部件,减少硬件开销 ·多周期实现 一数据通路,控制器(状态机,微程序) COD5,RV Edition 2ed,$4.5 ·唐本

内容提要 • 多周期设计优势:CISC采用 – 时钟周期对性能的影响 – 复用功能部件,减少硬件开销 • 多周期实现 – 数据通路,控制器(状态机,微程序) • COD5,RV Edition_2ed,$4.5 • 唐本

指令周期:single-cycle vs.multicycle Single-cycle Implementation:.定长指令周期,定长CC clock waste waste add sto,st1,st2 beg$t0,$t1,工 Multicycle Implementation:不定长指令周期,定长CC clock add sto,st1,st2 beg $to,$t1,L Multicycle Implementation: less waste higher performance

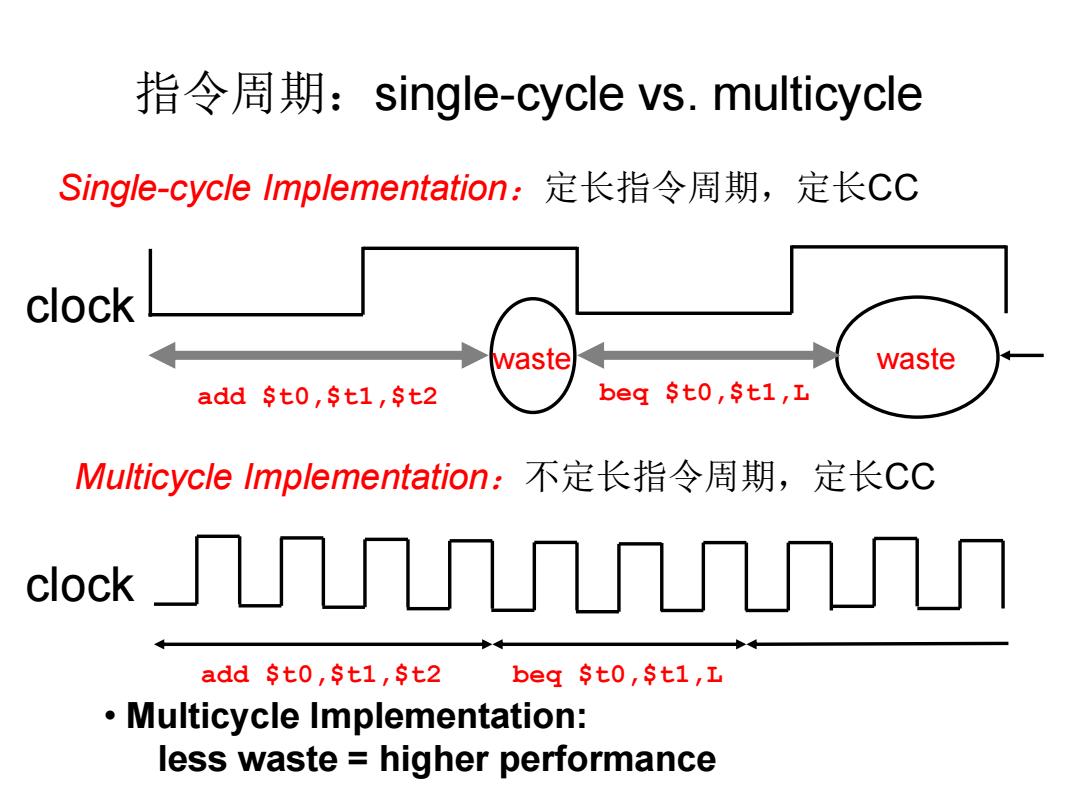

指令周期:single-cycle vs. multicycle • Multicycle Implementation: less waste = higher performance add $t0,$t1,$t2 beq $t0,$t1,L Single-cycle Implementation:定长指令周期,定长CC Multicycle Implementation:不定长指令周期,定长CC add $t0,$t1,$t2 beq $t0,$t1,L waste waste clock clock

多周期实现(COD5-RV32ed$4.5) ·将指令执行过程划分成多个阶段 -指令周期=n个机器周期 ·每个阶段(机器周期)一个时钟周期 -指令周期=n个机器周期=n个时钟周期 一在一个周期内的各个部件并行工作 ·只有控制信号有效的部件作有用功! o 时钟周期定长:假设一个时钟周期内可以完成 -一次寄存器读写(2 reads or one write),or -一次ALU操作,or 1.Instruction 2.Decode/3.Execute 4.Memory 5.Reg. Fetch Register Write -一次MEM访问(IF,w,SW)L☐ Read llxx@ustc.edu.cn 4

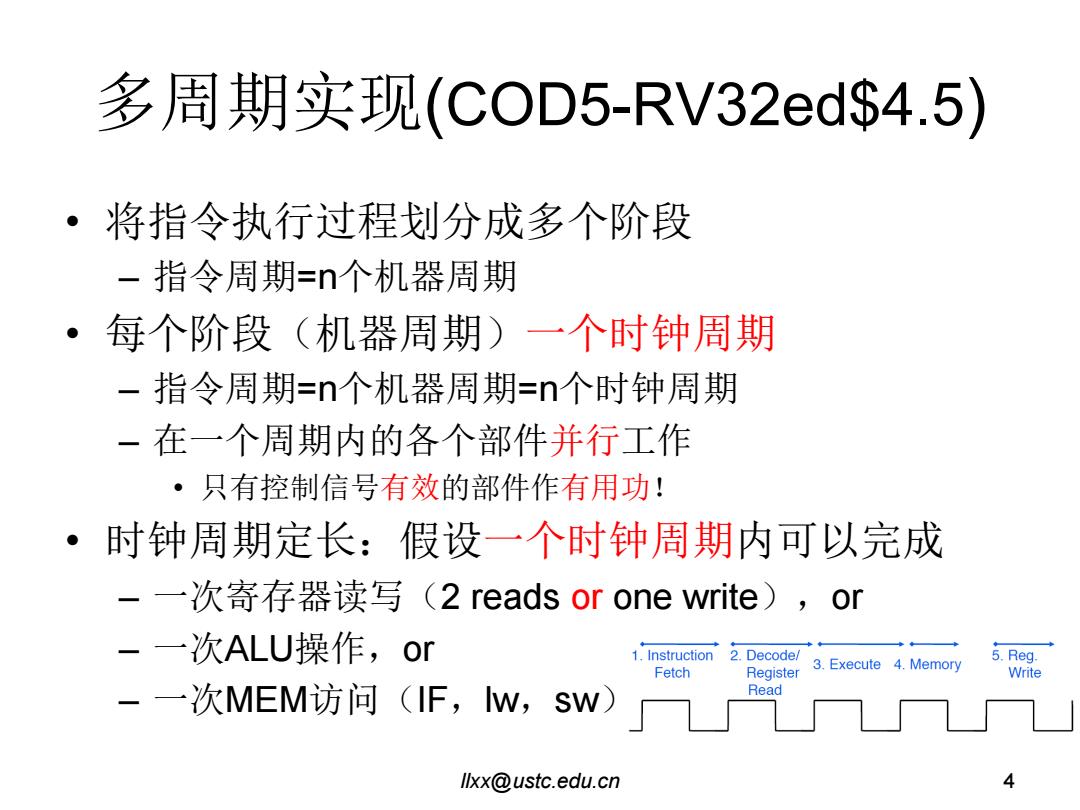

llxx@ustc.edu.cn 4 多周期实现(COD5-RV32ed$4.5) • 将指令执行过程划分成多个阶段 – 指令周期=n个机器周期 • 每个阶段(机器周期)一个时钟周期 – 指令周期=n个机器周期=n个时钟周期 – 在一个周期内的各个部件并行工作 • 只有控制信号有效的部件作有用功! • 时钟周期定长:假设一个时钟周期内可以完成 – 一次寄存器读写(2 reads or one write),or – 一次ALU操作,or – 一次MEM访问(IF,lw,sw)

指令执行的阶段划分 ·共5个阶段 1.Instruction 2.Decode/ 3.Execute 4.Memory 5.Reg. Fetch Register Write -取指:取指,PC+1 Read -译码:译码,读opr ·计算beq目标地址 -执行:R-type计算、访存地址计算,分支比较 ·分支更新(或不更新)PC(完成) - 访存:w读,sw写(完成),R-type写回(完成) -写回:w写回(完成) ● 指令周期不定长,分别为3、4、5个CC 当前时钟周期标识:主控制器据此发出所需控制信号 -周期标志触发器:clk gating FE IND EX INT 唐图8.9 -状态机:状态D CLK I→FEI→IND1一EX I一INT llxx@ustc.eau.cn 5

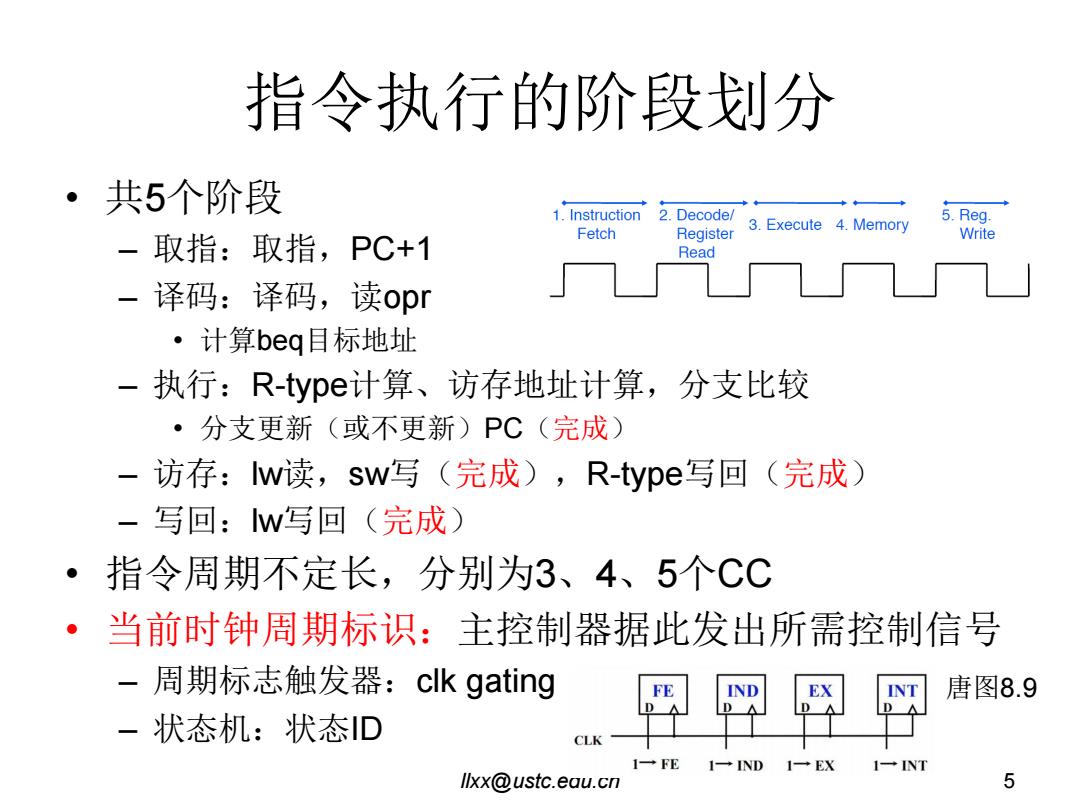

llxx@ustc.edu.cn 5 指令执行的阶段划分 • 共5个阶段 – 取指:取指,PC+1 – 译码:译码,读opr • 计算beq目标地址 – 执行:R-type计算、访存地址计算,分支比较 • 分支更新(或不更新)PC(完成) – 访存:lw读,sw写(完成),R-type写回(完成) – 写回:lw写回(完成) • 指令周期不定长,分别为3、4、5个CC • 当前时钟周期标识:主控制器据此发出所需控制信号 – 周期标志触发器:clk gating – 状态机:状态ID 唐图8.9

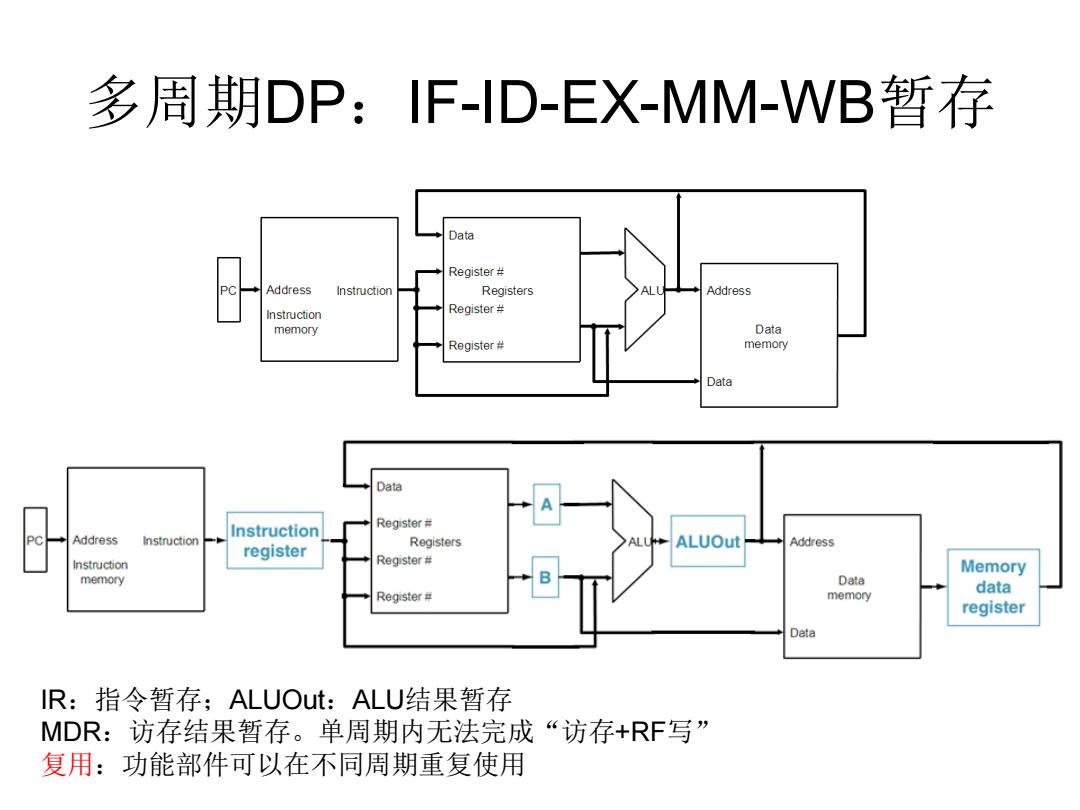

多周期DP:IF-D-EX-MM-WB暂存 Data Register PC Address Instruction Registers Address Instruction Register memory Data Register memory Data Data Instruction Register PC Address Instruction Registers ALUOut Address register Instruction Register# Memory memory Data data Register# memory register Data IR:指令暂存;ALUOut:ALU结果暂存 MDR:访存结果暂存。单周期内无法完成“访存+RF写” 复用:功能部件可以在不同周期重复使用

多周期DP:IF-ID-EX-MM-WB暂存 IR:指令暂存;ALUOut:ALU结果暂存 MDR:访存结果暂存。单周期内无法完成“访存+RF写” 复用:功能部件可以在不同周期重复使用

memory复用:IF/MM,IR=MDR? Data Instruction Register# PC Address Instruction ALUOut Address register Registers Instruction Register# Memory memory Data Register# memory data register Data Instruction register PC Address Data Instruction Register ALU● ALUOut Memory or data Registers Register Memory Data data Register register FIGURE e4.5.1,The high-level view

memory复用:IF/MM,IR=MDR? FIGURE e4.5.1,The high-level view

ALU复用:PC+1/EX/beq FIGURE e4.5.6 Action for R-type Action for memory Action for Step name instructions reference Instructions branches Instruction fetch IR <Memory[PC] Add. PC <=PC+4 Instruction decode/register fetch A<=Reg [IR[19:15]] B<=Reg [IR[24:20]] ALUOut <PC immediate Data Execution,address computation, ALUOut <A op B ALUOut <=A+immediate if (A==B) Register# branch/jump completion PC <ALUOut PC Address Instruction Registers ALU Address Register# Memory access or R-type Reg[1R11:7】<= Load:MDR <MemoryfALUOut] Data Instruction completion ALUOut or memory Register memory Store:Memory [ALUOut]<B Data Memory read completion Load:Reg[IR[11:7]]<=MDR Instruction register PC Address Data Instruction Register Memory or data Registers ALU ALUOut Register Memory Data data Register register

ALU复用:PC+1/EX/beq FIGURE e4.5.6

funct7 rs2 rs1 funct3 rd opcode R-type 多周期数据通路 immediate[11:0] rs1 funct3 rd opcode Itype mmed[11:5] rs2 rs1 funct3 immed[4:0] opcode S-type immed12,10:5] rs2 rs1 funct3 immed[4:1,11] opcode B-type 取指 lw/sw PC+4 PC 0 M Instruction Read 0 U Address [19-15] register 1 M X Read u 1 Instruction data 1 Memory Read [24-20] 1 Zero register 2 MemData Instruction Registers ALU ALU ALUOut [11-7刀 Writ Read result Write register data 2 B 0 data Instruction 1 M register Write u 0 data Instruction M [31-0] X 1 Memory Imm data Gen register beq SW I-type/lw/sw FIGURE e4.5.2 llxx@ustc.edu.cn 9

llxx@ustc.edu.cn 9 多周期数据通路 取指 lw/sw PC+4 I-type/lw/sw beq sw FIGURE e4.5.2

funct7 rs2 rs1 funct3 rd opcode R-type 多周期控制信号 immediate[11:0] rs1 funct3 rd opcode I-type immed(11:5] rs2 rs1 funct3 immed[4:0] opcode S-type immed12,10:5] rs2 rs1 funct3 immed[4:1,11] opcode B-type lorD MemRead MemWrite IRWrite RegWrite ALUSrcA PC 0 0 M Instruction Read Address [19-15] register 1 M X Read A Instruction Memory Read data 1 [24-20] Zero register 2 MemData Instruction Registers ALU ALU ALUOut [11-7刀 Write Read result Write register data 2 B M data Instruction u register o Write data Instruction M [31-0] 1 Memory Imm data Gen ALU register control Instruction [6-0] FIGURE e4.5.3 MemtoReg ALUSrcB ALUOp llxx@ustc.edu.cn 10

llxx@ustc.edu.cn 10 多周期控制信号 FIGURE e4.5.3

第一阶段:取指 根据PC从MEM中取指,IR=MEM[PC] 计算NPC,PC=PC+4 控制信号:lorD,MemRead,IRWrite;ALUSrcA,ALUSrcB ALUOp,PCWrite orD MemRead MemWrite IRWrite RegWrite ALUSrcA PC 0 Instruction Read Address [19-15 register 1 Read Instruction Read data 1 Memory [24-20] 1 Zero register 2 MemData Instruction Registers ALU ALU ALUOut [11-7刀 Write result Read Write register data 2 M data Instruction register Write data 2 Instruction [31-0 PC“后写”? Memory Imm data Gen ALU register control Instruction [6-0] MemtoReg ALUSrcB ALUOp

11 第一阶段:取指 • 根据PC从MEM中取指,IR=MEM[PC] • 计算NPC,PC=PC+4 • 控制信号:IorD, MemRead, IRWrite;ALUSrcA, ALUSrcB, ALUOp, PCWrite PC“后写”?