计算机组成原理 外设,输入输出系统 (RV$1.4$6.9,唐第5、8章) llxx@ustc.edu.cn 1

1 计算机组成原理 外设,输入输出系统 (RV $1.4 $6.9,唐第5、8章) llxx@ustc.edu.cn

o RV$1.4:外设(显示器, 触摸屏,网络) 0 RV$6.9:总线,IO系统 -示例:NetFPGA1 0G Ethernet NIC an FPGA-based open platform for network research and classroom experimentation -总线 -Control -Data ·PCl:并行总线 PCle ·PCle总线:串行总线 MAC PHY +Port 0 MAC PHY ++Port 1 -V0系统 DMA MAC PHY +Port 2 ·MMIO MAC PHY+Port 3 Polling,Interrupt-driven I/O,DMA ·设备驱动程序

• RV $1.4:外设(显示器,触摸屏,网络) • RV $6.9:总线,I/O系统 – 示例:NetFPGA 10G Ethernet NIC • an FPGA-based open platform for network research and classroom experimentation – 总线 • PCI:并行总线 • PCIe总线:串行总线 – I/O系统 • MMIO • Polling,Interrupt-driven I/O,DMA • 设备驱动程序

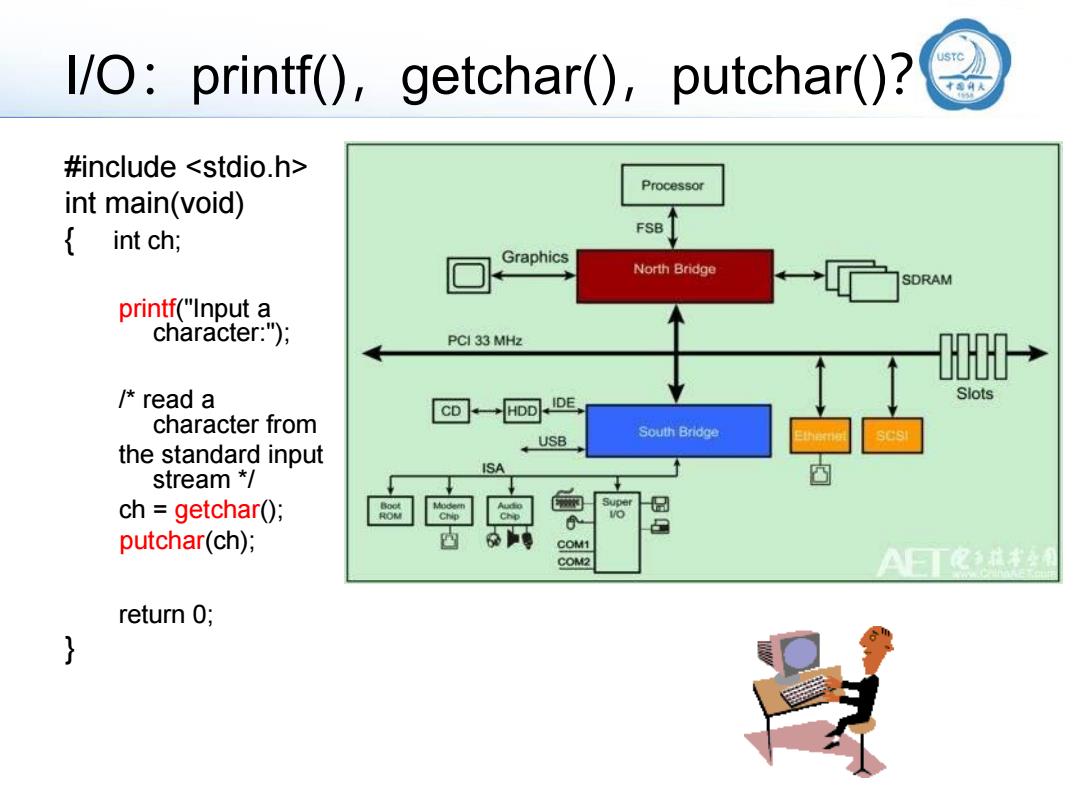

1/O:printf(),getchar(),putchar()? #include Processor int main(void) int ch; FSB Graphics North Bridge SDRAM printf("Input a character:"); PCI 33 MHz M→ /read a Slots character from [cD-ooE South Bridge the standard input USB ISA stream * ch getchar(); Super putchar(ch); COM1 COM2 return 0;

I/O:printf(),getchar(),putchar()? #include int main(void) { int ch; printf("Input a character:"); /* read a character from the standard input stream */ ch = getchar(); putchar(ch); return 0; }

KB:位置码 Key Cap d f 8 9 b Spring 哒哒嗌嗒 Mechanical switch 4 5 6 7 Conductor-coated membrane 0 2 Logical arrangement of keys Contacts Membrane switch 编码键盘:字符码(ASCI) 非编码键盘:位置码(POS机)

KB:位置码 编码键盘:字符码(ASCII) 非编码键盘:位置码(POS机)

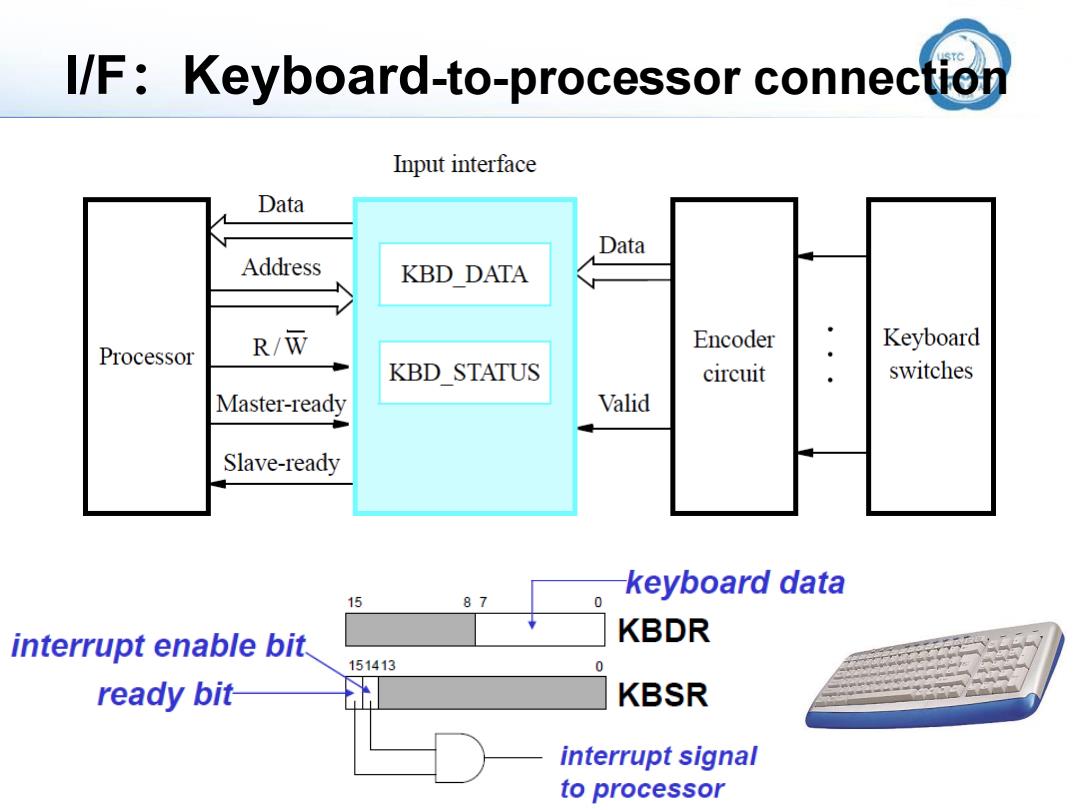

I/F:Keyboard-to-processor connection Input interface Data Data Address KBD DATA Encoder Keyboard Processor R/W KBD STATUS circuit switches Master-ready Valid Slave-ready keyboard data 15 87 0 interrupt enable bit KBDR 151413 ready bit KBSR interrupt signal to processor

I/F:Keyboard-to-processor connection

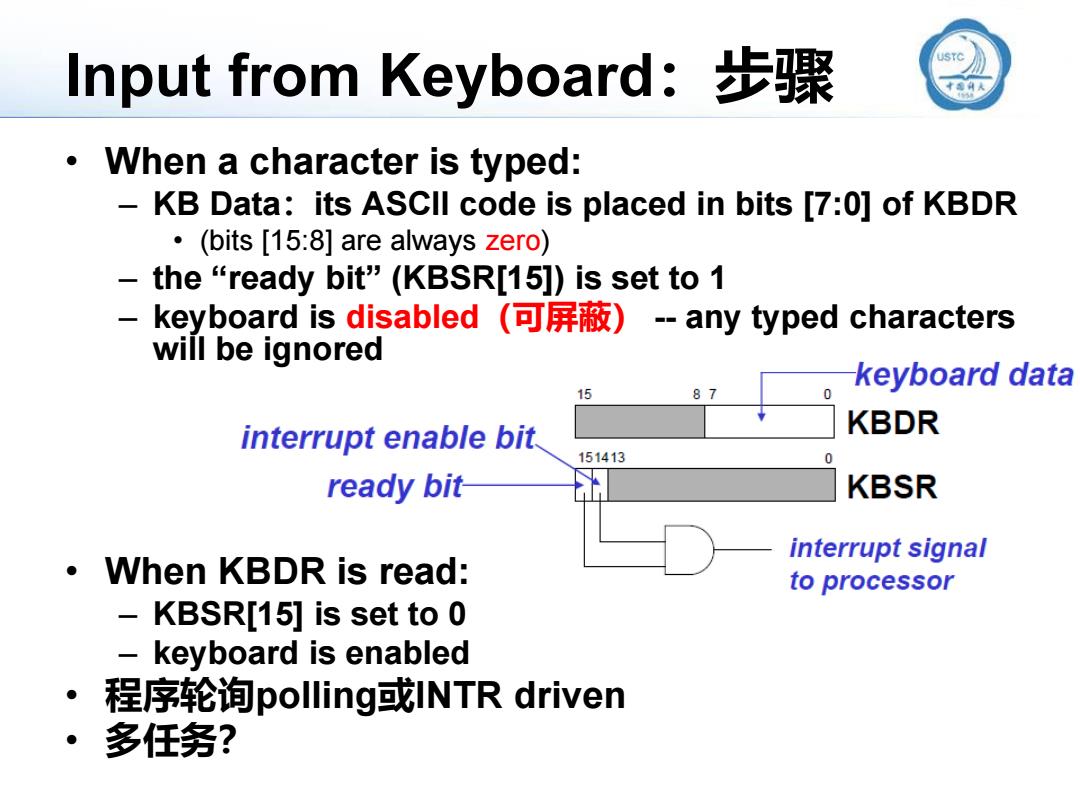

Input from Keyboard:步骤 USTC When a character is typed: KB Data:its ASCll code is placed in bits [7:0]of KBDR .(bits [15:8]are always zero) - the“ready bit'”(KBSR[15])is set to1 keyboard is disabled(可屏蔽)-any typed characters will be ignored keyboard data 15 87 0 interrupt enable bit KBDR 151413 0 ready bit KBSR interrupt signal ·Vhen KBDR is read: to processor KBSR[15]is set to 0 keyboard is enabled 程序轮询polling?或INTR driven 多任务?

Input from Keyboard:步骤 • When a character is typed: – KB Data:its ASCII code is placed in bits [7:0] of KBDR • (bits [15:8] are always zero) – the “ready bit” (KBSR[15]) is set to 1 – keyboard is disabled(可屏蔽) -- any typed characters will be ignored • When KBDR is read: – KBSR[15] is set to 0 – keyboard is enabled • 程序轮询polling或INTR driven • 多任务?

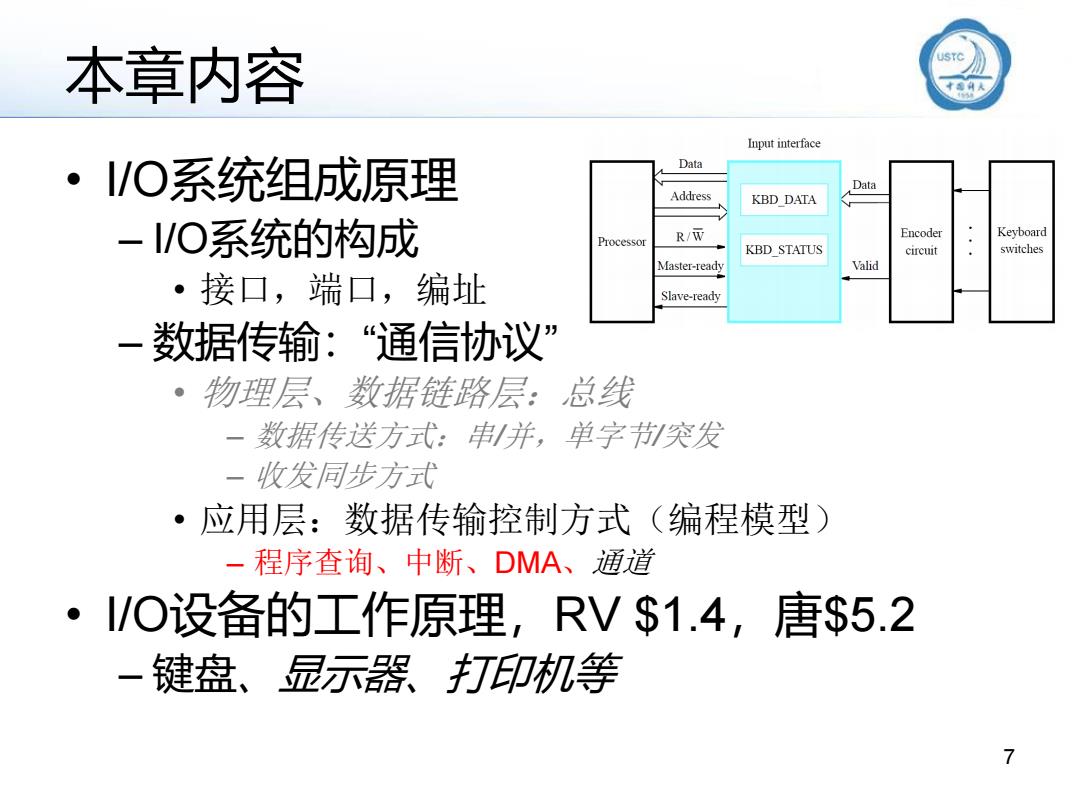

本章内容 e2》 Input interface ·/O系统组成原理 Data Data Address KBD DATA -/O系统的构成 R/W Encoder Keyboard Processor KBD STATUS circuit switches Master-ready Valid ·接口,端口,编址 Slave-ready 数据传输:“通信协议” 物理层、数据链路层:总线 一数据传送方式:串制并,单字节突发 一收发同步方式 ·应用层:数据传输控制方式(编程模型) -程序查询、中断、DMA、通道 ·/O设备的工作原理,RV$1.4,唐$5.2 一键盘、显示器打印机等 7

7 本章内容 • I/O系统组成原理 – I/O系统的构成 • 接口,端口,编址 – 数据传输:“通信协议” • 物理层、数据链路层:总线 – 数据传送方式:串/并,单字节/突发 – 收发同步方式 • 应用层:数据传输控制方式(编程模型) – 程序查询、中断、DMA、通道 • I/O设备的工作原理,RV $1.4,唐$5.2 – 键盘、显示器、打印机等

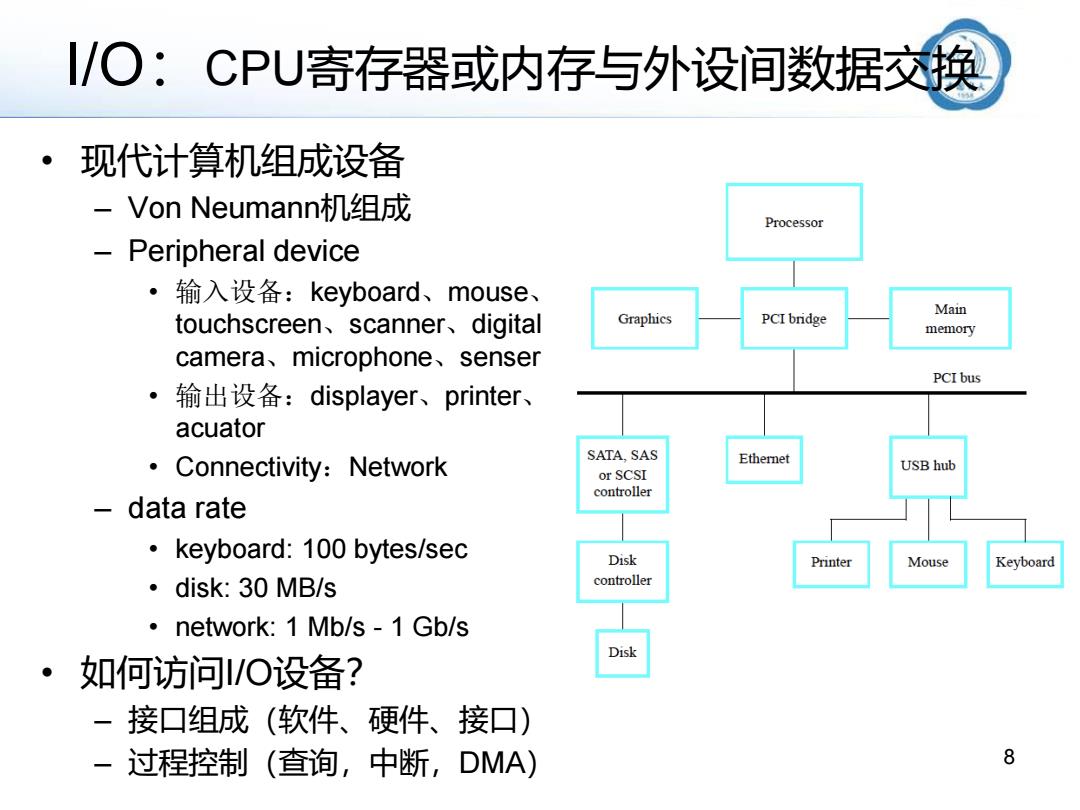

l/O:CPU寄存器或内存与外设间数据交换 现代计算机组成设备 -Von Neumann机组成 Processor Peripheral device ·输入设备:keyboard、mouse、 touchscreen、scanner、digital Graphics PCI bridge Main memory camera、microphone、senser PCI bus ·输出设备:displayer、printer、. acuator Connectivity:Network SATA,SAS Etheret or SCSI USB hub controller data rate keyboard:100 bytes/sec Disk Printer Mouse Keyboard ·disk:30MB/s controller network:1 Mb/s-1 Gb/s Disk 如何访问/O设备? -接口组成 (软件、硬件、接口) -过程控制(查询,中断,DMA) 8

8 I/O:CPU寄存器或内存与外设间数据交换 • 现代计算机组成设备 – Von Neumann机组成 – Peripheral device • 输入设备:keyboard、mouse、 touchscreen、scanner、digital camera、microphone、senser • 输出设备:displayer、printer、 acuator • Connectivity:Network – data rate • keyboard: 100 bytes/sec • disk: 30 MB/s • network: 1 Mb/s - 1 Gb/s • 如何访问I/O设备? – 接口组成(软件、硬件、接口) – 过程控制(查询,中断,DMA)

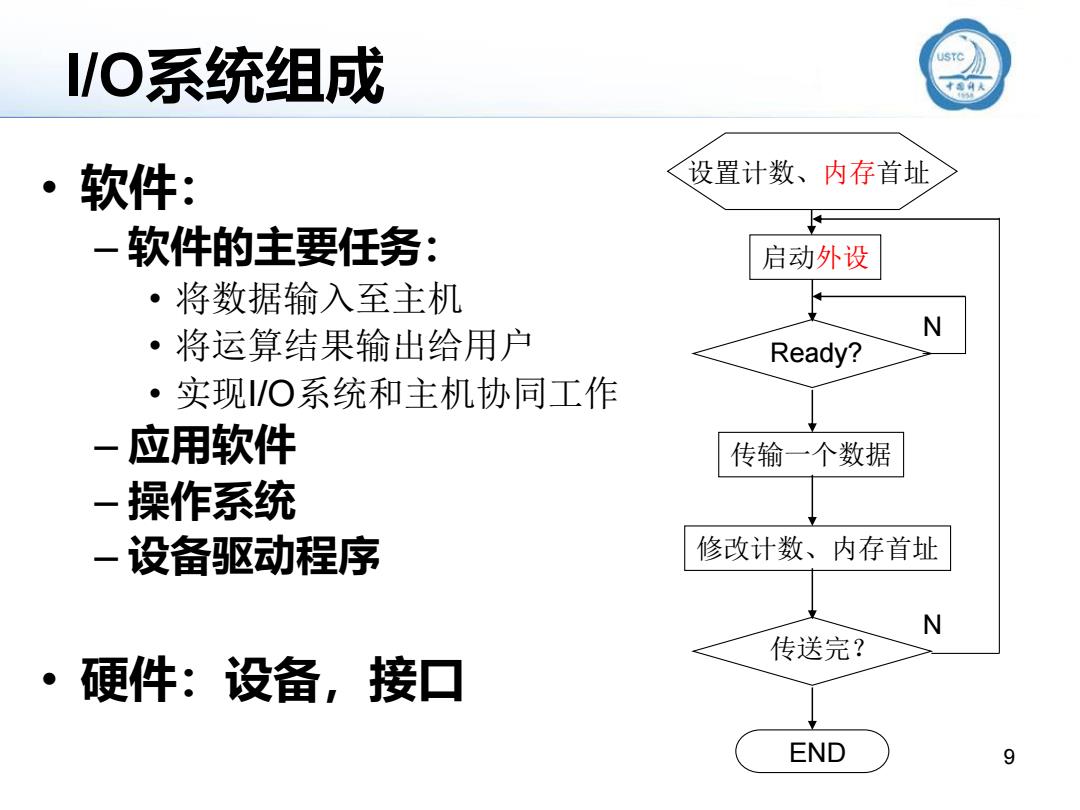

/O系统组成 。软件: 设置计数、内存首址 一软件的主要任务: 启动外设 ·将数据输入至主机 。 N 将运算结果输出给用户 Ready? 实现/O系统和主机协同工作 一应用软件 传输一个数据 一操作系统 一设备驱动程序 修改计数、内存首址 N 传送完? 。硬件:设备,接口 END 9

9 I/O系统组成 • 软件: – 软件的主要任务: • 将数据输入至主机 • 将运算结果输出给用户 • 实现I/O系统和主机协同工作 – 应用软件 – 操作系统 – 设备驱动程序 • 硬件:设备,接口 Ready? N 传输一个数据 修改计数、内存首址 传送完? N END 设置计数、内存首址 启动外设

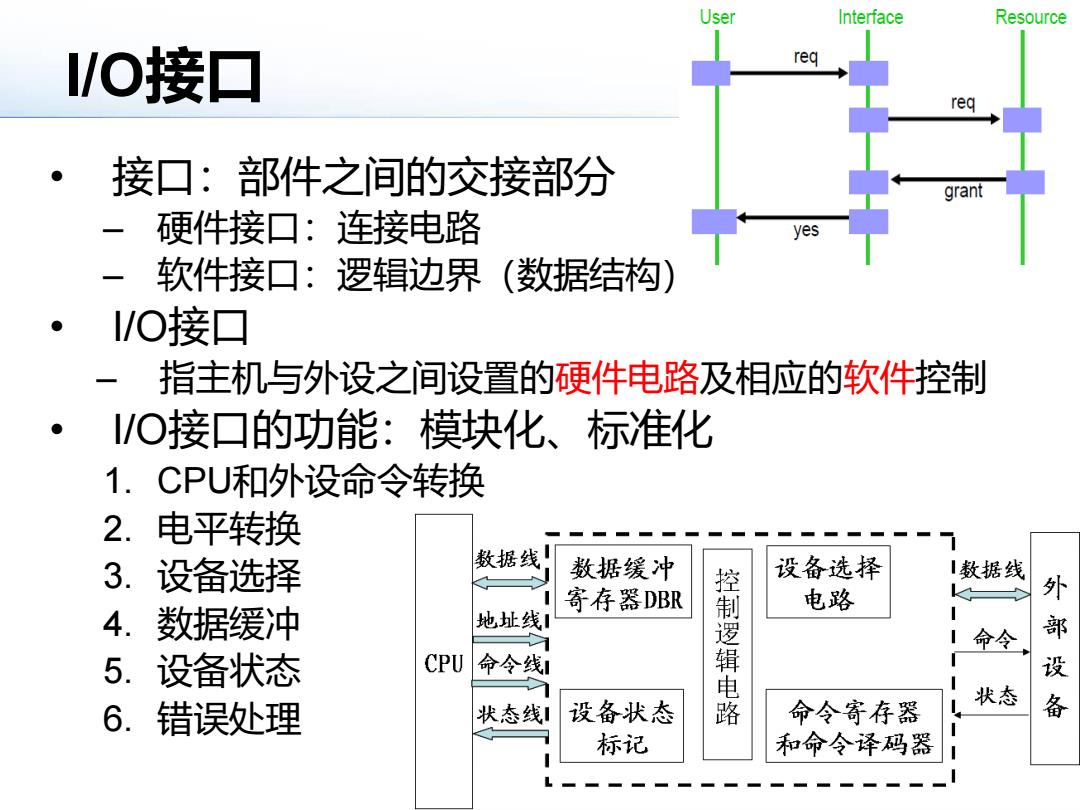

User Interface Resource /O接口 re rea 接口:部件之间的交接部分 硬件接口:连接电路 yes 软件接口:逻辑边界(数据结构) I/O接口 -指主机与外设之间设置的硬件电路及相应的软件控制 O接口的功能:模块化、标准化 1.CPU和外设命令转换 2.电平转换 3.设备选择 数据线 数据缓冲 设备选择 I数据线 寄存器DBR 电路 外 4.数据缓冲 控制 地址线 1命令 部 5.设备状态 CPU 命令线! 辑 设 6.错误处理 状态线」 设备状态 命令寄存器 状态 备 标记 和命令译码器

10 I/O接口 • 接口:部件之间的交接部分 – 硬件接口:连接电路 – 软件接口:逻辑边界(数据结构) • I/O接口 – 指主机与外设之间设置的硬件电路及相应的软件控制 • I/O接口的功能:模块化、标准化 1. CPU和外设命令转换 2. 电平转换 3. 设备选择 4. 数据缓冲 5. 设备状态 6. 错误处理