内容提要 Digital Design and Computer Architecture ·流水线技术原理:4.5 ·RV的五级流水线实现:4.6 M< -Verilog行为级定义:4.13 MODERN PROCESSOR DESIGN 物 。Hazard问题:4.5.2 一结构冲突:哈佛结构 -数据依赖:4.7 ·编译技术:插入nop,指令重排,寄存器重命名 MIPS体系结构透 ·forwarding技术:RAW ·Interlock技术:Stall Run -控制相关:4.8 ·编译技术:延迟分支 ·硬件优化:提前完成,投机,预测 。多发射技术:4.10 Parallel Computer Organization 硬件多线程:6.4 and Design

内容提要 • 流水线技术原理:4.5 • RV的五级流水线实现:4.6 – Verilog行为级定义:4.13 • Hazard问题:4.5.2 – 结构冲突:哈佛结构 – 数据依赖:4.7 • 编译技术:插入nop,指令重排,寄存器重命名 • forwarding技术:RAW • Interlock技术:Stall – 控制相关:4.8 • 编译技术:延迟分支 • 硬件优化:提前完成,投机,预测 • 多发射技术:4.10 • 硬件多线程:6.4

Laundry Example 6 PM 7 8 9 10 11 Midnight 6PM 7 8 9 10 11 Midnight Time Time 30'402030'40203040203040'20 304040404020 T T a 同 6 福¥ d 6 6 同 6 。·4袋衣服:Wash(30),dry(40),fold(20) - Sequential Laundry:需要6小时:4x(30+40+20)=360分钟⑧ - Pipelined Laundry:需3.5小时:30+4x40+20=210分钟© ·前提:1)过程可分解,2)设备独立(单缸/滚筒,双缸?),3)作业等时 ·贪心:Start work ASAP!一袋衣服? ·流水线目标:提升“吞吐率”,缩短“完成时间”。IPC?CP? CSC顺序模型,RISC指令级并行模型(LP)

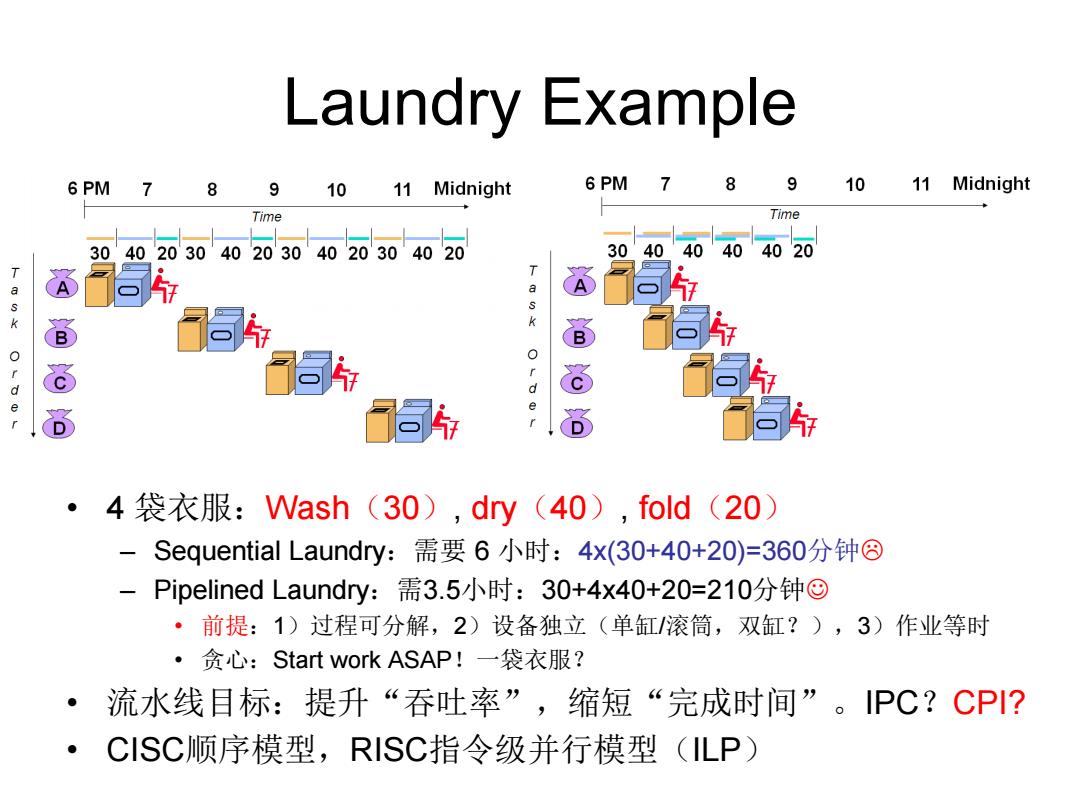

Laundry Example • 4 袋衣服:Wash(30), dry(40), fold(20) – Sequential Laundry:需要 6 小时:4x(30+40+20)=360分钟 – Pipelined Laundry:需3.5小时:30+4x40+20=210分钟☺ • 前提:1)过程可分解,2)设备独立(单缸/滚筒,双缸?),3)作业等时 • 贪心:Start work ASAP!一袋衣服? • 流水线目标:提升“吞吐率”,缩短“完成时间”。IPC?CPI? • CISC顺序模型,RISC指令级并行模型(ILP)

指令流水线时空图(Gantt chart):六级 CPI=?IPC=? L1L23456L78⊥910111213114 指令1巴,lp9 指令2 指令3 指令4 Lplc9FoE画wg 指令5 FI DI COFOL EL WO 指令6 E巴PLlC9ELwo 指令7 FL DIICOLFO EL WO 指令8 {D49马w9 指令9 4P449404马y llxx@ustc.edu.cn

llxx@ustc.edu.cn 4 指令流水线时空图(Gantt chart):六级 CPI=? IPC=?

流水线性能:Pipelining Idealism ·CPI,IPC,加速比(speedup) -单周期,多周期,ppl? 非流水线执行时间 n*k*△t speedup= lim =k 流水线执行时间 n->0 k*△t+(n-1)*△t 从CC6开始,每个周期流出一条 指令,因此,CPI=IPC≈1。 L1L23L4⊥56⊥78⊥91011121314 每条指令的指令周期没变 指令1,poFo弘,wg 整体性能提升 指令3、 FL DLICO FOLEL WO 最坏情况?最好情况?PC≥1? 指令4 FL DL COFOLEL WO 指令5 FL DLCO FOLEL WO PPL越深越好? 指令6 FL DLCOFO ELWO 指令7 FL DL CO FOL EL WO 指令8 249马y9 指令9 144494马y9

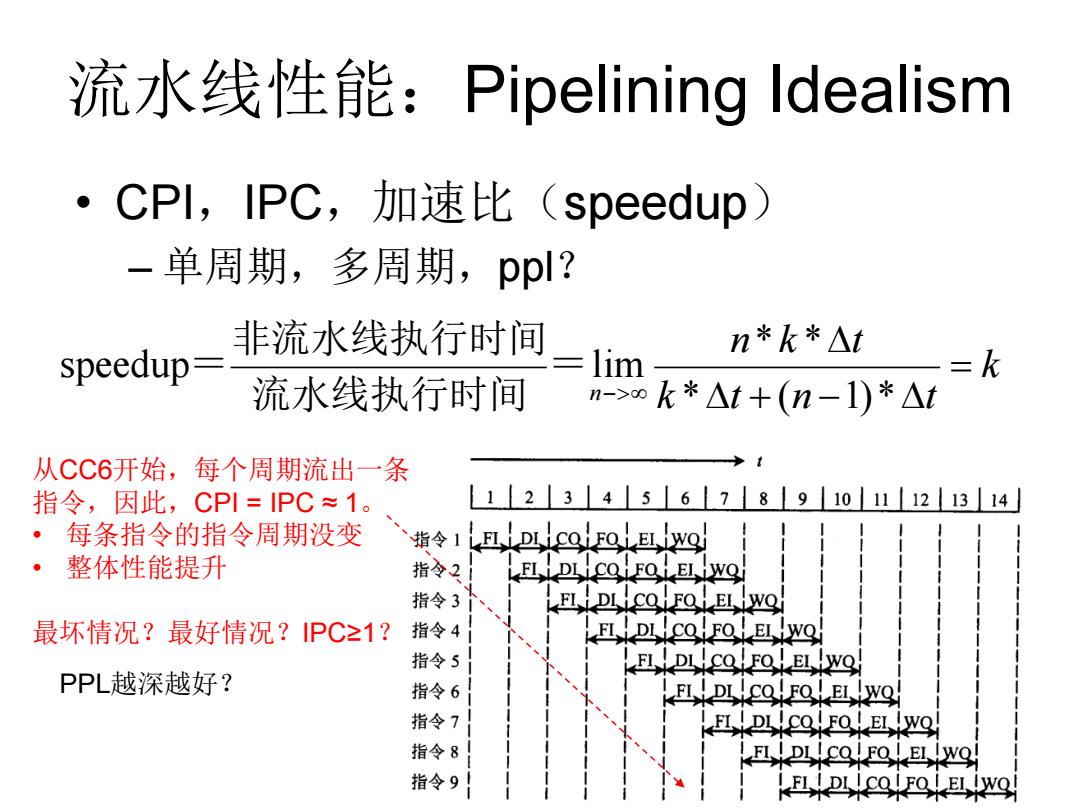

5 流水线性能:Pipelining Idealism • CPI,IPC,加速比(speedup) – 单周期,多周期,ppl? k k t n t n k t n = + − − * ( 1)* * * speedup =lim 流水线执行时间 非流水线执行时间 = 从CC6开始,每个周期流出一条 指令,因此,CPI = IPC ≈ 1。 • 每条指令的指令周期没变 • 整体性能提升 最坏情况?最好情况?IPC≥1? PPL越深越好?

流水线分类 ·单功能流水线:只能完成一种功能的流水线,如浮点加法流水线。 多功能流水线:流水线的各段可以进行不同的连接,从而使流水线在 不同的时间完成不同的功能。 ·静态流水线:在某一时间段内,流水线的各段只能按同一种功能的连 接方式工作,即只有当输入是一串相同性质的操作时其性能才能得到 发挥。 动态流水线:在某一段时间内,某些段正在实现某类操作(定点乘), 其他段却在实现另一类操作(浮点加)。 顺序流水线:流水线的流出顺序与其流入顺序相同。 ·乱序流水线:流水线的流出顺序与其流入顺序不同。 静态调度流水线:不对指令执行顺序进行重排序。 动态调度流水线:对指令执行顺序进行重排序(“指令调度”)。 6

6 流水线分类 • 单功能流水线:只能完成一种功能的流水线,如浮点加法流水线。 • 多功能流水线:流水线的各段可以进行不同的连接,从而使流水线在 不同的时间完成不同的功能。 • 静态流水线:在某一时间段内,流水线的各段只能按同一种功能的连 接方式工作,即只有当输入是一串相同性质的操作时其性能才能得到 发挥。 • 动态流水线:在某一段时间内,某些段正在实现某类操作(定点乘), 其他段却在实现另一类操作(浮点加)。 • 顺序流水线:流水线的流出顺序与其流入顺序相同。 • 乱序流水线:流水线的流出顺序与其流入顺序不同。 • 静态调度流水线:不对指令执行顺序进行重排序。 • 动态调度流水线:对指令执行顺序进行重排序(“指令调度”)

RV指令流水线技术 图4-24 Instruction Register ALU Data Register Total ·分解指令执行步骤 Instruction class fetch read operation access write time Load doubleword (ld) 200ps 100ps 200ps 200ps 100ps 800ps 一流水线“级”/“段” Store doubleword(sd) 200ps 100ps 200ps 200ps 700ps R-format(add,sub, 200pS 100ps 200ps 100ps 600ps and,or) 一每个流水段所需的时间 Branch (beq) 200ps 100ps 200ps 500ps ·一个时钟周期(机器周期) Program 一流水线深度:段数 execution 200 400600 800 1000120014001600 1800 Time order ·深好浅好? (in instructions) dx1,100(x4) Instruction Data fetch Reg ALU access Reg ·Pipelining Idealism dX2,200x4 800ps nstruction Data fetch Reg ALU Reg access -各段均衡(latency) 1dX3.400x4) Instruction 800ps fetch ·执行时间长的流水段将成 800ps 为瓶颈,造成block/stall Program execution 200 400 600800 100012001400 Time 一重复相同的指令 order (in instructions) ·单功能流水线 dx1.100(x4) Instructior Reg ALU Data fetch access Reg Instruction ALU Data 一指令流无依赖 1dx2,200(x4) 200ps Reg fetch access Reg Instruction ALU Data dx3.400(x4) 200ps fetch Reg access 图4-25 200ps200ps200ps200ps200ps 7

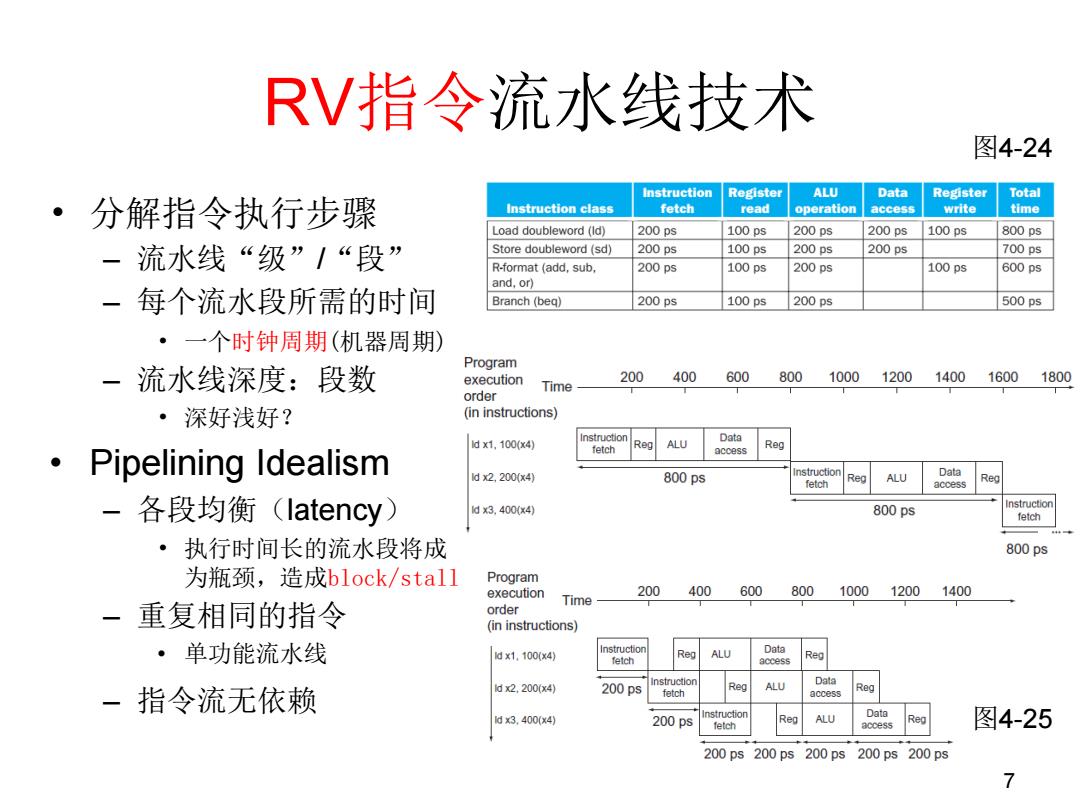

7 RV指令流水线技术 • 分解指令执行步骤 – 流水线“级”/“段” – 每个流水段所需的时间 • 一个时钟周期(机器周期) – 流水线深度:段数 • 深好浅好? • Pipelining Idealism – 各段均衡(latency) • 执行时间长的流水段将成 为瓶颈,造成block/stall – 重复相同的指令 • 单功能流水线 – 指令流无依赖 图4-25 图4-24

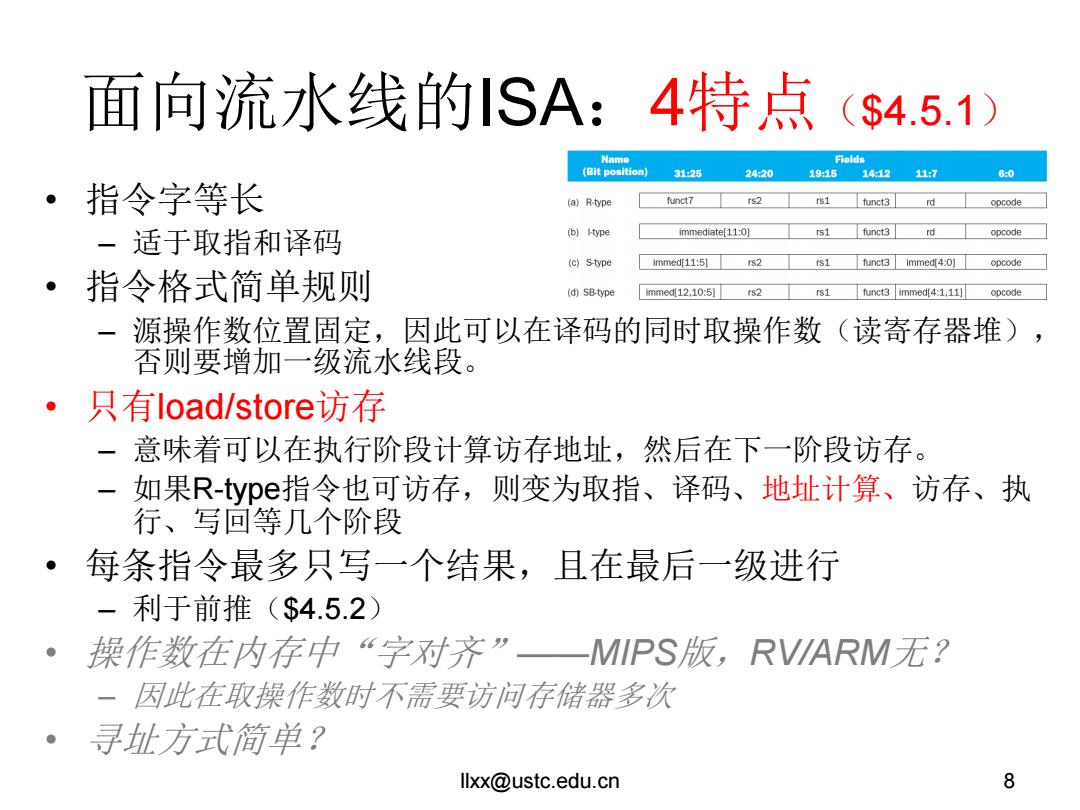

面向流水线的1SA:4特点($4.5.1) Namo Fiolds (Bit position) 31:25 24:20 19:15 14:12 11:7 6:0 ·指令字等长 (a)R-type funct7 rs2 rs1 tunct3 rd opcode 一适于取指和译码 (b)Itype immediate[11:0] rs1 funct3 rd opcode (c)S-type immed[11:5] rs2 rs1 funct3 immed[4:0] opcode 指令格式简单规则 (d)SB-type immed[12.10:5]rs2 rs1 funct3 immed[4:1.11] opcode 源操作数位置固定,因此可以在译码的同时取操作数(读寄存器堆), 否则要增加一级流水线段。 只有load/store访存 - 意味着可以在执行阶段计算访存地址,然后在下一阶段访存。 如果R-type指令也可访存,则变为取指、译码、地址计算、访存、执 行、写回等几个阶段 ·每条指令最多只写一个结果,且在最后一级进行 -利于前推($4.5.2) 操作数在内存中“字对齐”一MIPS版,RV/ARM无? 一因此在取操作数时不需要访问存储器多次 寻址方式简单? llxx@ustc.edu.cn 8

llxx@ustc.edu.cn 8 面向流水线的ISA:4特点($4.5.1) • 指令字等长 – 适于取指和译码 • 指令格式简单规则 – 源操作数位置固定,因此可以在译码的同时取操作数(读寄存器堆), 否则要增加一级流水线段。 • 只有load/store访存 – 意味着可以在执行阶段计算访存地址,然后在下一阶段访存。 – 如果R-type指令也可访存,则变为取指、译码、地址计算、访存、执 行、写回等几个阶段 • 每条指令最多只写一个结果,且在最后一级进行 – 利于前推($4.5.2) • 操作数在内存中“字对齐”——MIPS版,RV/ARM无? – 因此在取操作数时不需要访问存储器多次 • 寻址方式简单?

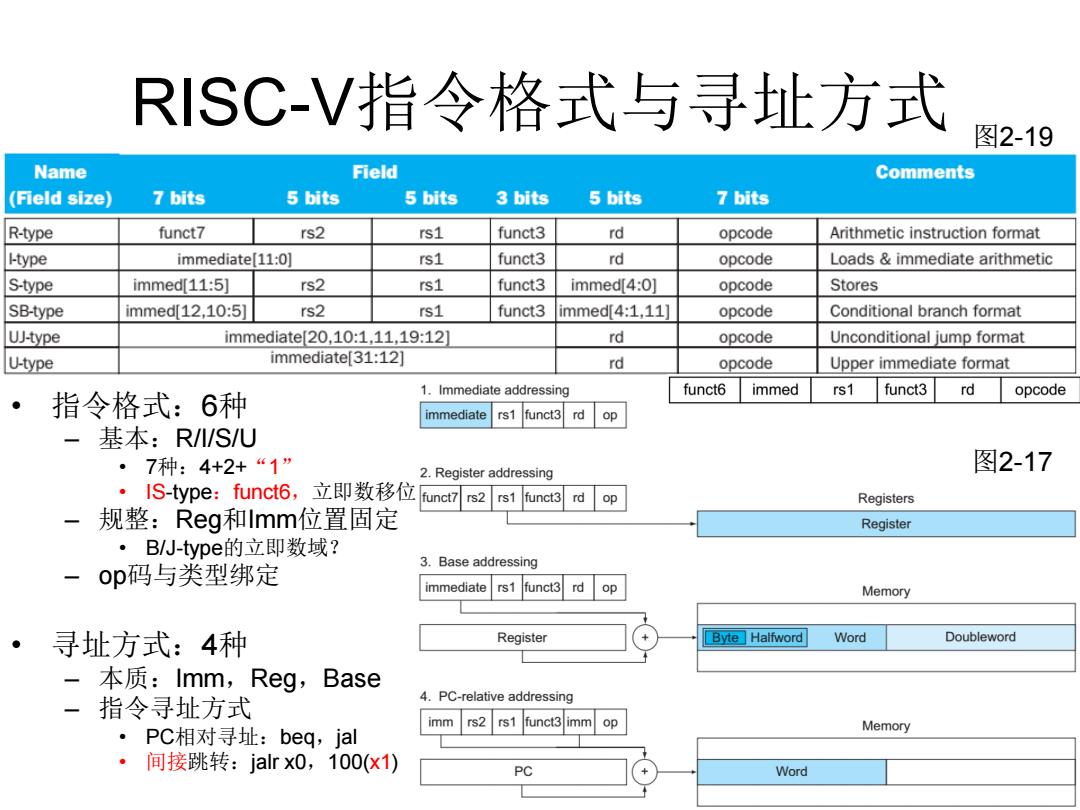

RISC-V指令格式与寻址方式 图2-19 Name Field Comments (Field size】 7 bits 5 bits 5 bits 3 bits 5 bits 7 bits R-type funct7 rs2 rs1 funct3 rd opcode Arithmetic instruction format I-type immediate[11:0] rs1 funct3 rd opcode Loads immediate arithmetic S-type immed[11:5] rs2 rs1 funct3 immed[4:0] opcode Stores SB-type immed12,10:5] rs2 rs1 funct3 immed[4:1,11] opcode Conditional branch format UJ-type immediate[20,10:1,11,19:12] rd opcode Unconditional jump format U-type immediate[31:12] rd opcode Upper immediate format 1.Immediate addressing funct6 immed rs1 funct3 rd opcode 指令格式:6种 immediate rs1 funct3rd op - 基本:RI/S/U ·7种:4+2+“1” 2.Register addressing 图2-17 ·lS-type:functe6,立即数移位 funct7 rs2 rs1 funct3 rd op Registers 规整:Reg和lmm位置固定 Register ·BJ-type的立即数域? op码与类型绑定 3.Base addressing - immediate rs1 funct3rd op Memory 寻址方式:4种 Register Byte Halfword Word Doubleword - 本质:lmm,Reg,Base 指令寻址方式 4.PC-relative addressing imm rs2 rs1 funct3imm op ·PC相对寻址:beq,jal Memory ·间接跳转:jalr x0,100(x1) PC Word

RISC-V指令格式与寻址方式 • 指令格式:6种 – 基本:R/I/S/U • 7种:4+2+“1” • IS-type:funct6,立即数移位 – 规整:Reg和Imm位置固定 • B/J-type的立即数域? – op码与类型绑定 • 寻址方式:4种 – 本质:Imm,Reg,Base – 指令寻址方式 • PC相对寻址:beq,jal • 间接跳转:jalr x0,100(x1) 图2-17 图2-19

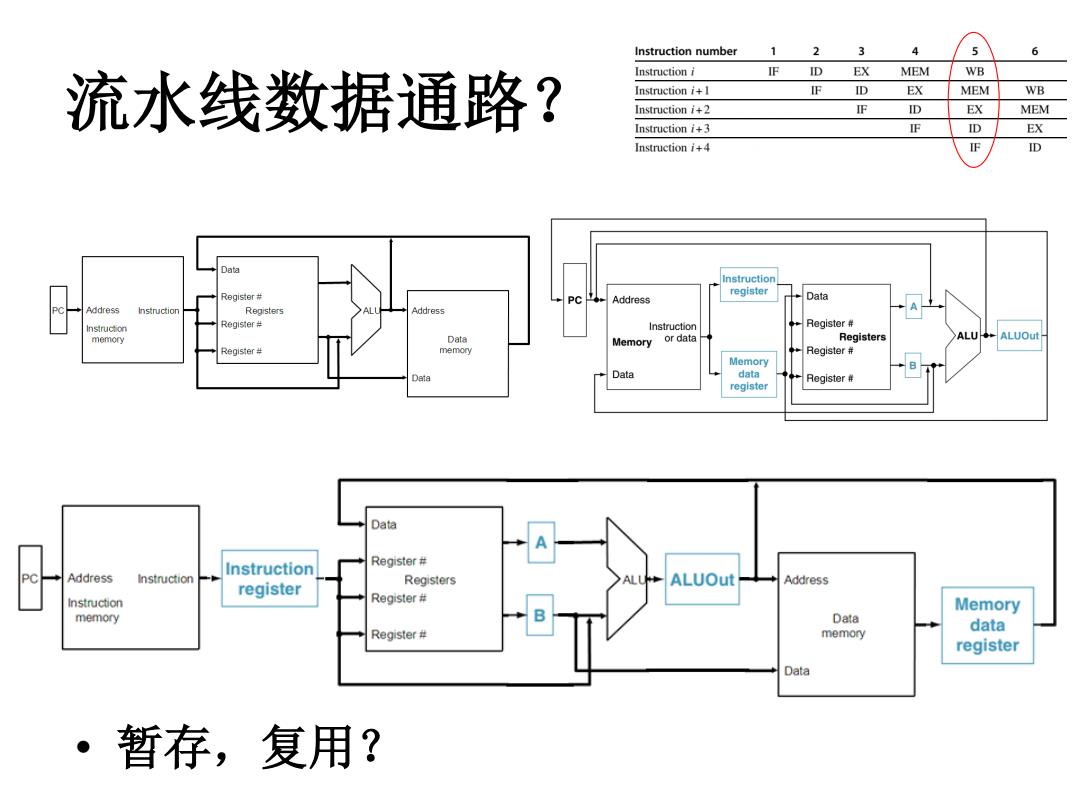

Instruction number 2 3 4 5 6 Instruction i F ID EX MEM WB 流水线数据通路? Instruction i+1 F D EX MEM WB Instruction i+2 F ID EX MEM Instruction i+3 公 ID EX Instruction i+4 F D Da妇 Instruction Register# register PC Address Data Address Registers Address Instruction Register Data ALU ALUOut- memory memory Memory or data Registers Register Memory Data d33 Register register Data Register PC Address Instruction Instruction Registers ALUOut Address register Instruction Register Memory memory Data data Register# memory register Data 暂存,复用?

流水线数据通路? • 暂存,复用?

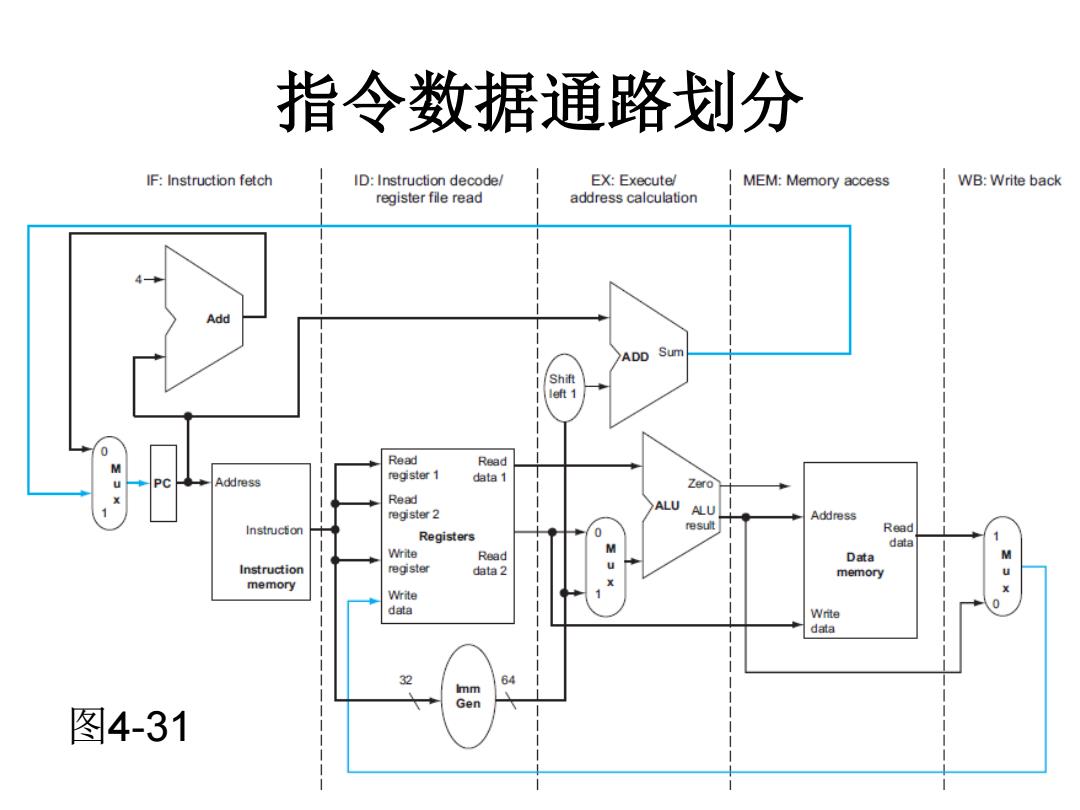

指令数据通路划分 IF:Instruction fetch ID:Instruction decode/ EX:Execute/ MEM:Memory access WB:Write back register file read address calculation Add ADD Sum Sh准 left 1 0 Read M Read PC Address register 1 d归ta1 Zero Read ALU register 2 ALU Ad划ess Instructon re sult Read Registers Write Read M data Data M Instruction register data 2 memory u memory Write data Write data 32 64 imm Gen 图4-31

11 指令数据通路划分 图4-31