计算机组成原理 第二章“指令系统” 中科大11系 李曦

计算机组成原理 第二章“指令系统” 中科大11系 李曦

概要 ·指令系统:机器指令的集合 David Patterson,Andrew Waterman, The RISC-V Reader:An Open 一“程序控制” Architecture Atlas,2017 ·程序=顺序执行的指令流 一 机器语言,汇编语言(Assemble Language) Instruction Set Architecture (ISA) ·分类:CISC、RISC、VLIW David Patterson Andrew Waterman ·影响:处理器、C编译器、OS。。。 ·本章的内容 RISC-V RV指令系统 ·操作数:寄存器,存储器 (大小尾端,对齐),常数/立即数: ·指令功能,指令格式与编码,寻址方式(操作数,下一条指令) ·分支指令$2.7,大立即数处理2.10 ·过程调用$2.8,$2.13 ·汇编程序设计:COD4附录B -指令系统特征 一 编译过程:$2.12 ·可执行程序生成:编译,汇编,链接,加载 llxx@ustc.edu.cn 2/41

llxx@ustc.edu.cn 2/41 概要 • 指令系统:机器指令的集合 – “程序控制” • 程序=顺序执行的指令流 – 机器语言,汇编语言(Assemble Language) – Instruction Set Architecture(ISA) • 分类:CISC、RISC、VLIW • 影响:处理器、C编译器、OS。。。 • 本章的内容 – RV指令系统 • 操作数:寄存器,存储器(大小尾端,对齐),常数/立即数; • 指令功能,指令格式与编码,寻址方式(操作数,下一条指令) • 分支指令$2.7,大立即数处理$2.10 • 过程调用$2.8,$2.13 • 汇编程序设计:COD4附录B – 指令系统特征 – 编译过程:$2.12 • 可执行程序生成:编译,汇编,链接,加载 David Patterson,Andrew Waterman, The RISC-V Reader: An Open Architecture Atlas,2017

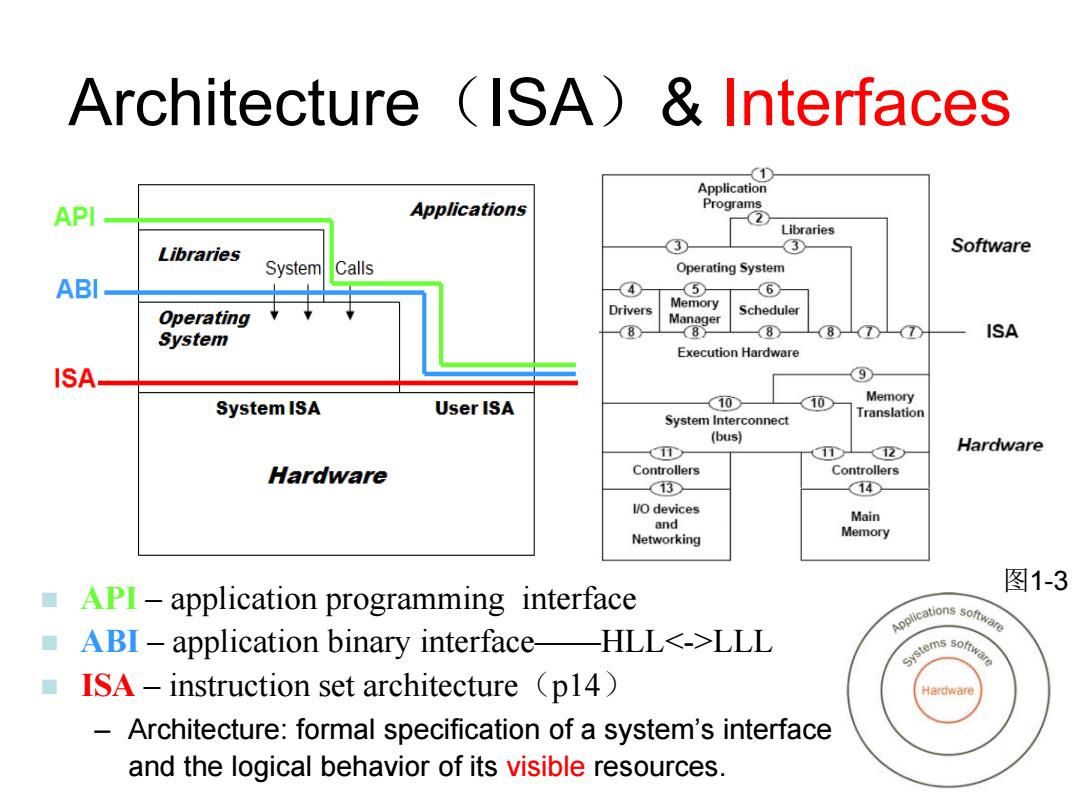

Architecture (ISA)&Interfaces (1D Application API Applications Programs 2 Libraries Libraries 3 ③ Software System Calls Operating System ABI. ④ 5 6 Operating Drivers Memory Scheduler Manager System 8 (8H 8 (8D ISA Execution Hardware ISA- (9 System ISA Memory User ISA 10 10 System Interconnect Translation (bus) T 12 Hardware Hardware Controllers Controllers 13 14 1/O devices and Main Networking Memory API-application programming i 图1-3 interface ppucat⊙ns software ■ ABI-application binary interface-HLLLLL 马 ISA-instruction set architecture (p14) Hardware -Architecture:formal specification of a system's interface and the logical behavior of its visible resources

Architecture(ISA)& Interfaces ◼ API – application programming interface ◼ ABI – application binary interface——HLLLLL ◼ ISA – instruction set architecture(p14) – Architecture: formal specification of a system’s interface and the logical behavior of its visible resources. 图1-3

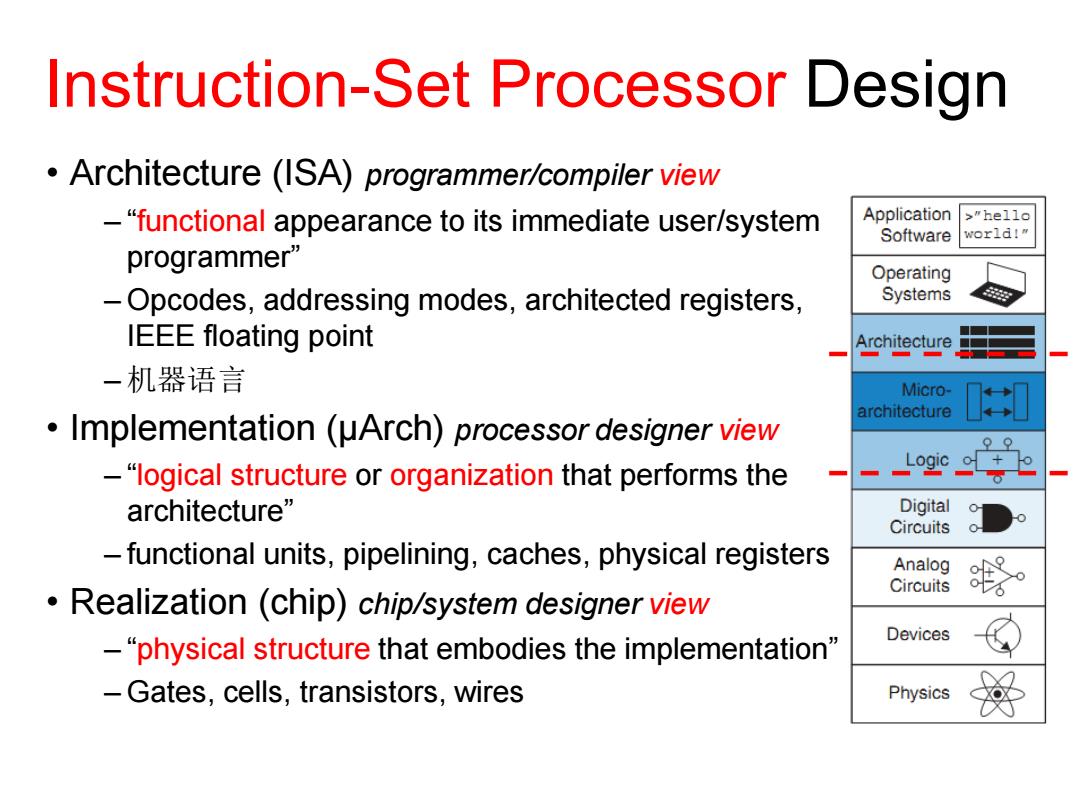

Instruction-Set Processor Design Architecture (ISA)programmer/compiler view -"functional appearance to its immediate user/system Application >"hello Software world!" programmer" Operating -Opcodes,addressing modes,architected registers Systems IEEE floating point Architecture -机器语言 Micro- architecture Implementation (JArch)processor designer view -"logical structure or organization that performs the architecture" Digital Circuits o -functional units,pipelining,caches,physical registers Analog Circuits Realization (chip)chip/system designer view Devices -"physical structure that embodies the implementation' -Gates,cells,transistors,wires Physics

Instruction-Set Processor Design • Architecture (ISA) programmer/compiler view – “functional appearance to its immediate user/system programmer” – Opcodes, addressing modes, architected registers, IEEE floating point – 机器语言 • Implementation (µArch) processor designer view – “logical structure or organization that performs the architecture” – functional units, pipelining, caches, physical registers • Realization (chip) chip/system designer view – “physical structure that embodies the implementation” – Gates, cells, transistors, wires

体系结构的8种属性 ,数据表示 -硬件能直接辨识和操作的数据类型和格式 寻址方式 一最小可寻址单位、寻址方式的种类、地址运算 寄存器组织 操作寄存器、变址寄存器、控制寄存器及专用寄存器的定义、数量和使用 规则 ·指令系统 -机器指令的操作类型、格式、指令间排序和控制机构 存储系统 -最小编址单位、编址方式、主存容量、最大可编址空间 输入输出 输入输出的连接方式、处理机山存储器与输入输出设备间的数据交换方式、 数据交换过程的控制 ● 中断机构 中断类型、中断级别,以及中断响应方式等 ·信息保护 一信息保护方式、硬件信息保护机制

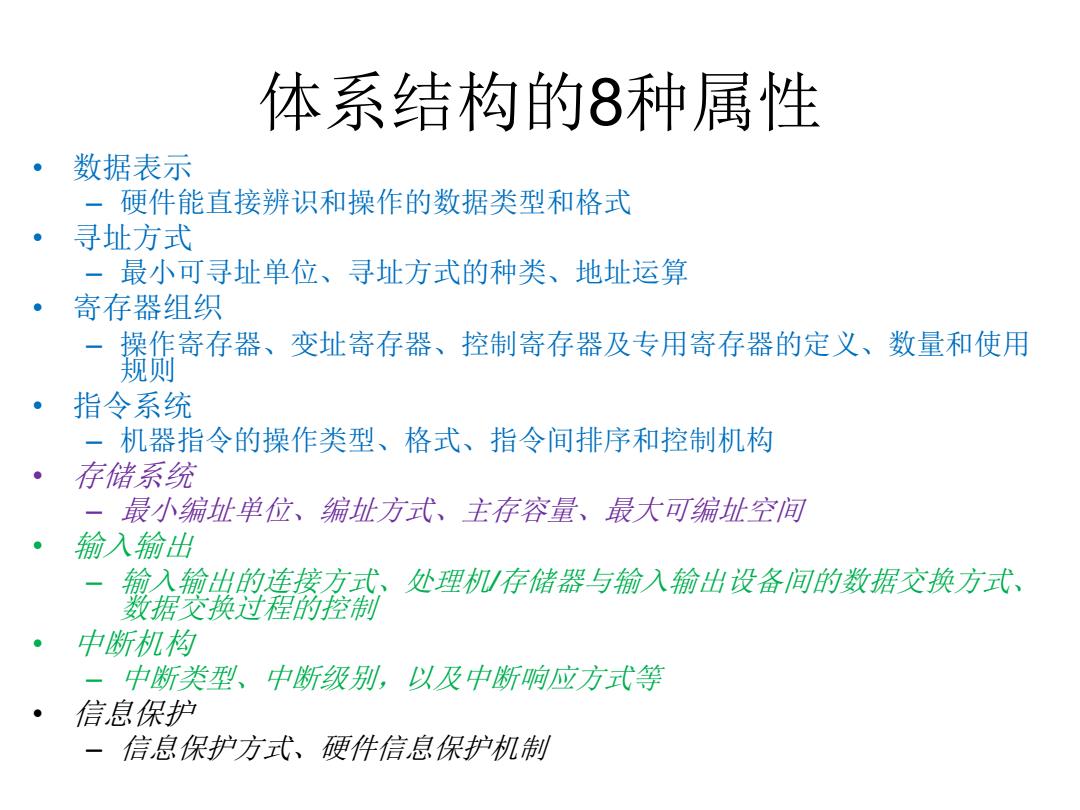

体系结构的8种属性 • 数据表示 – 硬件能直接辨识和操作的数据类型和格式 • 寻址方式 – 最小可寻址单位、寻址方式的种类、地址运算 • 寄存器组织 – 操作寄存器、变址寄存器、控制寄存器及专用寄存器的定义、数量和使用 规则 • 指令系统 – 机器指令的操作类型、格式、指令间排序和控制机构 • 存储系统 – 最小编址单位、编址方式、主存容量、最大可编址空间 • 输入输出 – 输入输出的连接方式、处理机/存储器与输入输出设备间的数据交换方式、 数据交换过程的控制 • 中断机构 – 中断类型、中断级别,以及中断响应方式等 • 信息保护 – 信息保护方式、硬件信息保护机制

操作数(opr) ·操作数类型:进制,编码,立即数(补码) 一地址:无符号整数。寄存器、内存、/O端口D 一数值:常数、定点数(有符号/无符号)、浮点数、逻辑值 -字符:ASCl、汉字内码 。 字长:“RV321”32位, “RV64”一64位(“大立即数”) 字节 100 半字:2B 8 80 字:4B 60 双字:8B(大立即数) 40 物理操作数:存放位置 20 寄存器 0 主存 /O端口 Video Image Graphics Audio Speech Security Decode Encode Average Media type 外存? Floating-point ■Pointers ■Word■Half-word■Byte 6/41

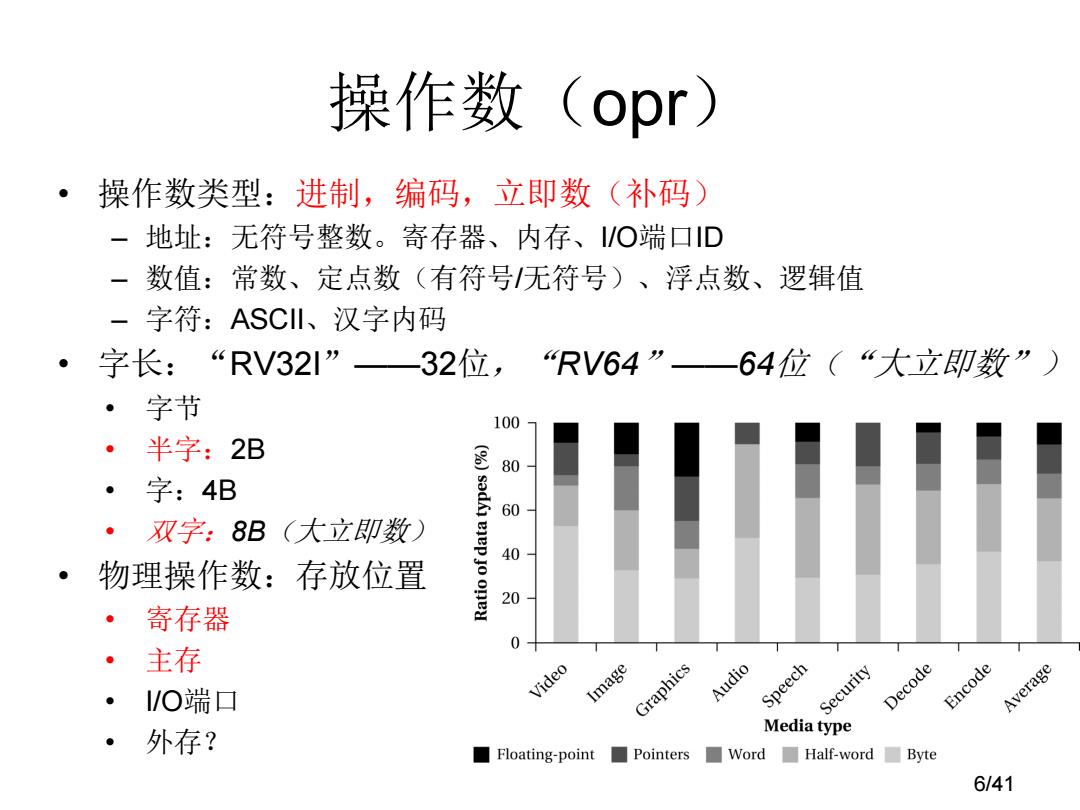

6/41 操作数(opr) • 操作数类型:进制,编码,立即数(补码) – 地址:无符号整数。寄存器、内存、I/O端口ID – 数值:常数、定点数(有符号/无符号)、浮点数、逻辑值 – 字符:ASCII、汉字内码 • 字长:“RV32I”——32位,“RV64”——64位(“大立即数”) • 字节 • 半字:2B • 字:4B • 双字:8B(大立即数) • 物理操作数:存放位置 • 寄存器 • 主存 • I/O端口 • 外存?

指令字中的操作数 寄存器 Ripes 存储器 File Help 一内存地址 着G〈〉o1oos日》四田 698 字长:Sw 01 Source code Executable code Viev node:O Binary O Disassenbled Editor 1 main: 2 addi x2,x0,2 00000000: 3addi×3,x0,3 0: 00200113 addi x2 x0 2IF ·立即数 目 4 addi x7,x3,-6 4: 00300193 addi x3 x0 3 5 8: ffa18393 addi x7 x3-6 一进制表示 6 j end c: 0080086f jal x0 0x14 : 十六进制 10sWx2,45(x0) 14: 022026a3 sW×245(x0) -0x12345 11 beq x7,x5,main 18: fe5384e3 beq x7 x5 -24 <r ·二进制 -0b1101 ·标号/行号 -main,end

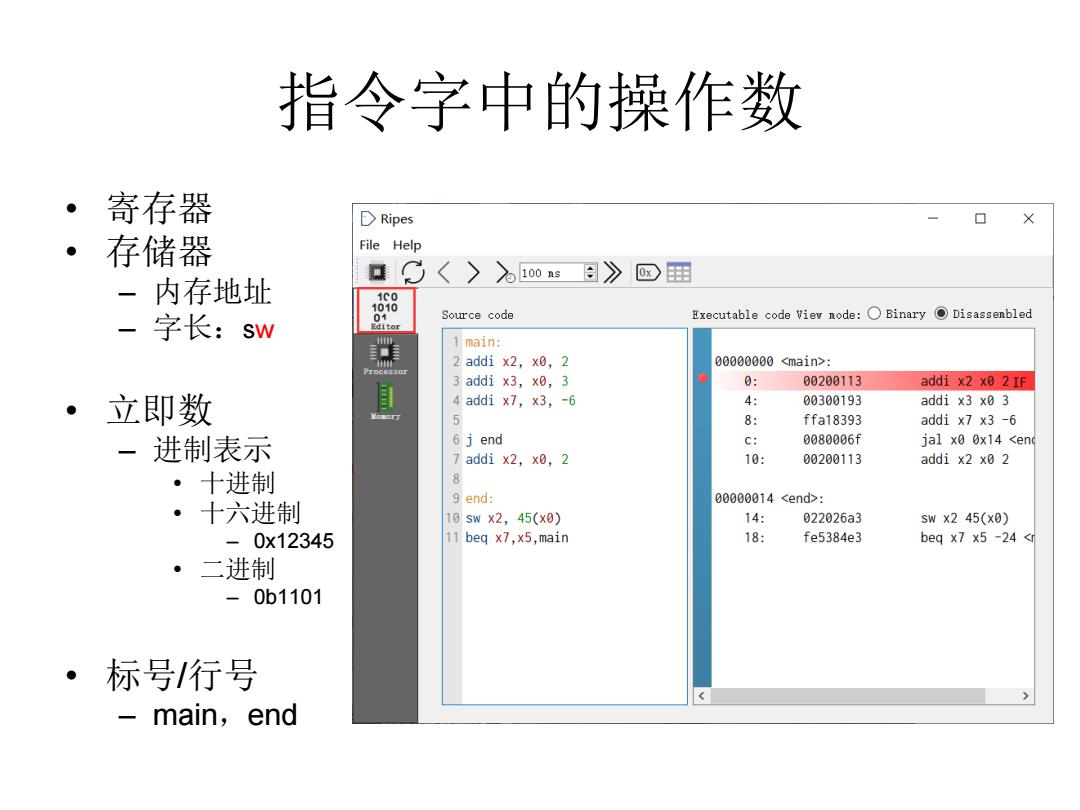

指令字中的操作数 • 寄存器 • 存储器 – 内存地址 – 字长:sw • 立即数 – 进制表示 • 十进制 • 十六进制 – 0x12345 • 二进制 – 0b1101 • 标号/行号 – main,end

RV architected registers:RV64/RV32.2-14 Name Register Preserved Usage number on call? x0 0 The constant value O n.a. x1 (ra) 1 Return address (link register) yes x2 (sp) 2 Stack pointer yes x3 (gp) 3 Globa pointer yes x4 (tp) 4 Thread pointer yes x5-x7 5-7 Temporaries no x8-x9 8-9 Saved yes ×10-×17 10-17 Arguments/results no x18-x27 18-27 Saved yes ×28-×31 28-31 Temporaries no

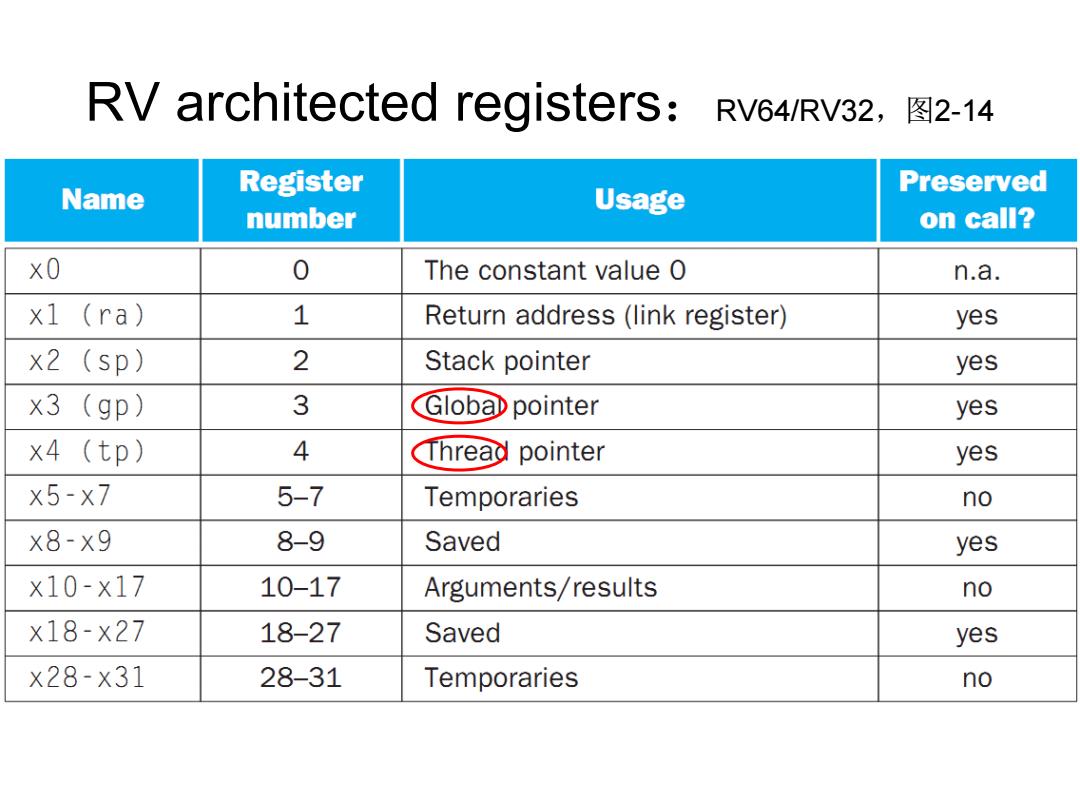

RV architected registers:RV64/RV32,图2-14

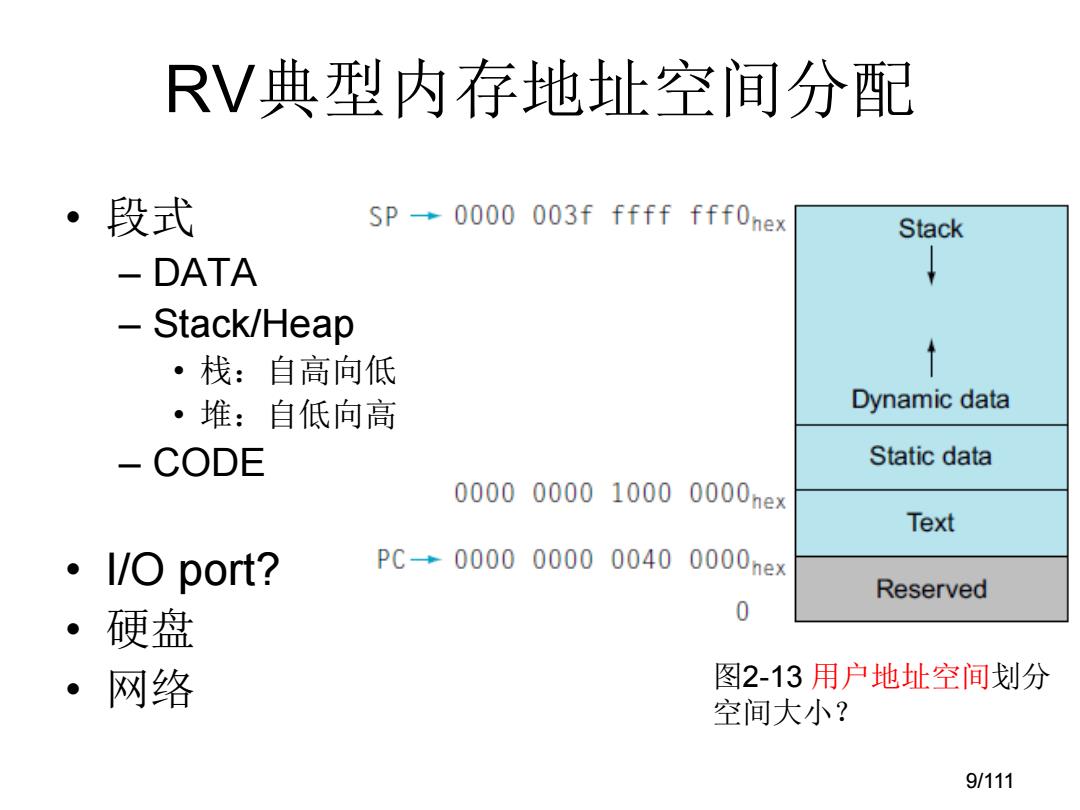

RV典型内存地址空间分配 。段式 SP -0000 003f ffff fffOnex Stack -DATA Stack/Heap ·栈:自高向低 ·堆:自低向高 Dynamic data CODE Static data 0000000010000000nex Text ·I/O port? PC+0000000000400000nex Reserved ·硬盘 0 ·网络 图2-13用户地址空间划分 空间大小? 9/111

RV典型内存地址空间分配 • 段式 – DATA – Stack/Heap • 栈:自高向低 • 堆:自低向高 – CODE • I/O port? • 硬盘 • 网络 9/111 图2-13 用户地址空间划分 空间大小?

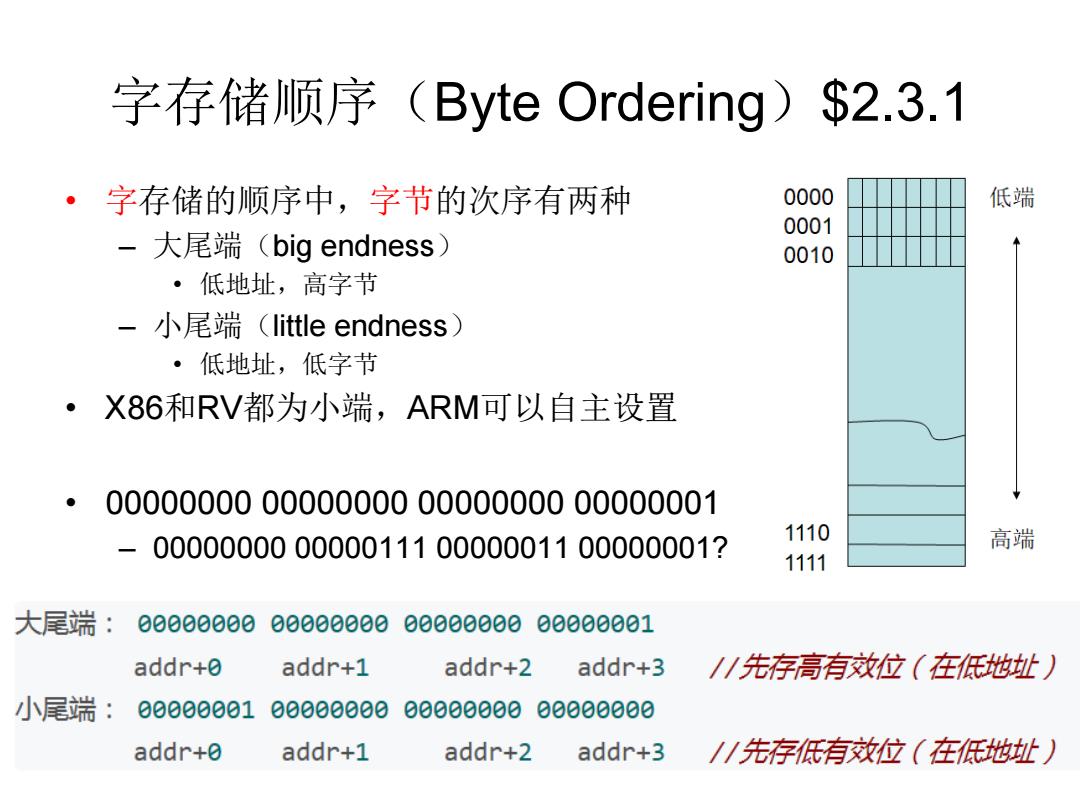

字存储顺序(Byte Ordering)$2.3.1 ·字存储的顺序中,字节的次序有两种 0000 低端 0001 -大尾端(big endness) 0010 ·低地址,高字节 -小尾端(little endness) ·低地址,低字节 ·X86和RV都为小端,ARM可以自主设置 ·00000000000000000000000000000001 00000000000001110000001100000001? 1110 高端 1111 大尾端:a00000000008800008000e0088008801 addr+0 addr+1 addr+2 addr+3 /1先存高有效位(在低地址) 小尾端:008000018008880888000800080e8080 addr+0 addr+1 addr+2 addr+3 /1先存低有效位(在低地址】

字存储顺序(Byte Ordering)$2.3.1 • 字存储的顺序中,字节的次序有两种 – 大尾端(big endness) • 低地址,高字节 – 小尾端(little endness) • 低地址,低字节 • X86和RV都为小端,ARM可以自主设置 • 00000000 00000000 00000000 00000001 – 00000000 00000111 00000011 00000001?