数字电子技术第3章组合逻辑电路 第3章组合逻辑电路 教学目标: 1.掌握组合逻辑电路的分析方法。 2.了解组合逻辑电路的设计方法。 教学重点: 分析步骤。 教学难点: 设计步骤、思路和注意事项。 一、组合逻辑电路的特点 任何时刻电路的输出只取决于该时刻的输入,而与该时刻以前的电路状态无关。 二、组合电路逻辑功能的表示方法 真值表,卡诺图,逻辑表达式,时间图(波形图) 三、组合电路分类 ①按逻辑功能不同:加法器、比较器、编码器、译码器、数据选择器和分配器、只读存储器 ②按开关元件不同:CMOS TTL ③按集成度不同:SSI MSI LSI VLSI 3.1组合电路的分析方法和设计方法 3.11组合电路的基本分析方法 组合逻辑电路的分析就是根据已知的组合逻辑电路,确定其输入与输出之间的逻辑关系,验证和 说明该电路逻辑功能的过程。即对给定的一个组合逻辑电路,确定其输入与输出之间的逻辑关系, 验证和说明该电路逻辑功能的过程。 3.2.2分析举例 【例3-1】组合电路如图3-3所示,分析该电路的逻辑功能。 例3-1电路图

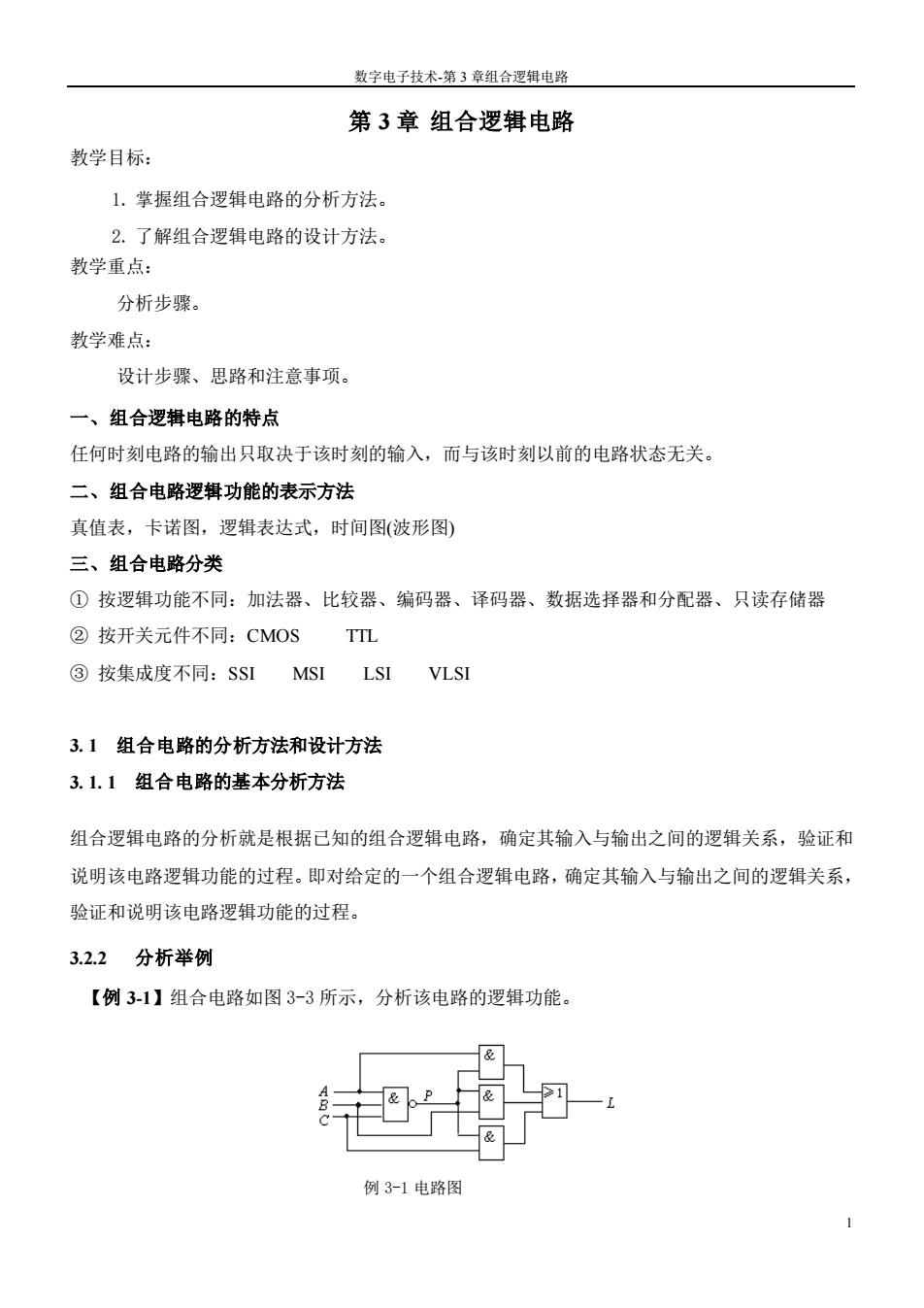

数字电子技术-第 3 章组合逻辑电路 1 第 3 章 组合逻辑电路 教学目标: 1. 掌握组合逻辑电路的分析方法。 2. 了解组合逻辑电路的设计方法。 教学重点: 分析步骤。 教学难点: 设计步骤、思路和注意事项。 一、组合逻辑电路的特点 任何时刻电路的输出只取决于该时刻的输入,而与该时刻以前的电路状态无关。 二、组合电路逻辑功能的表示方法 真值表,卡诺图,逻辑表达式,时间图(波形图) 三、组合电路分类 ① 按逻辑功能不同:加法器、比较器、编码器、译码器、数据选择器和分配器、只读存储器 ② 按开关元件不同:CMOS TTL ③ 按集成度不同:SSI MSI LSI VLSI 3. 1 组合电路的分析方法和设计方法 3. 1. 1 组合电路的基本分析方法 组合逻辑电路的分析就是根据已知的组合逻辑电路,确定其输入与输出之间的逻辑关系,验证和 说明该电路逻辑功能的过程。即对给定的一个组合逻辑电路,确定其输入与输出之间的逻辑关系, 验证和说明该电路逻辑功能的过程。 3.2.2 分析举例 【例 3-1】组合电路如图 3-3 所示,分析该电路的逻辑功能。 例 3-1 电路图

数字电子技术.第3章组合逻组电路 解:(1)由逻辑图逐级写出逻辑表达式。为了写表达式方便,借助中间变量P。 P=ABC L=AP+BP+CP=AABC BABC+CABC (2)化简与变换: L=ABC(A+B+C)=ABC+4+B+C=ABC+ABC (3)由表达式列出真值表。 (4)分析逻辑功能: 当A、BC三个变量不一致时,电路输出为“1”,所以这个电路称为“不一致电路”。 表3-1例3-1真值表 输入 输出 A B 山 0 0 0 【例3-2】组合电路如图所示,试分析其逻辑功能 例3-2逻辑图 解:(1)由逻辑图写出逻辑表达式L=ABBC·AC=AB+BC+AC (2)列真值表: 表3-2例3-2真值表 输入 输出 L

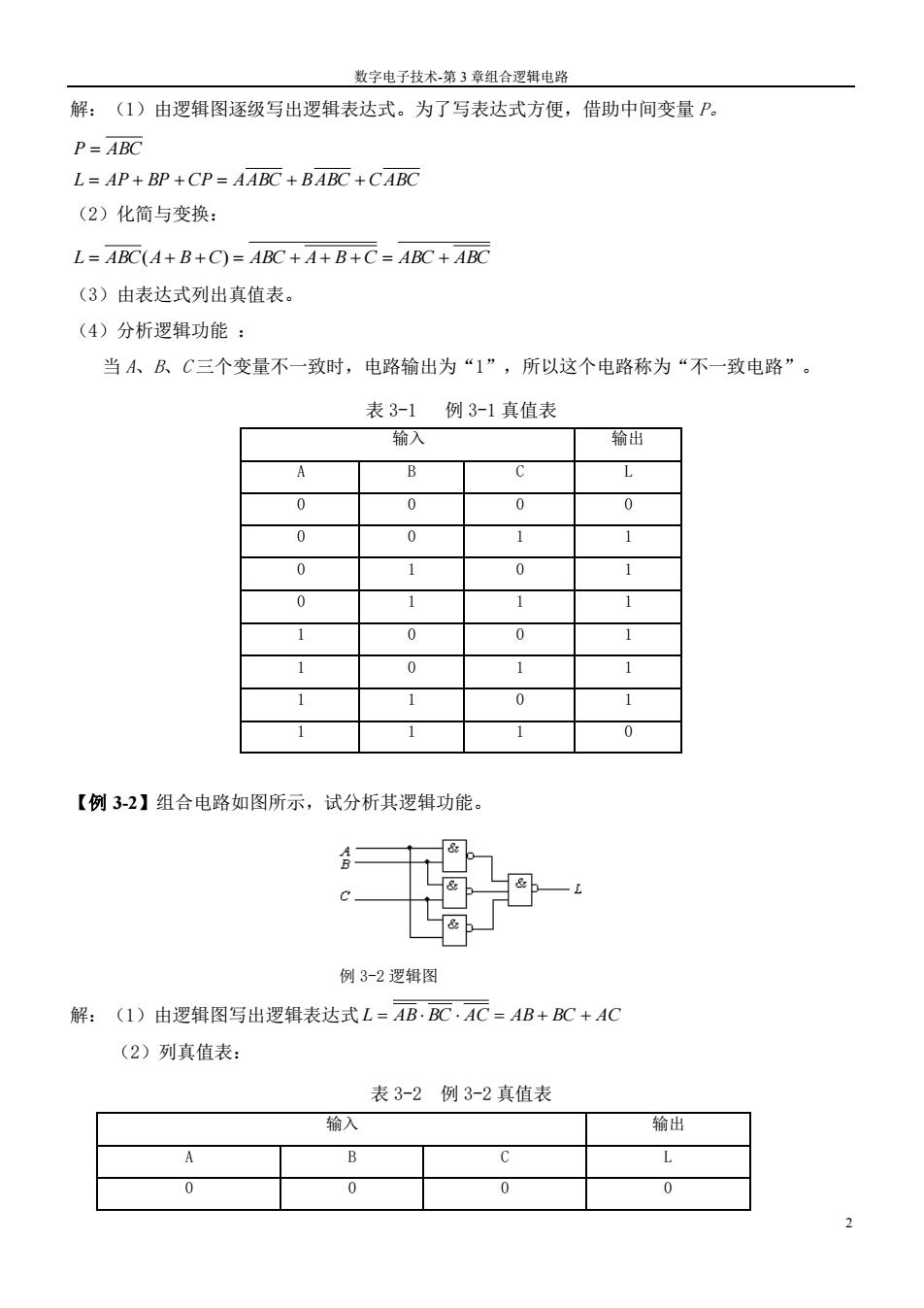

数字电子技术-第 3 章组合逻辑电路 2 解:(1)由逻辑图逐级写出逻辑表达式。为了写表达式方便,借助中间变量 P。 L AP BP CP AABC BABC CABC P ABC = + + = + + = (2)化简与变换: L = ABC(A+ B +C) = ABC + A+ B +C = ABC + ABC (3)由表达式列出真值表。 (4)分析逻辑功能 : 当 A、B、C 三个变量不一致时,电路输出为“1”,所以这个电路称为“不一致电路”。 表 3-1 例 3-1 真值表 输入 输出 A B C L 0 0 0 0 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 0 【例 3-2】组合电路如图所示,试分析其逻辑功能。 例 3-2 逻辑图 解:(1)由逻辑图写出逻辑表达式 L = AB BC AC = AB + BC + AC (2)列真值表: 表 3-2 例 3-2 真值表 输入 输出 A B C L 0 0 0 0

数字电子技术第3章组合逻辑电路 0 1 0 0 0 0 0 0 0 0 1 0 1 (3)分析逻辑可能:由表可知,若输入两个或两个以上的1(或0),输出Y为1(或0) 此电路在实际应用中可作为三人表决电路。 【例33】如图电路 例3-3电路图 解:(1)表达式 Y=ABCD+ABCD+ABCD+ABCD+ABCD+ABCD+ABCD+ABCD 已经是最简,不再化简。 (2)真值表 (3)逻辑功能 由真值表看出,四位二进制数中,1的个数为奇数时,Y=1,否则Y=0。所以,该电路为四 位检奇电路一检验四位二进制数中1的个数。 表3-3例3-3真值表 输入 输出 A D Y 0 0 0 0 0

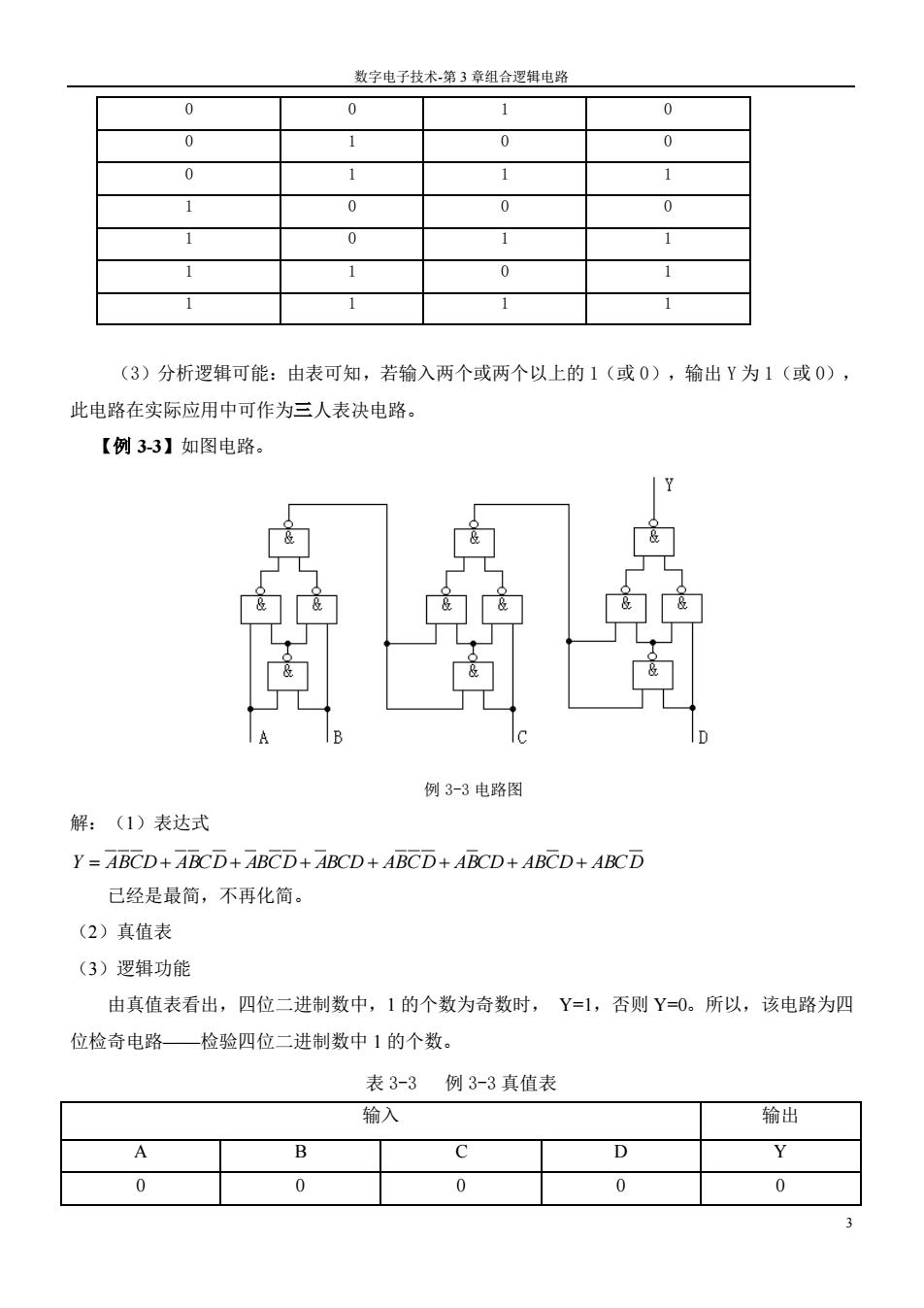

数字电子技术-第 3 章组合逻辑电路 3 0 0 1 0 0 1 0 0 0 1 1 1 1 0 0 0 1 0 1 1 1 1 0 1 1 1 1 1 (3)分析逻辑可能:由表可知,若输入两个或两个以上的 1(或 0),输出 Y 为 1(或 0), 此电路在实际应用中可作为三人表决电路。 【例 3-3】如图电路。 例 3-3 电路图 解:(1)表达式 Y = ABCD + ABCD + ABCD + ABCD + ABCD + ABCD+ ABCD + ABCD 已经是最简,不再化简。 (2)真值表 (3)逻辑功能 由真值表看出,四位二进制数中,1 的个数为奇数时, Y=1,否则 Y=0。所以,该电路为四 位检奇电路——检验四位二进制数中 1 的个数。 表 3-3 例 3-3 真值表 输入 输出 A B C D Y 0 0 0 0 0

数字电子技术.第3章组合逻组电路 0 0 0 1 0 0 0 1 0 0 1 0 0 0 0 1 0 1 0 1 0 0 1 0 0 0 1 1 1 1 1 0 0 1 1 0 0 1 0 1 0 1 0 0 1 分 0 0 1 0 1 1 1 0 1 1 1 1 1 0 例3-4:分析下图的逻辑功能 5西 (1)写出逻辑表达式 Y=-ABBM厉 B.A (②)应用逻辑代数化简 Y=A-AB.B.AB=A.AB+B.AB=A-AB+B.AB =(4+B)-AB=(4+B)-(+B)=AB+AB (3)列逻辑状态表 AB Y=AB+AB 可一 1 =A⊕B 逻辑符号 (④)分析逻辑功能:输入相同输出为“0”,输入相异输出为“1”,称为异或逻辑,电路称异或门

数字电子技术-第 3 章组合逻辑电路 4 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 0 1 0 0 1 0 1 0 1 0 0 1 1 0 0 0 1 1 1 1 1 0 0 0 1 1 0 0 1 0 1 0 1 0 0 1 0 1 1 1 1 1 0 0 0 1 1 0 1 1 1 1 1 0 1 1 1 1 1 0 例 3-4 :分析下图的逻辑功能 (2) 应用逻辑代数化简 Y = = + = + A AB B AB A AB B AB A AB B AB = + = + + = + ( ) ( ) ( ) A B AB A B A B AB AB (3) 列逻辑状态表 (4)分析逻辑功能:输入相同输出为“0”,输入相异输出为“1”,称为异或逻辑,电路称异或门。 (1) 写出逻辑表达式

数字电子技术-第3章组合逻辑电路 3.1.2组合电路的基本设计方法 根据逻辑功能要求设计 逻辑电路 设计是分析的逆过程,一般组合逻辑电路的设计就是要根据给定的逻辑问题,设计出满足要 求的最佳逻辑电路。对于同一设计对象,可以采用不同的设计思路和方法,从而得到不同的设计 结果。因此,同一功能的电路可能采用不同的器件和不同的结构来实现,最佳电路的含义因此也 各不相同。 下图给出了组合逻辑电路设计的一般过程 逻辑表达式 合理)表达式 逻辑图 组合逻辑电路设计过程 组合逻辑电路的设计一般应以电路简单、所用器件最少为目标,并尽量减少所用集成器件的 种类,因此在设计过程中要用到前面介绍的代数法和卡诺图法来化简或转换逻辑函数。 设计步骤如下: 1、按照题目要求找出输入输出的变量 2、写出真值表 3、由真值表写出函数表达式 4、化简 例:用与非门设计一个表决电路,要求输出信号的电平与三个输入信号中的多数电平一致。 练习:二进制码变格雷码。 3.2加法器和数值比较器 教学目标: 3.掌握组合逻辑电路的分析方法。 4.了解组合逻辑电路的设计方法。 教学重点: 分析步骤。 教学难点: 设计步骤、思路和注意事项

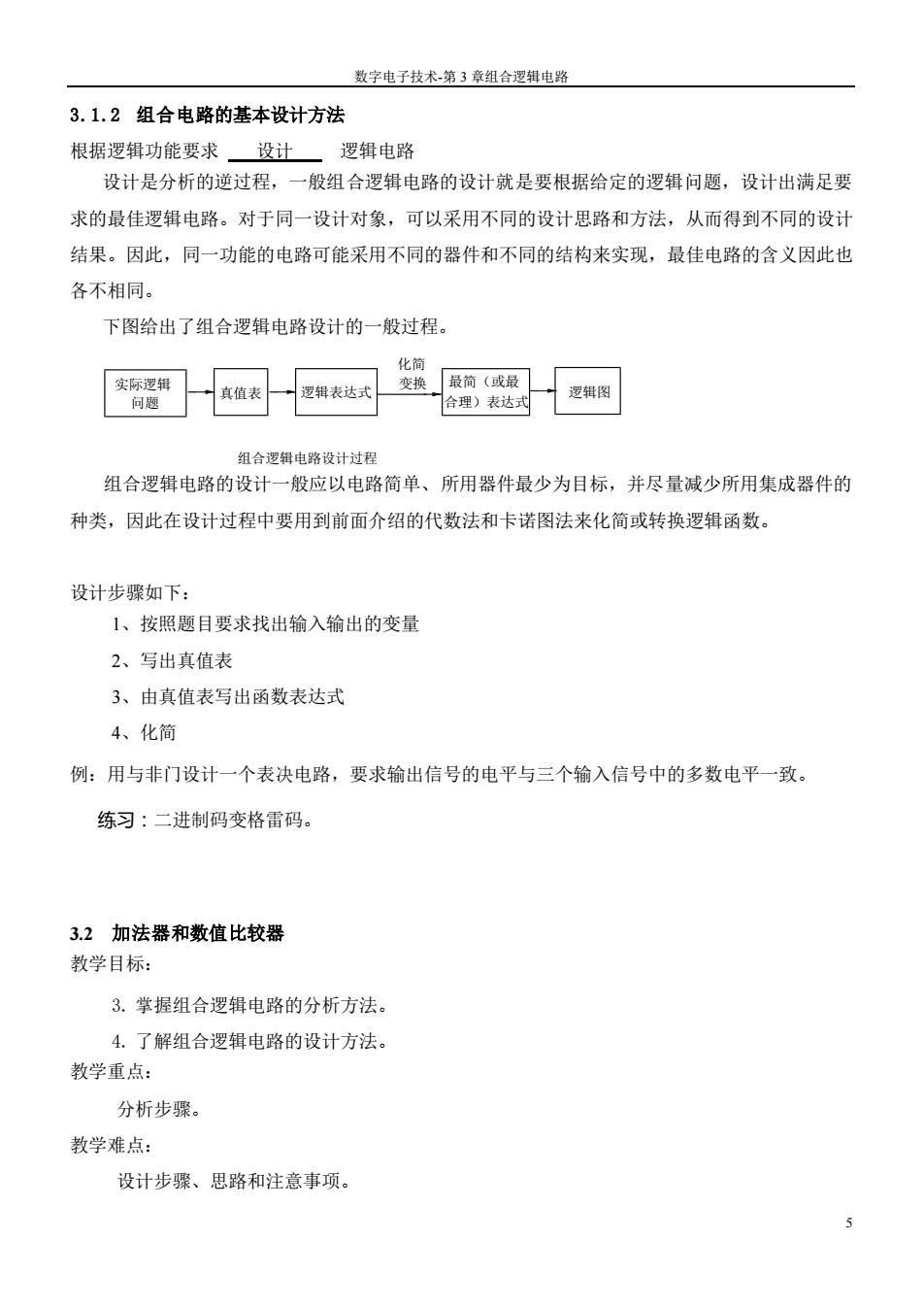

数字电子技术-第 3 章组合逻辑电路 5 3.1.2 组合电路的基本设计方法 根据逻辑功能要求 设计 逻辑电路 设计是分析的逆过程,一般组合逻辑电路的设计就是要根据给定的逻辑问题,设计出满足要 求的最佳逻辑电路。对于同一设计对象,可以采用不同的设计思路和方法,从而得到不同的设计 结果。因此,同一功能的电路可能采用不同的器件和不同的结构来实现,最佳电路的含义因此也 各不相同。 下图给出了组合逻辑电路设计的一般过程。 组合逻辑电路设计过程 组合逻辑电路的设计一般应以电路简单、所用器件最少为目标,并尽量减少所用集成器件的 种类,因此在设计过程中要用到前面介绍的代数法和卡诺图法来化简或转换逻辑函数。 设计步骤如下: 1、按照题目要求找出输入输出的变量 2、写出真值表 3、由真值表写出函数表达式 4、化简 例:用与非门设计一个表决电路,要求输出信号的电平与三个输入信号中的多数电平一致。 练习:二进制码变格雷码。 3.2 加法器和数值比较器 教学目标: 3. 掌握组合逻辑电路的分析方法。 4. 了解组合逻辑电路的设计方法。 教学重点: 分析步骤。 教学难点: 设计步骤、思路和注意事项。 化简 变换 最简(或最 问题 实际逻辑 真值表 逻辑表达式 逻辑图 合理)表达式

数字电子技术.第3章组合逻辑电路 教学目标: 1、理解半加器和全加器的基本原理。 2、掌握加法器的设计方法 3、掌握数值比较器的原理和基本设计方法 教学重点: 加法器、数值比较器的原理和计方法。 教学难点: 全加器构成多位加法器。 3.2.1加法器 一、半加器和全加器 l.半加器(Half Adder): 半加器逻辑状态表 A B S C 逻辑表达式 0000 0110 S=AB+AB=A⊕B 1010 1101 C=AB 曲 逻纸图 2.全加器(Full Adder) 一一考虑来自低位的进位, ()列逻辑状态表 A B Ci-1 S:C. 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 1 1 1 1 1 1 (2)写出逻辑式

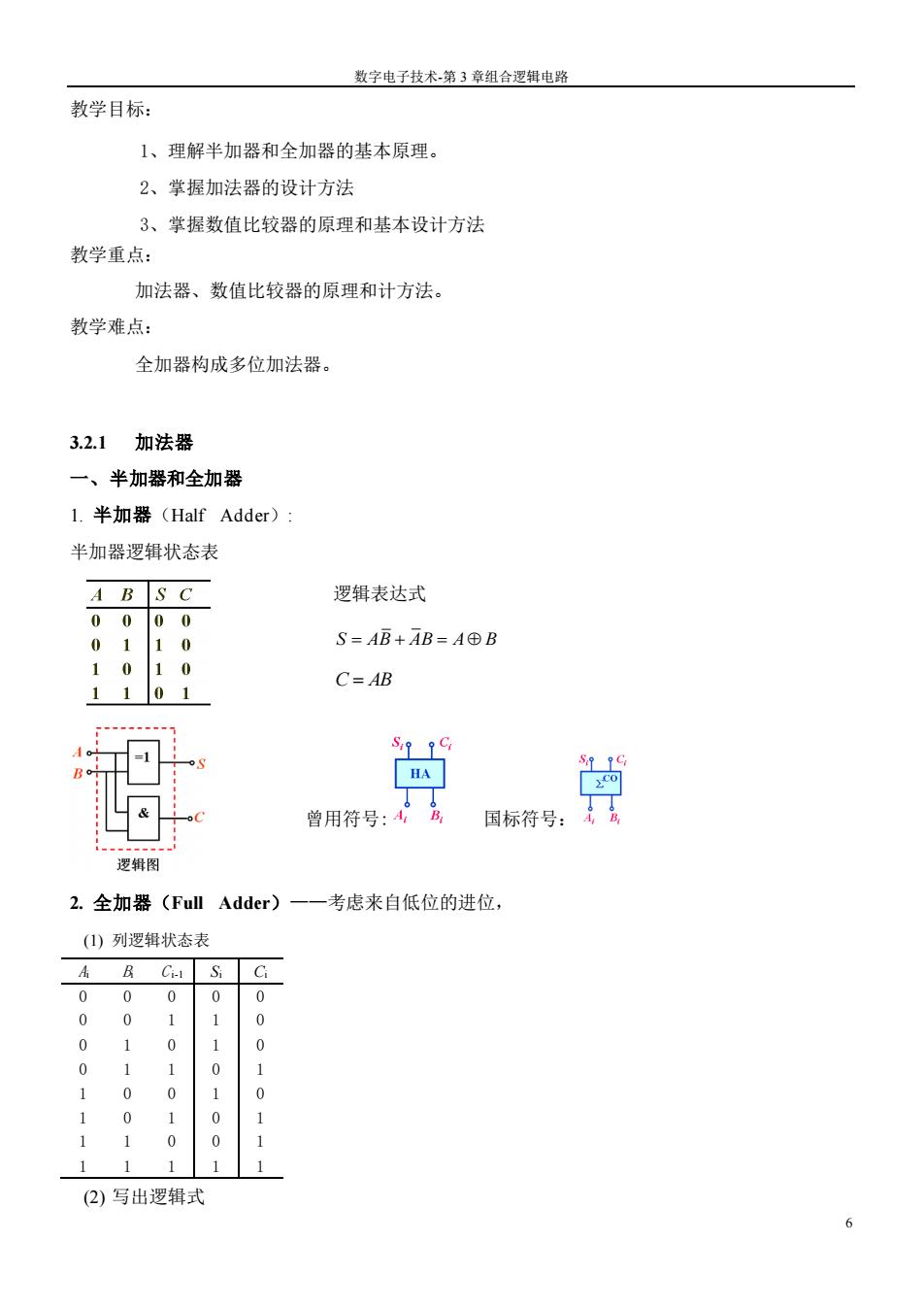

数字电子技术-第 3 章组合逻辑电路 6 教学目标: 1、理解半加器和全加器的基本原理。 2、掌握加法器的设计方法 3、掌握数值比较器的原理和基本设计方法 教学重点: 加法器、数值比较器的原理和计方法。 教学难点: 全加器构成多位加法器。 3.2.1 加法器 一、半加器和全加器 1. 半加器(Half Adder): 半加器逻辑状态表 2. 全加器(Full Adder)——考虑来自低位的进位, (1) 列逻辑状态表 Ai Bi C i-1 Si Ci 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1 (2) 写出逻辑式 逻辑表达式 S AB AB A B = + = C AB = 曾用符号: 国标符号:

数字电子技术第3章组合逻辑电路 S=4BC.+BC.+4BC+4BC C=4B+4C+B.C 用与或非门和非门实现逻辑图 FA 电电 曾用号: 国标符号: 3.集成全加器 将2个上图封装在一个器件中,就构成了双全加器。 双全加器TTL:74LS183 CMOS:C661 外引线功能端排列图P153图3.2.5 二、加法器(Adder) 1.4位串行进位加法器 2.超前进位加法器 作加法运算时,总进位信号由输入二进制数直接产生。 优点:速度快 缺点:电路比较复杂 3.2.2数值比较器(Digital Comparator) 一、1位数值比较器 L(A>B) 1位 oG(A=B) B:0 比较器 °M(A<B) 二、4位数值比较器 真值表 7

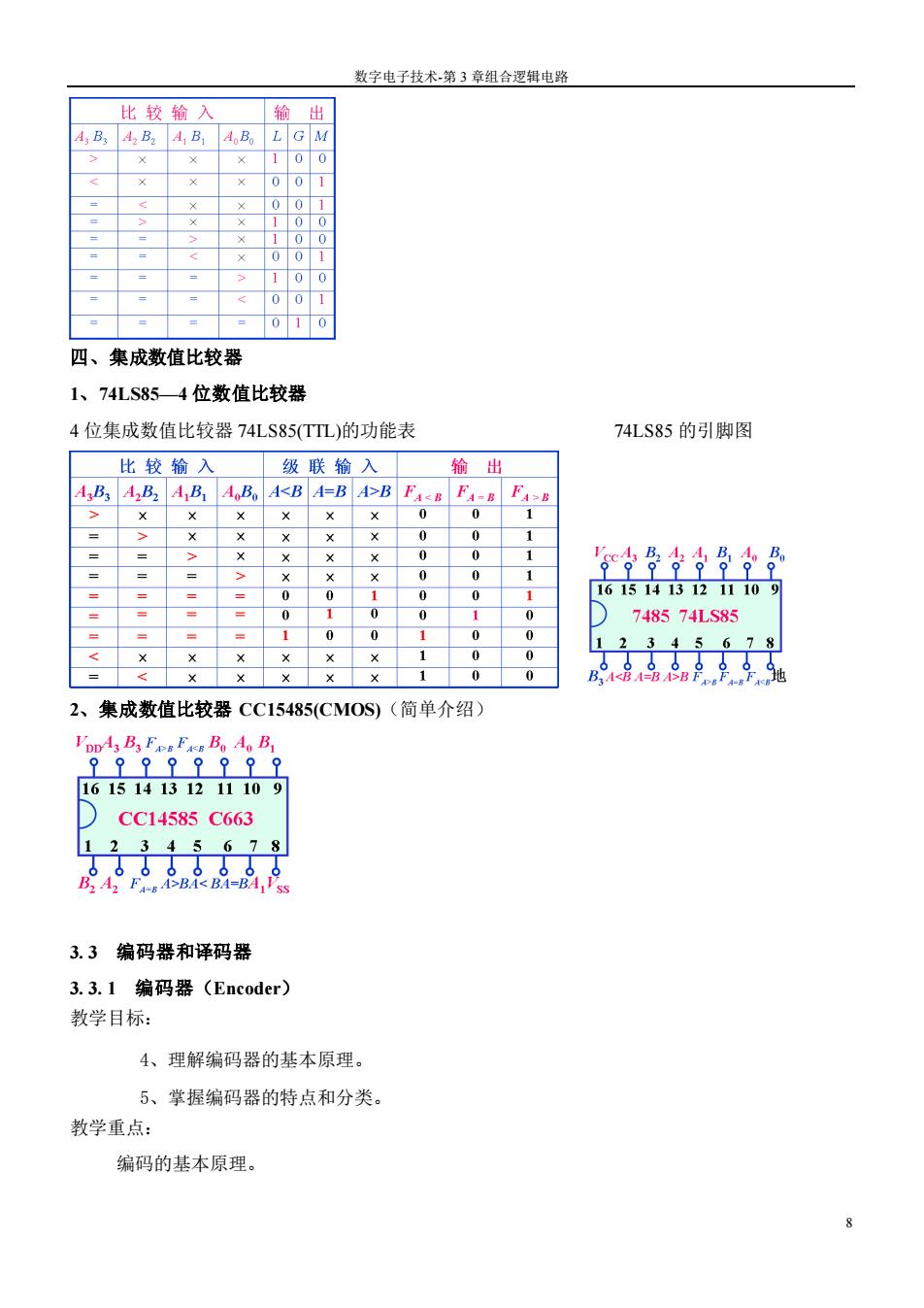

数字电子技术-第 3 章组合逻辑电路 7 i i i i i i i i i i i i i 1 1 1 1 S ABC ABC ABC ABC = + + + − − − − C A B AC B C i i i i i i i = + + − − 1 1 用与或非门和非门实现逻辑图 3. 集成全加器 将 2 个上图封装在一个器件中,就构成了双全加器。 双全加器 TTL:74LS183 CMOS:C661 外引线功能端排列图 P153 图 3.2.5 二、加法器(Adder) 1. 4 位串行进位加法器 2. 超前进位加法器 作加法运算时,总进位信号由输入二进制数直接产生。 优点:速度快 缺点:电路比较复杂 3. 2. 2 数值比较器(Digital Comparator) 一、1 位数值比较器 二、4 位数值比较器 真值表 曾用符号: 国标符号:

数字电子技术第3章组合逻辑电路 比较输入 输出 4B4B24B,AB。LGM 01 010 四、集成数值比较器 1、74LS854位数值比较器 4位集成数值比较器74LS85TL)的功能表 74LS85的引脚图 比较输入 级联输入 输出 AB 4Bs AB.AB A<B A-B AB F-a Fa "g受令台8令品 16151413121110可 748574L585 0 12345678 1 0 <×100 2、集成数值比较器CC15485(CMOS)(简单介绍) 'DDA3B3 Fes F&B。AoB 99999999 161514131211109 DCC14585C663 12345678 8n品品品 B:A F 3.3编码器和译码器 3.3.1编码器(Encoder) 教学目标: 4、理解编码器的基本原理。 5、掌握编码器的特点和分类。 教学重点: 编码的基本原理

数字电子技术-第 3 章组合逻辑电路 8 四、集成数值比较器 1、74LS85—4 位数值比较器 4 位集成数值比较器 74LS85(TTL)的功能表 74LS85 的引脚图 2、集成数值比较器 CC15485(CMOS)(简单介绍) 3. 3 编码器和译码器 3. 3. 1 编码器(Encoder) 教学目标: 4、理解编码器的基本原理。 5、掌握编码器的特点和分类。 教学重点: 编码的基本原理

数字电子技术第3章组合逻辑电路 教学难点: 电路功能。特别是编码器的分类。 概念:编码一一将特定含义的输入信号(文字、数字、符号)转换成二进制代码的过程.能够 实现编码功能的数字电路称为编码器。 编码器:完成编码工作的数字电路(二进制数码组和信息的对应) 二进制编码器一将输入信号编成二进制代码的电路。 高低电平信号 进制代码 1、4线一2线普通编码器 2、3位二进制编码器(普通8线-3线编码器) 任何时候只允许一个输入信号为有效电平,即只能有一个信号请求编码 图3-6三位二进制编码器结构图 输入是8个需要编码的信号(互相排斥),分别用1o、10、h表示:输出是3位二进制编 码,分别用Y2、Y1、Yo表示。其中,0、1o、.、h是一组互相排斥的变量, 其简化编码真值表 如下 表3-4三位二进制编码器简化真值表 输出 输入 Y2 Y Yo 0 0 0 12 0 0 4 0 0 15 0 17

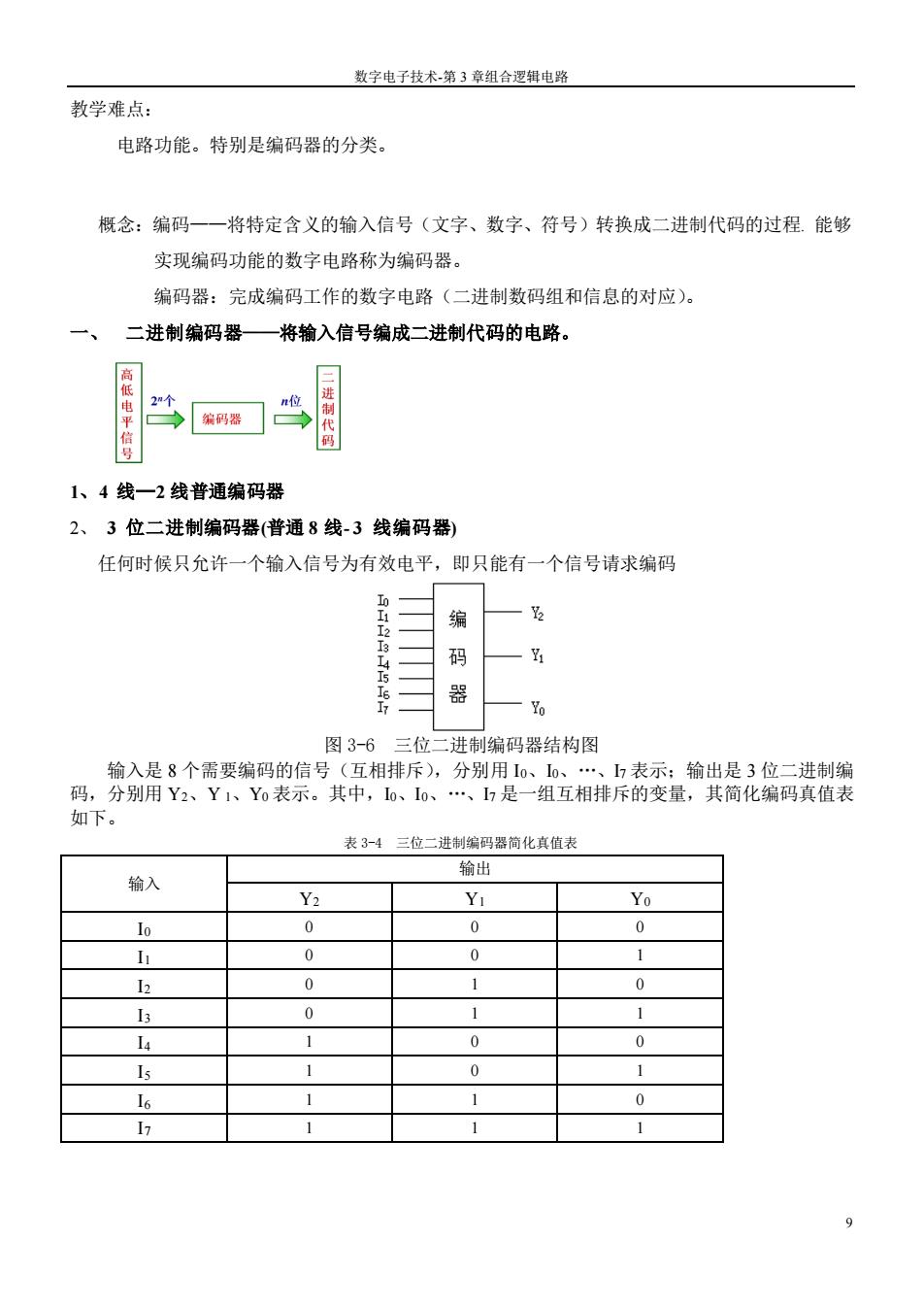

数字电子技术-第 3 章组合逻辑电路 9 教学难点: 电路功能。特别是编码器的分类。 概念:编码——将特定含义的输入信号(文字、数字、符号)转换成二进制代码的过程. 能够 实现编码功能的数字电路称为编码器。 编码器:完成编码工作的数字电路(二进制数码组和信息的对应)。 一、 二进制编码器——将输入信号编成二进制代码的电路。 1、4 线─2 线普通编码器 2、 3 位二进制编码器(普通 8 线- 3 线编码器) 任何时候只允许一个输入信号为有效电平,即只能有一个信号请求编码 图 3-6 三位二进制编码器结构图 输入是 8 个需要编码的信号(互相排斥),分别用 I0、I0、.、I7 表示;输出是 3 位二进制编 码,分别用 Y2、Y 1、Y0 表示。其中,I0、I0、.、I7 是一组互相排斥的变量,其简化编码真值表 如下。 表 3-4 三位二进制编码器简化真值表 输入 输出 Y2 Y1 Y0 I0 0 0 0 I1 0 0 1 I2 0 1 0 I3 0 1 1 I4 1 0 0 I5 1 0 1 I6 1 1 0 I7 1 1 1

数字电子技术第3章组合逻辑电路 逻辑式为: Y2=14+L3+16+17 y=12+13+1。+1 Y%=1+13+I+I 进一步得到逻辑图,属或门阵列。 用与非门实现,输入采用非变量形式: y2=+1+1。+1=1,1 Y=2+13+1。+1-2131.1 。=+1+1+万=131,万 元。 图3-7三位二进制编码器逻辑图 3、3位二进制优先编码器 当有两个及以上的信号同时请求编码,电路只能对其中一个优先级别高的信号进行编码。 优先编码器一一允许同时输入两个以上的编码信号,编码器给所有的输入信号规定了优先顺 序,当多个输入信号同时出现时,只对其中优先级最高的一个进行编码。 需编码的8个输入信号10、10、允许有多个同时输入,但电路只对优先级别最高的进行 编码(优先级别可自行设定 在编码器中,设1级别最高、16次之、5再次之.、1最低。其编码真值表、逻辑式为: 表35三位二进制优先编码器真值表 输出 y=12+1l6+113+1114=1,+16+13+14 X=1+11。+111l3+116111l2=1,+16+1l3+1l Y13+1,16l5+1514山3+165141l=1,+l5+16i43+4l 10

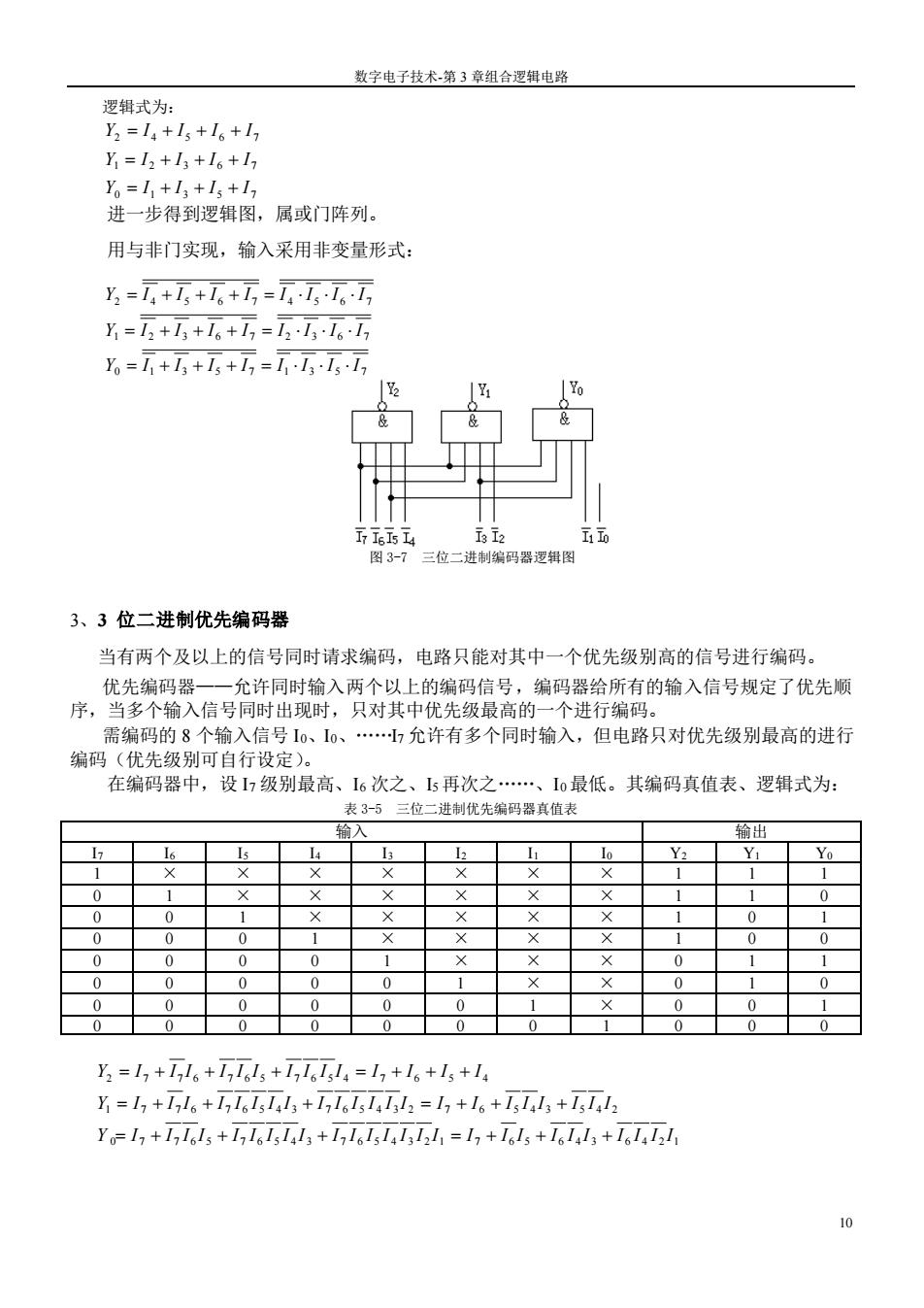

数字电子技术-第 3 章组合逻辑电路 10 逻辑式为: 0 1 3 5 7 1 2 3 6 7 2 4 5 6 7 Y I I I I Y I I I I Y I I I I = + + + = + + + = + + + 进一步得到逻辑图,属或门阵列。 用与非门实现,输入采用非变量形式: 0 1 3 5 7 1 3 5 7 1 2 3 6 7 2 3 6 7 2 4 5 6 7 4 5 6 7 Y I I I I I I I I Y I I I I I I I I Y I I I I I I I I = + + + = = + + + = = + + + = 图 3-7 三位二进制编码器逻辑图 3、3 位二进制优先编码器 当有两个及以上的信号同时请求编码,电路只能对其中一个优先级别高的信号进行编码。 优先编码器——允许同时输入两个以上的编码信号,编码器给所有的输入信号规定了优先顺 序,当多个输入信号同时出现时,只对其中优先级最高的一个进行编码。 需编码的 8 个输入信号 I0、I0、.I7 允许有多个同时输入,但电路只对优先级别最高的进行 编码(优先级别可自行设定)。 在编码器中,设 I7 级别最高、I6 次之、I5再次之.、I0最低。其编码真值表、逻辑式为: 表 3-5 三位二进制优先编码器真值表 输入 输出 I7 I6 I5 I4 I3 I2 I1 I0 Y2 Y1 Y0 1 × × × × × × × 1 1 1 0 1 × × × × × × 1 1 0 0 0 1 × × × × × 1 0 1 0 0 0 1 × × × × 1 0 0 0 0 0 0 1 × × × 0 1 1 0 0 0 0 0 1 × × 0 1 0 0 0 0 0 0 0 1 × 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0 7 7 6 5 7 6 5 4 3 7 6 5 4 3 2 1 7 6 5 6 4 3 6 4 2 1 1 7 7 6 7 6 5 4 3 7 6 5 4 3 2 7 6 5 4 3 5 4 2 2 7 7 6 7 6 5 7 6 5 4 7 6 5 4 Y I I I I I I I I I I I I I I I I I I I I I I I I I I Y I I I I I I I I I I I I I I I I I I I I I I Y I I I I I I I I I I I I I I = + + + = + + + = + + + = + + + = + + + = + + +