数字电子技术Digital Eleetronics Technolo 第十章可编程逻辑器件 名阿子大学《数字电子技术》保程组 电 活:0993-2057237 电子邮搐:rl mac@shZu,edu,cn 机电学院电气工程系 上一页下一页回目绿 退出

机电学院电气工程系 上一页 下一页 回目录 退出 第十章 可编程逻辑器件 数字电子技术Digital Electronics Technology 石河子大学《数字电子技术》课程组 电 话:0993-2057237 电子邮箱:rl_mac@shzu.edu.cn

10.1PLD的基本概念 10.2低密度PLD 10.3高密度PLD简介 10.4基于可编程逻辑器件的数字系统设计流程 机电学院电气工程系 上一页下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 10.3 高密度PLD简介 10.1 PLD的基本概念 10.2 低密度PLD 10.4 基于可编程逻辑器件的数字系统设计流程

10.1PLD的基本结构与分类 一、PLD的由来 数字集成电路就其应用而言可以分为三大类。 第一类是通用芯片。是指那些具有基本功能的数字器件,比如我们学过的 门电路、触发器、各种组合逻辑电路和时序逻辑电路等。它们可用来设计 各种各样的数字电路。 缺点:很难实现一个复杂的数字系统。 第二类是专用芯片(ASIC)。是为某种专门用途而设计,并将整个系统集 成在一个芯片上。如手机、电视机、数码相机、单片机等等,其核心都是 专用的集成芯片。 缺点:它的开发周期长、成本高,只适用于那些大批量生产的电子产品。 第三类就是可编程逻辑芯片(PLD)。它相当于一种集成的半成品芯片, 出厂时不具有特定的逻辑功能,用户可根据需要对其进行编程而赋予某种 逻辑功能,使其成为一种专用芯片。 机电学院电气工程系 上一页下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 10.1 PLD的基本结构与分类 一、PLD的由来 数字集成电路就其应用而言可以分为三大类。 第一类是通用芯片。是指那些具有基本功能的数字器件,比如我们学过的 门电路、触发器、各种组合逻辑电路和时序逻辑电路等。它们可用来设计 各种各样的数字电路。 缺点:很难实现一个复杂的数字系统。 第二类是专用芯片(ASIC)。是为某种专门用途而设计,并将整个系统集 成在一个芯片上。如手机、电视机、数码相机、单片机等等,其核心都是 专用的集成芯片。 缺点:它的开发周期长、成本高,只适用于那些大批量生产的电子产品。 第三类就是可编程逻辑芯片(PLD)。它相当于一种集成的半成品芯片, 出厂时不具有特定的逻辑功能,用户可根据需要对其进行编程而赋予某种 逻辑功能,使其成为一种专用芯片

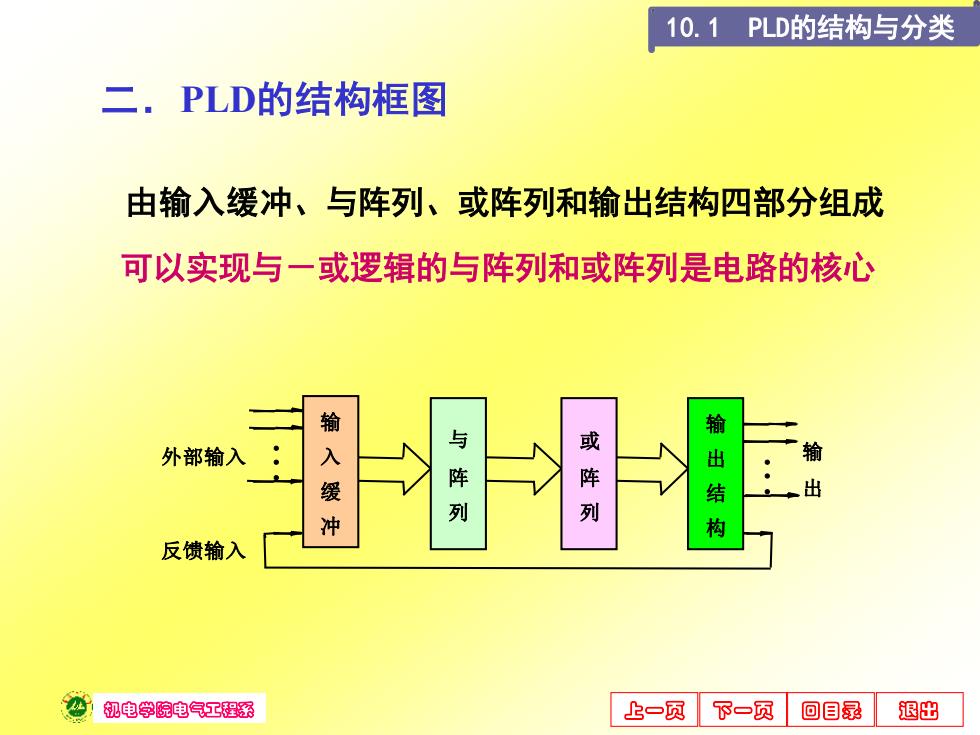

10.1 PLD的结构与分类 二.PLD的结构框图 由输入缓冲、与阵列、或阵列和输出结构四部分组成 可以实现与一或逻辑的与阵列和或阵列是电路的核心 输 输 外部输入 或阵列 出 输 缓 出 冲 列 构 反馈输入 机电学院电气工程系 上一页下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 二.PLD的结构框图 由输入缓冲、与阵列、或阵列和输出结构四部分组成 可以实现与-或逻辑的与阵列和或阵列是电路的核心 输 入 缓 冲 阵 列 与 阵 列 或 输 出 结 构 . . . 外部输入 . 出 . 输 . 反馈输入 10.1 PLD的结构与分类

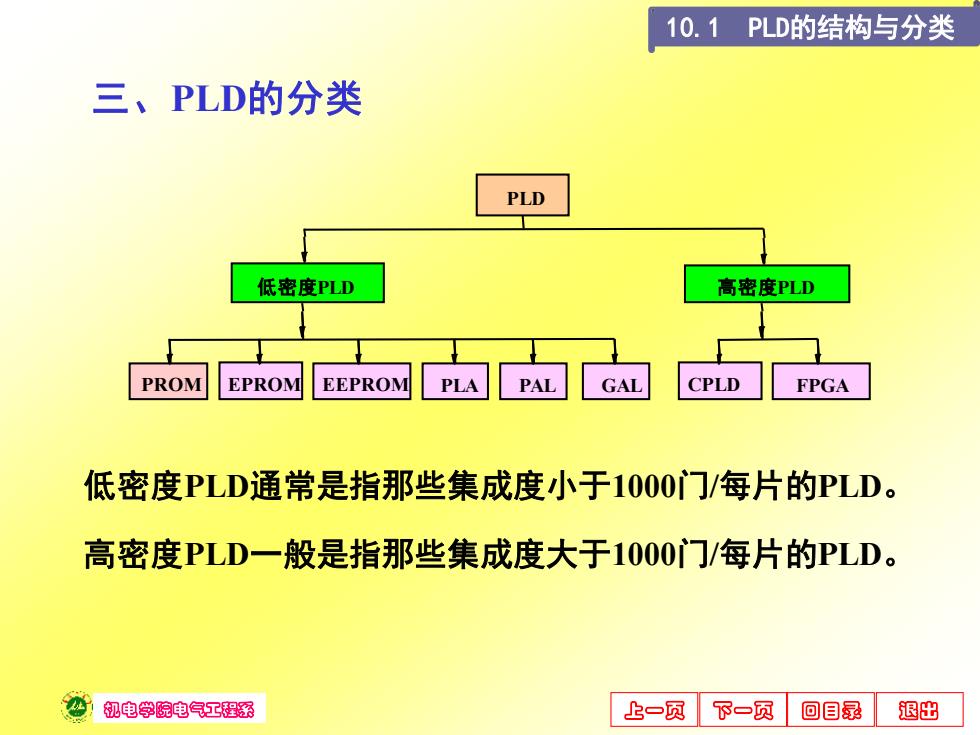

10.1PLD的结构与分类 三、PLD的分类 PLD 低密度PLD 高密度PLD PROM EPROM EEPROM PLA PAL GAL CPLD FPGA 低密度PLD通常是指那些集成度小于1000门/每片的PLD。 高密度PLD一般是指那些集成度大于1000门/每片的PLD。 机电学院电气工程系 上一页下一页回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 低密度PLD PROM EPROM EEPROM PLA PAL GAL 高密度PLD CPLD FPGA PLD 三、PLD的分类 低密度PLD通常是指那些集成度小于1000门/每片的PLD。 高密度PLD一般是指那些集成度大于1000门/每片的PLD。 10.1 PLD的结构与分类

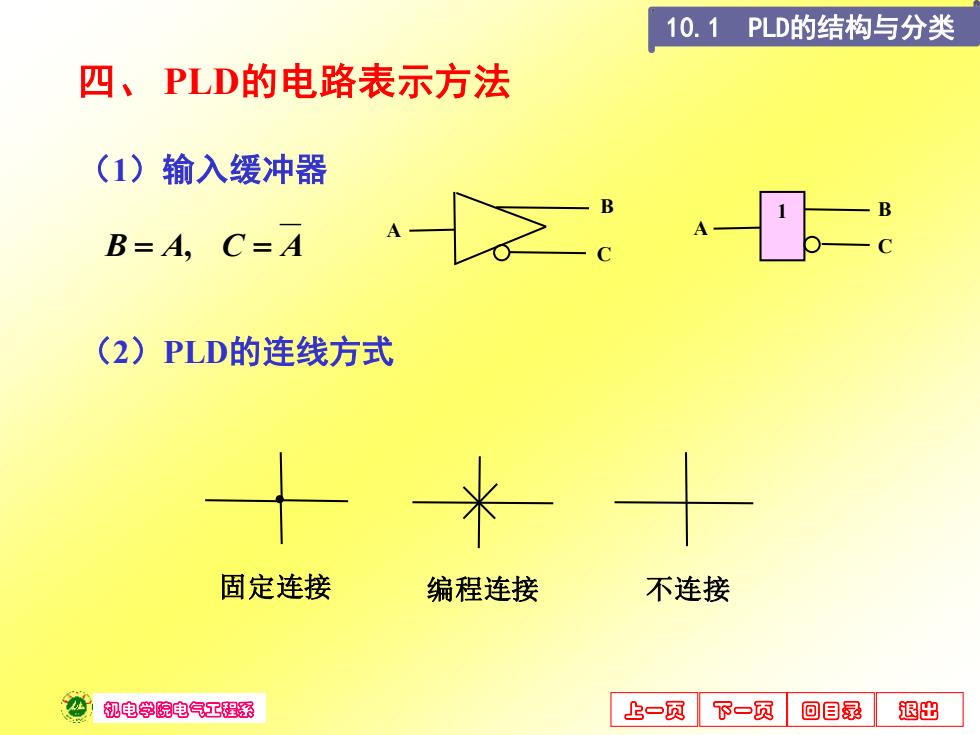

10.1 PLD的结构与分类 四、PLD的电路表示方法 (1)输入缓冲器 B=A,C=A 2D= (2)PLD的连线方式 十米 固定连接 编程连接 不连接 机电学院电气工程系 上一页下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 (1)输入缓冲器 四、 PLD的电路表示方法 B = A, C = A (2)PLD的连线方式 A C A B C 1 B 固定连接 编程连接 不连接 10.1 PLD的结构与分类

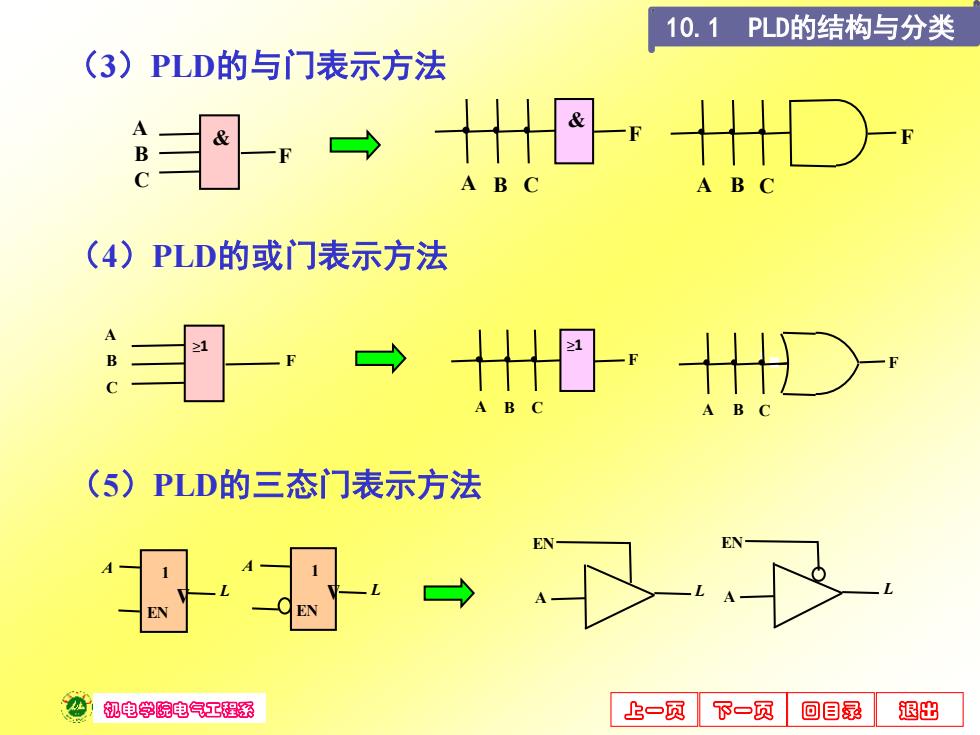

10.1PLD的结构与分类 (3)PLD的与门表示方法 3→H8H什D (4)PLD的或门表示方法 -→丹D (5)PLD的三态门表示方法 →凡 “机电学院电气工程系 上一页下一页回目暴 退出

机电学院电气工程系 上一页 下一页 回目录 退出 (3)PLD的与门表示方法 (4)PLD的或门表示方法 & A B C F & A B C A B C F F ≥1 A B C F 2 A B C ≥1 F A B C F (5)PLD的三态门表示方法 A EN L A EN Δ L L 1 EN A EN A 1 L Δ 10.1 PLD的结构与分类

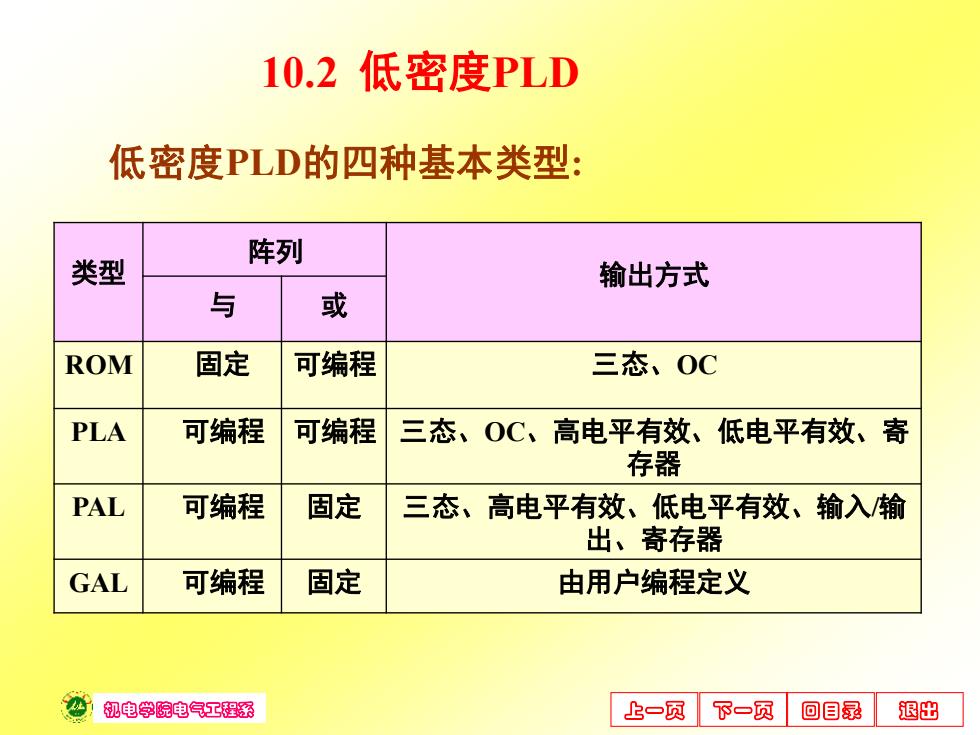

10.2低密度PLD 低密度PLD的四种基本类型: 阵列 类型 输出方式 与 或 ROM 固定 可编程 三态、OC PLA 可编程 可编程 三态、OC、高电平有效、低电平有效、寄 存器 PAL 可编程 固定 三态、高电平有效、低电平有效、输入输 出、寄存器 GAL 可编程 固定 由用户编程定义 机电学院电气工程系 上-页 下一顷 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 类型 阵列 输出方式 与 或 ROM 固定 可编程 三态、OC PLA 可编程 可编程 三态、OC、高电平有效、低电平有效、寄 存器 PAL 可编程 固定 三态、高电平有效、低电平有效、输入/输 出、寄存器 GAL 可编程 固定 由用户编程定义 低密度PLD的四种基本类型: 10.2 低密度PLD

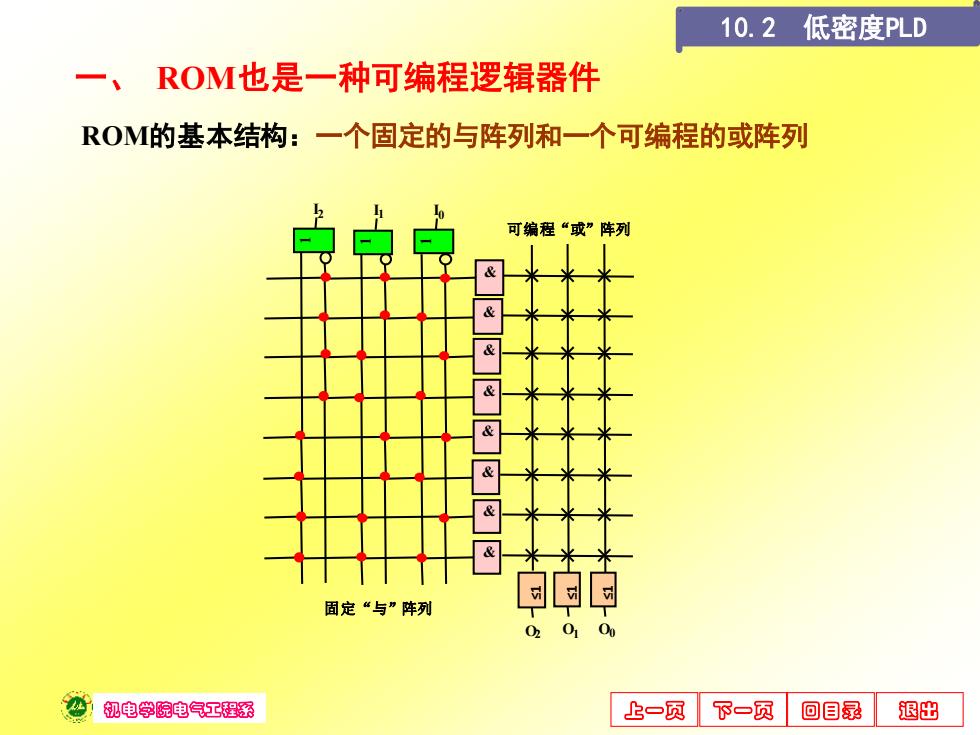

10.2 低密度PLD 一、 ROM也是一种可编程逻辑器件 ROM的基本结构:一个固定的与阵列和一个可编程的或阵列 可编程“或”阵列 && & & 固定“与”阵列 中中 020100 ,机电学院电气工系 上一页下一页回目绿 退出

机电学院电气工程系 上一页 下一页 回目录 退出 一、 ROM也是一种可编程逻辑器件 ROM的基本结构:一个固定的与阵列和一个可编程的或阵列 & & 固定“与”阵列 O2 O1 O0 ≤1 ≤1 ≤1 可编程“或”阵列 2 1 & 1 & & I & 0 I & I & 1 1 10.2 低密度PLD

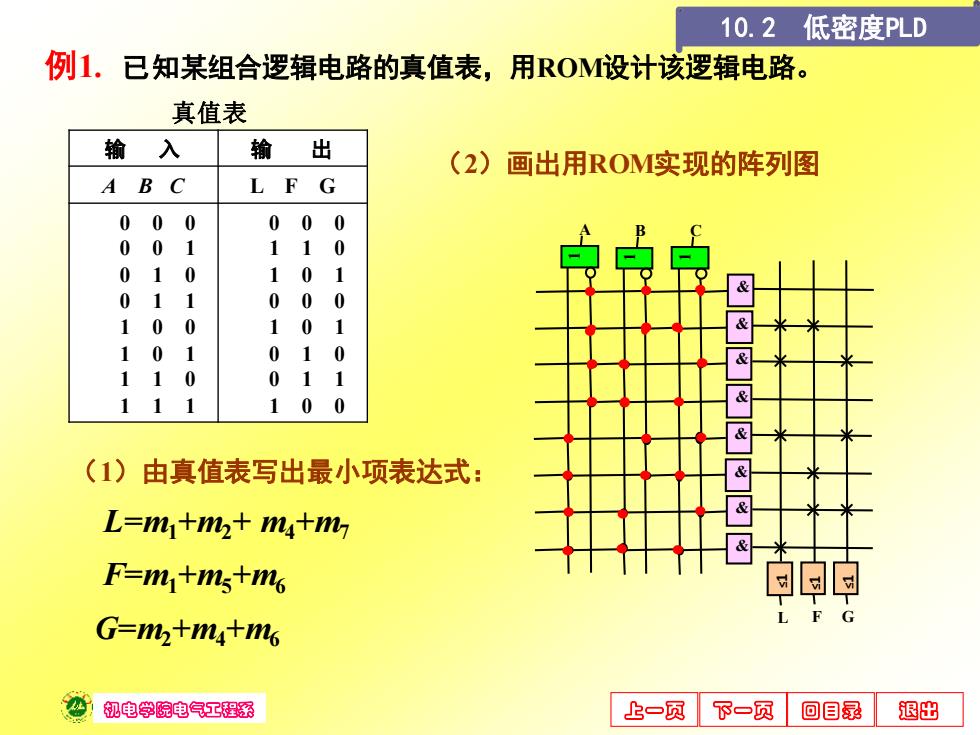

10.2低密度PLD 例1.已知某组合逻辑电路的真值表,用ROM设计该逻辑电路。 真值表 输 入 输 出 (2) 画出用ROM实现的阵列图 ABC L FG 000 000 001 110 010 101 011 000 & 100 101 1 01 010 & 1 1 0 0 11 1 1 00 & (1)由真值表写出最小项表达式: L=m1+m2+m+ F-m+ms+m 肉自向 L FG G=m2+n4+n6 机电学院电气工程系 上一页 下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 例1. 已知某组合逻辑电路的真值表,用ROM设计该逻辑电路。 输 入 输 出 A B C L F G 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 0 0 0 1 1 0 1 0 1 0 0 0 1 0 1 0 1 0 0 1 1 1 0 0 真值表 (1)由真值表写出最小项表达式: L=m1+m2+ m4+m7 F=m1+m5+m6 G=m2+m4+m6 (2)画出用ROM实现的阵列图 & ≤1 & L G A B F 1 C 1 & & & & & 1 & ≤1 ≤1 10.2 低密度PLD