K芯科骏 EDA技术与VHDL 第10章 VHDL结构

EDA技术与VHDL 第10章 VHDL结构 KX 康芯科技

K康还科技 8.1VHDL实体 VHDL实体作为一个设计实体(独立的电路功能结构) 的组成部分,其功能是对这个设计实体与外部电路进行接 口描述。实体是设计实体的表层设计单元,实体说明部分 规定了设计单元的输入输出接口信号或引脚,它是设计实 体对外的一个通信界面。实体的具体表述和用法已在前面 有过详细例解,这里不再重复

KX 康芯科技 8.1 VHDL实体 VHDL实体作为一个设计实体(独立的电路功能结构) 的组成部分,其功能是对这个设计实体与外部电路进行接 口描述。实体是设计实体的表层设计单元,实体说明部分 规定了设计单元的输入输出接口信号或引脚,它是设计实 体对外的一个通信界面。实体的具体表述和用法已在前面 有过详细例解,这里不再重复。 KX 康芯科技

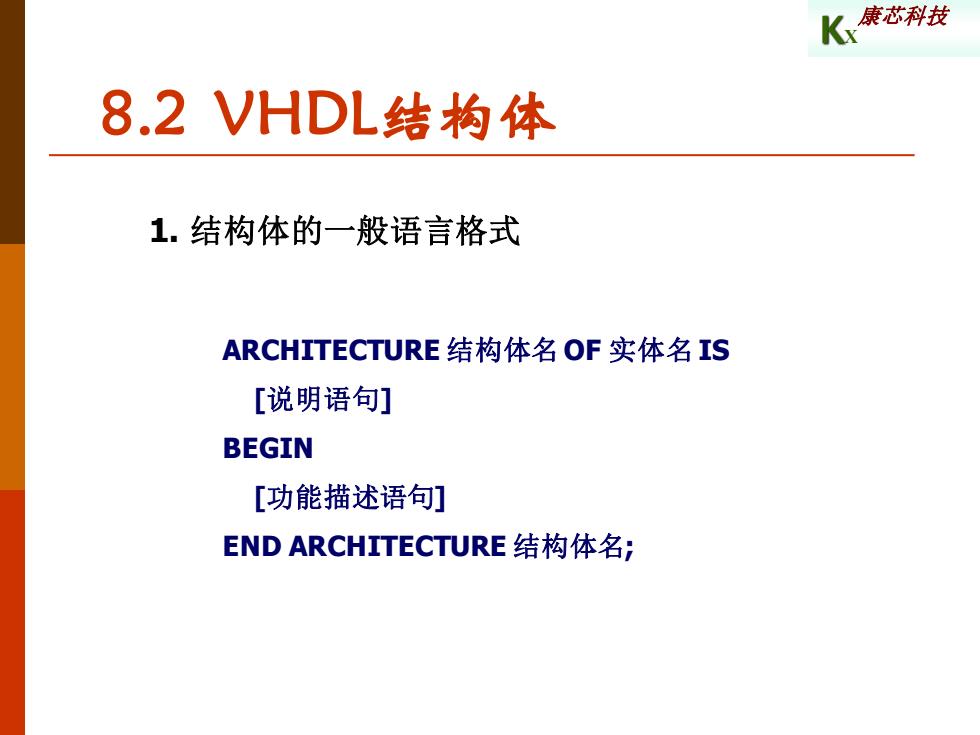

K能芯科技 8.2VHDL结构体 1.结构体的一般语言格式 ARCHITECTURE结构体名OF实体名IS [说明语句] BEGIN [功能描述语句] END ARCHITECTURE结构体名;

KX 康芯科技 8.2 VHDL结构体 1. 结构体的一般语言格式 ARCHITECTURE 结构体名 OF 实体名 IS [说明语句] BEGIN [功能描述语句] END ARCHITECTURE 结构体名;

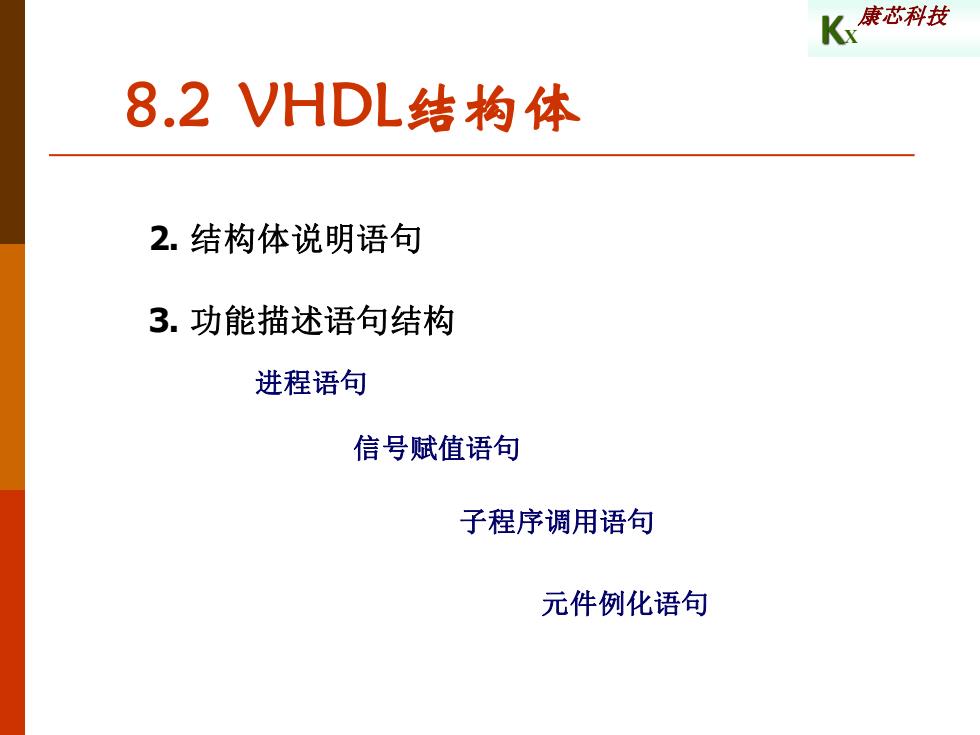

K康科技 8.2VHDL结构体 2.结构体说明语句 3.功能描述语句结构 进程语句 信号赋值语句 子程序调用语句 元件例化语句

KX 康芯科技 8.2 VHDL结构体 2. 结构体说明语句 3. 功能描述语句结构 进程语句 信号赋值语句 子程序调用语句 元件例化语句

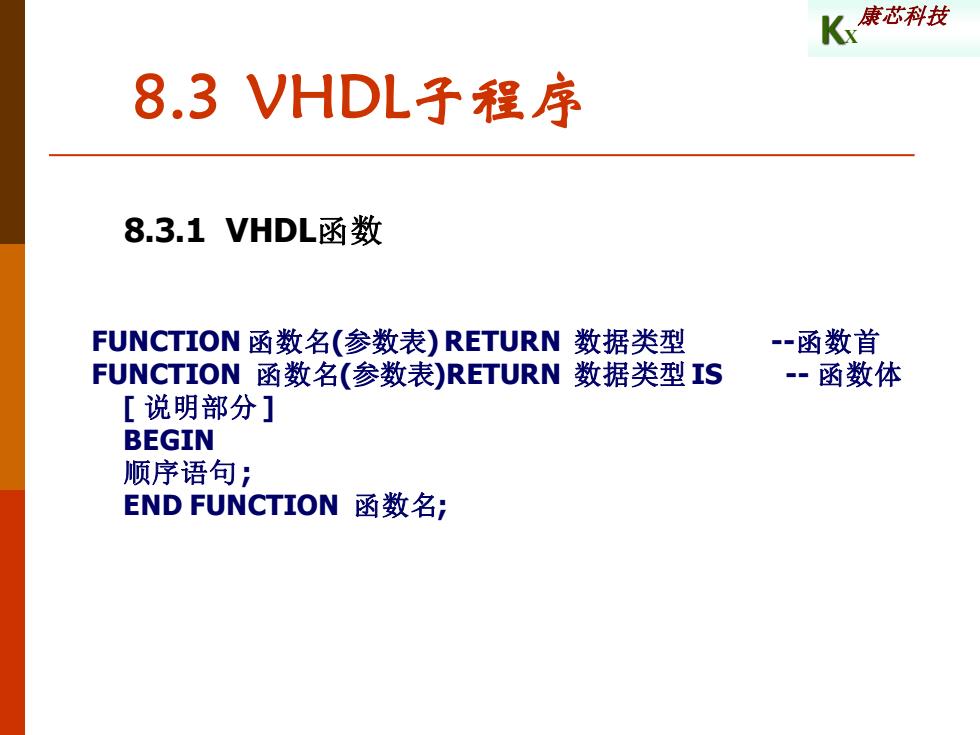

K康芯科技 8.3VHDL子程序 8.3.1VHDL函数 FUNCTION函数名(参数表)RETURN数据类型 -函数首 FUNCTION函数名(参数表)RETURN数据类型IS 函数体 [说明部分] BEGIN 顺序语句; END FUNCTION函数名;

KX 康芯科技 8.3 VHDL子程序 8.3.1 VHDL函数 FUNCTION 函数名(参数表) RETURN 数据类型 -函数首 FUNCTION 函数名(参数表)RETURN 数据类型 IS - 函数体 [ 说明部分 ] BEGIN 顺序语句 ; END FUNCTION 函数名;

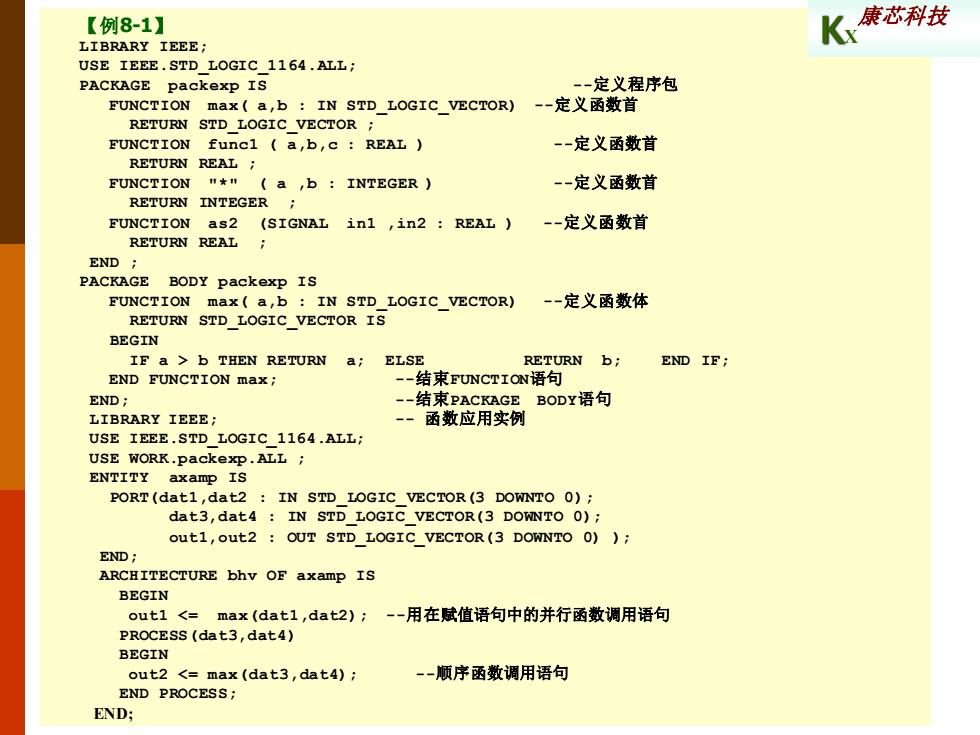

【例8-1】 LIBRARY IEEE; K顾还科技 USE IEEE.STD LOGIC 1164.ALL; PACKAGE packexp IS -一定义程序包 FUNCTION max(a,b:IN STD_LOGIC_VECTOR) -定义函数首 RETURN STD LOGIC VECTOR; FUNCTION funcl a,b,c:REAL -定义函数首 RETURN REAL FUNCTION a ,b:INTEGER -定义函数首 RETURN INTEGER FUNCTION as2 (SIGNAL in1,in2 REAL -一定义函数首 RETURN REAL END PACKAGE BODY packexp IS FUNCTION max(a,b:IN STD_LOGIC_VECTOR) -定义函数体 RETURN STD_LOGIC_VECTOR IS BEGIN IF a b THEN RETURN a;ELSE RETURN b; END IF; END FUNCTION max; -结束UNCTION语句 END; -结束PACKAGE BODY语句 LIBRARY IEEE; -一函数应用实例 USE IEEE.STD LOGIC 1164.ALL; USE WORK.packexp.ALL ENTITY axamp IS PORT(dat1,dat2 IN STD LOGIC VECTOR(3 DOWNTO 0); dat3,dat4 IN STD_LOGIC_VECTOR(3 DOWNTO 0); out1,out2 OUT STD LOGIC VECTOR(3 DOWNTO 0)); END; ARCHITECTURE bhv OF axamp IS BEGIN out1<=max(dat1,dat2);-用在赋值语句中的并行函数调用语句 PROCESS(dat3,dat4) BEGIN out2 <max(dat3,dat4); -顺序函数调用语句 END PROCESS; END;

KX 【例8-1】 康芯科技 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; PACKAGE packexp IS -定义程序包 FUNCTION max( a,b : IN STD_LOGIC_VECTOR) -定义函数首 RETURN STD_LOGIC_VECTOR ; FUNCTION func1 ( a,b,c : REAL ) -定义函数首 RETURN REAL ; FUNCTION "*" ( a ,b : INTEGER ) -定义函数首 RETURN INTEGER ; FUNCTION as2 (SIGNAL in1 ,in2 : REAL ) -定义函数首 RETURN REAL ; END ; PACKAGE BODY packexp IS FUNCTION max( a,b : IN STD_LOGIC_VECTOR) -定义函数体 RETURN STD_LOGIC_VECTOR IS BEGIN IF a > b THEN RETURN a; ELSE RETURN b; END IF; END FUNCTION max; -结束FUNCTION语句 END; -结束PACKAGE BODY语句 LIBRARY IEEE; - 函数应用实例 USE IEEE.STD_LOGIC_1164.ALL; USE WORK.packexp.ALL ; ENTITY axamp IS PORT(dat1,dat2 : IN STD_LOGIC_VECTOR(3 DOWNTO 0); dat3,dat4 : IN STD_LOGIC_VECTOR(3 DOWNTO 0); out1,out2 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ); END; ARCHITECTURE bhv OF axamp IS BEGIN out1 <= max(dat1,dat2); -用在赋值语句中的并行函数调用语句 PROCESS(dat3,dat4) BEGIN out2 <= max(dat3,dat4); -顺序函数调用语句 END PROCESS; END; KX 康芯科技

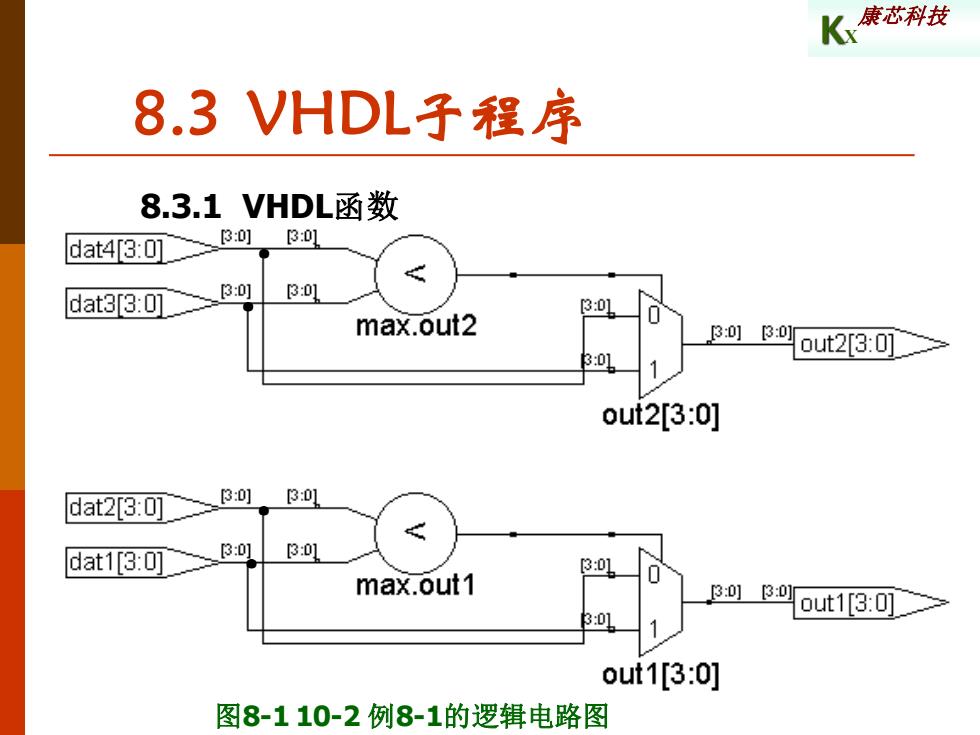

K策科技 8.3VHDL子程序 8.3.1VHDL函数 dat4[3:0] 3:0301 dat33:0] 3:0] 3:01 3:01 max.out2 B01Bout2[3:0] out23:0] dat2[3:0] 30] 301 dat1[3:可 30 301 30 max.out1 3:0]3:0] out1[3:0) out1[3:0] 图8-110-2例8-1的逻辑电路图

KX 康芯科技 8.3 VHDL子程序 8.3.1 VHDL函数 · · · · 图8-1 10-2 例8-1的逻辑电路图

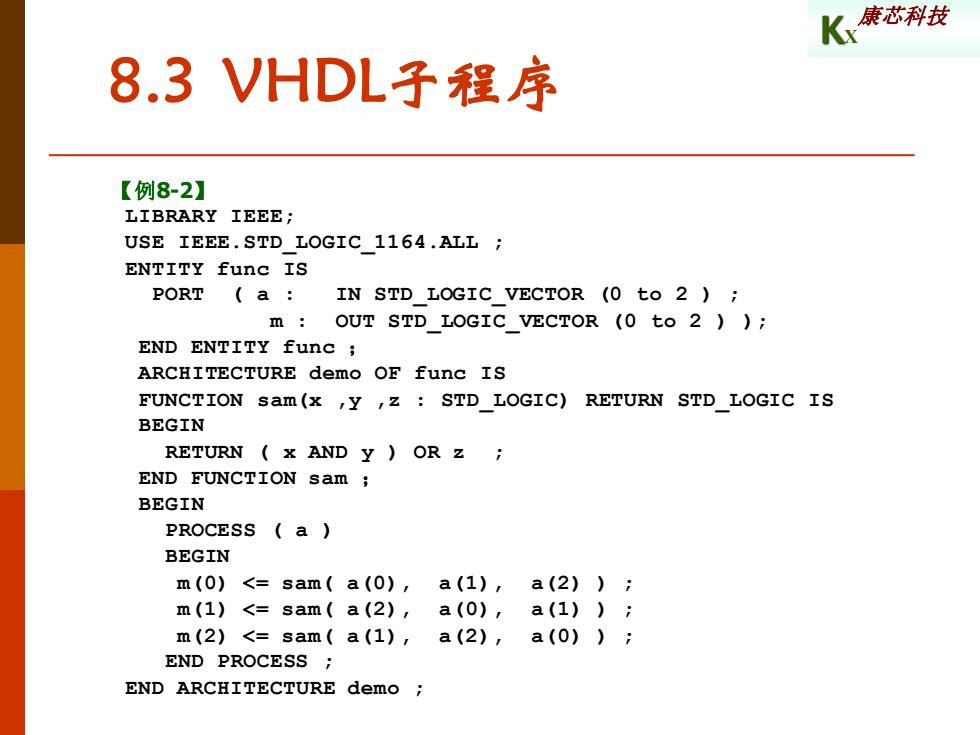

K康还科技 8.3VHDL子程序 【例8-2】 LIBRARY IEEE; USE IEEE.STD LOGIC 1164.ALL ENTITY func IS PORT a IN STD LOGIC VECTOR (0 to 2 ) m OUT STD LOGIC VECTOR (0 to 2 )) END ENTITY func ARCHITECTURE demo OF func IS FUNCTION sam (x,y,z:STD LOGIC)RETURN STD LOGIC IS BEGIN RETURN x AND y OR Z; END FUNCTION sam BEGIN PROCESS a BEGIN m(0)<=sam(a(0),a(1),a(2)); m(1)<=sam(a(2),a(0),a(1)); m(2)<=sam(a(1),a(2),a(0)); END PROCESS END ARCHITECTURE demo;

KX 康芯科技 8.3 VHDL子程序 【例8-2】 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL ; ENTITY func IS PORT ( a : IN STD_LOGIC_VECTOR (0 to 2 ) ; m : OUT STD_LOGIC_VECTOR (0 to 2 ) ); END ENTITY func ; ARCHITECTURE demo OF func IS FUNCTION sam(x ,y ,z : STD_LOGIC) RETURN STD_LOGIC IS BEGIN RETURN ( x AND y ) OR z ; END FUNCTION sam ; BEGIN PROCESS ( a ) BEGIN m(0) = sam( a(0), a(1), a(2) ) ; m(1) = sam( a(2), a(0), a(1) ) ; m(2) = sam( a(1), a(2), a(0) ) ; END PROCESS ; END ARCHITECTURE demo ;

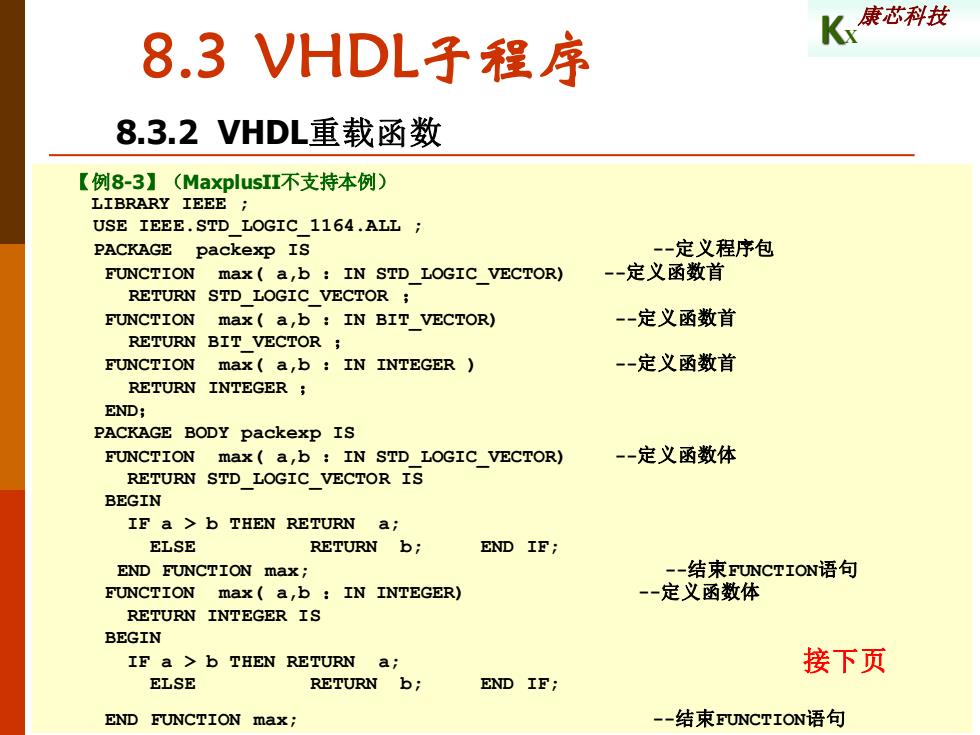

8.3VHDL子程序 K能芯科技 8.3.2VHDL重载函数 【例8-3】(MaxplusII不支持本例) LIBRARY IEEE USE IEEE.STD LOGIC 1164.ALL; PACKAGE packexp IS -定义程序包 FUNCTION max(a,b:IN STD LOGIC VECTOR) -定义函数首 RETURN STD LOGIC VECTOR FUNCTION max(a,b IN BIT VECTOR) -定义函数首 RETURN BIT VECTOR FUNCTION max(a,b:IN INTEGER) -定义函数首 RETURN INTEGER END; PACKAGE BODY packexp IS FUNCTION max a,b IN STD LOGIC VECTOR) -定义函数体 RETURN STD LOGIC VECTOR IS BEGIN IF a b THEN RETURN a; ELSE RETURN b; END IF; END FUNCTION max; -结束NCTION语句 FUNCTION max(a,b IN INTEGER) -定义函数体 RETURN INTEGER IS BEGIN IF a b THEN RETURN a; 接下页 ELSE RETURN b; END IF; END FUNCTION max; -结束FUNCTION语句

KX 康芯科技 8.3 VHDL子程序 8.3.2 VHDL重载函数 【例8-3】(MaxplusII不支持本例) LIBRARY IEEE ; USE IEEE.STD_LOGIC_1164.ALL ; PACKAGE packexp IS -定义程序包 FUNCTION max( a,b :IN STD_LOGIC_VECTOR) -定义函数首 RETURN STD_LOGIC_VECTOR ; FUNCTION max( a,b :IN BIT_VECTOR) -定义函数首 RETURN BIT_VECTOR ; FUNCTION max( a,b :IN INTEGER ) -定义函数首 RETURN INTEGER ; END; PACKAGE BODY packexp IS FUNCTION max( a,b :IN STD_LOGIC_VECTOR) -定义函数体 RETURN STD_LOGIC_VECTOR IS BEGIN IF a > b THEN RETURN a; ELSE RETURN b; END IF; END FUNCTION max; -结束FUNCTION语句 FUNCTION max( a,b :IN INTEGER) -定义函数体 RETURN INTEGER IS BEGIN IF a > b THEN RETURN a; ELSE RETURN b; END IF; END FUNCTION max; -结束FUNCTION语句 接下页

FUNCTION max a,b IN BIT VECTOR) -一定义函数体 K康还科技 RETURN BIT VECTOR IS BEGIN IF a b THEN RETURN a; ELSE RETURN b; END IF; END FUNCTION max; -结束UNCTION语句 END; -结束PACKAGE BODY语句.-以下是调用重载函数max的程序: LIBRARY IEEE USE IEEE.STD_LOGIC_1164.ALL; USE WORK.packexp.ALL; ENTITY axamp IS PORT (a1,b1 IN STD LOGIC VECTOR(3 DOWNTO 0); a2,b2 IN BIT VECTOR(4 DOWNTO 0); a3,b3 IN INTEGER RANGE 0 TO 15; c1 OUT STD LOGIC VECTOR(3 DOWNTO 0); c2 OUT BIT_VECTOR(4 DOWNTO 0); c3 OUT INTEGER RANGE 0 TO 15); END ARCHITECTURE bhv OF axamp IS BEGIN c1<= max(al,b1);-对函数max(a,b:IN STD_LOGIC_VECTOR)的调用 c2<= max(a2,b2);-对函数max(a,b:IN BIT_VECTO)的调用 c3<= max(a3,b3);-对函数max(a,b:IN INTEGER)的调用 END;

KX FUNCTION max( a,b :IN BIT_VECTOR) -定义函数体 康芯科技 RETURN BIT_VECTOR IS BEGIN IF a > b THEN RETURN a; ELSE RETURN b; END IF; END FUNCTION max; -结束FUNCTION语句 END; -结束PACKAGE BODY语句. - 以下是调用重载函数max的程序: LIBRARY IEEE ; USE IEEE.STD_LOGIC_1164.ALL ; USE WORK.packexp.ALL; ENTITY axamp IS PORT(a1,b1 : IN STD_LOGIC_VECTOR(3 DOWNTO 0); a2,b2 : IN BIT_VECTOR(4 DOWNTO 0); a3,b3 : IN INTEGER RANGE 0 TO 15; c1 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); c2 : OUT BIT_VECTOR(4 DOWNTO 0); c3 : OUT INTEGER RANGE 0 TO 15); END; ARCHITECTURE bhv OF axamp IS BEGIN c1 <= max(a1,b1); -对函数max( a,b :IN STD_LOGIC_VECTOR)的调用 c2 <= max(a2,b2); -对函数max( a,b :IN BIT_VECTOR) 的调用 c3 <= max(a3,b3); -对函数max( a,b :IN INTEGER) 的调用 END; KX 康芯科技