K康芯科技 EDA技术与VHDL 第1章 概述

EDA技术与VHDL 第1章 概 述 KX 康芯科技

K 康芯科技 1.1电子设计自动化技术及其发展 现代电子设计技术的核心已日趋转向基于计算机的电子 设计自动化技术,即 EDA(Electronic Design Automation)技术。 20世纪70年代 EDA技术的发展 分为三个阶段 20世纪80年代 20世纪90年代

KX 康芯科技 1.1 电子设计自动化技术及其发展 现代电子设计技术的核心已日趋转向基于计算机的电子 设计自动化技术,即 EDA(Electronic Design Automation) 技术。 EDA技术的发展 分为三个阶段 20世纪70年代 20世纪80年代 20世纪90年代

K康芯科技 1.1EDA技术及其发展 EDA技术在进入21世纪后,得到了更大的发展 在FPGA上实现DSP(数字信号处理)应用成为可能 在一片FPGA中实现一个完备的数字处理系统成为可能 功能强大的EDA软件不断推出 电子技术领域全方位融入EDA技术 EDA使得电子领域各学科的界限更加模糊,更加互为包容 基于EDA的用于ASIC设计的标准单元已涵盖大规模电子系统 软硬P(ntellectual Property)核在电子行业的产业领域广泛应用 SoC高效低成本设计技术的成熟 使复杂电子系统的设计和验证趋于简单

KX 康芯科技 1.1 EDA技术及其发展 EDA技术在进入21世纪后,得到了更大的发展 在FPGA上实现DSP(数字信号处理)应用成为可能 在一片FPGA中实现一个完备的数字处理系统成为可能 功能强大的EDA软件不断推出 电子技术领域全方位融入EDA技术 EDA使得电子领域各学科的界限更加模糊,更加互为包容 基于EDA的用于ASIC设计的标准单元已涵盖大规模电子系统 软硬IP(Intellectual Property)核在电子行业的产业领域广泛应用 SoC高效低成本设计技术的成熟 使复杂电子系统的设计和验证趋于简单

K 康芯科技 1.2电子设计自动化应用对象 利用EDA技术进行电子系统设计,最后的实现的目标 全定制或半定制ASIC FPGA/CPLD(或称可编程ASIC)开发应用 PCB (印制电路板)

KX 康芯科技 1.2 电子设计自动化应用对象 利用EDA技术进行电子系统设计,最后的实现的目标 全定制或半定制ASIC FPGA/CPLD(或称可编程ASIC)开发应用 PCB(印制电路板)

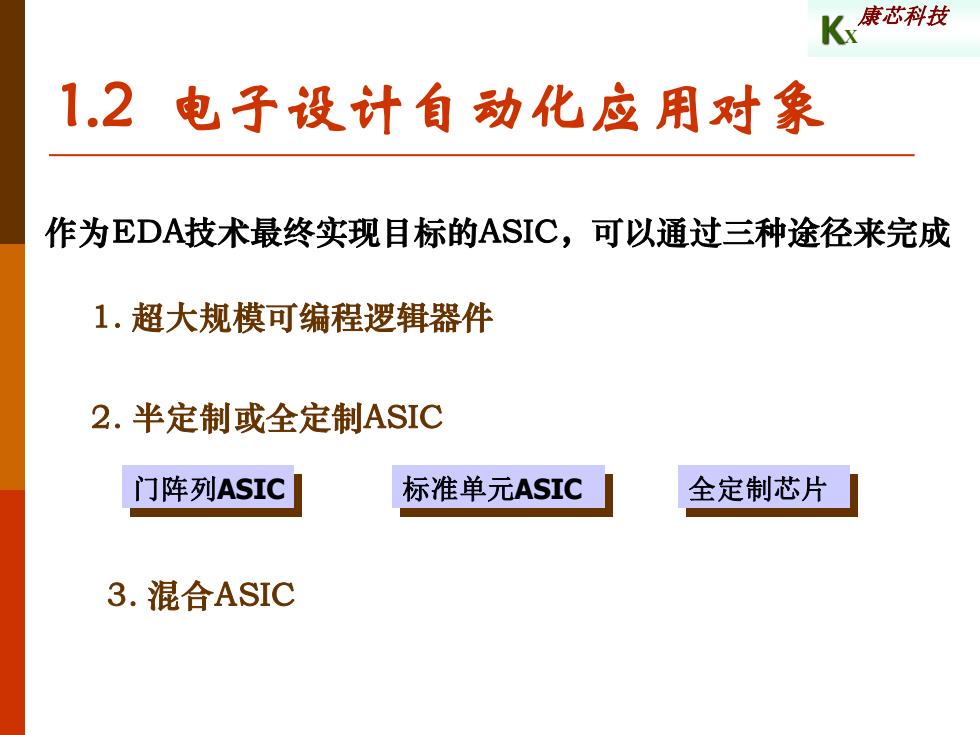

K康芯科我 1.2电子设计自动化应用对象 作为EDA技术最终实现目标的ASIC,可以通过三种途径来完成 1.超大规模可编程逻辑器件 2.半定制或全定制ASIC 门阵列ASIC 标准单元ASIC 全定制芯片 3.混合ASIC

KX 康芯科技 1.2 电子设计自动化应用对象 门阵列ASIC 1. 超大规模可编程逻辑器件 2. 半定制或全定制ASIC 标准单元ASIC 全定制芯片 3. 混合ASIC 作为EDA技术最终实现目标的ASIC,可以通过三种途径来完成

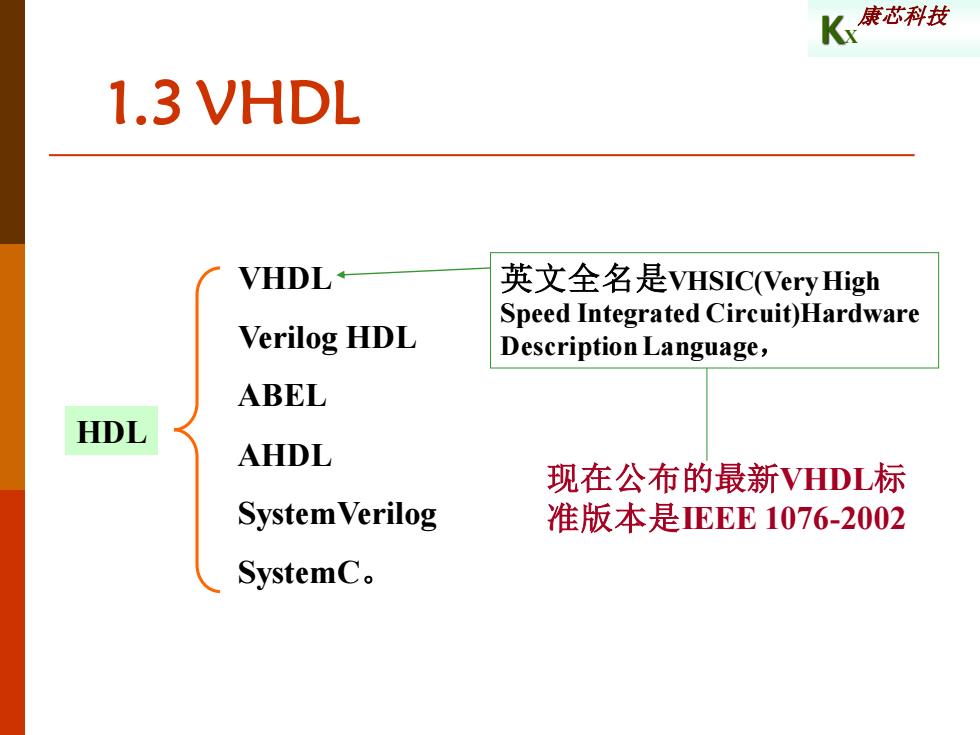

K康还科技 1.3 VHDL VHDL 英文全名是VHSIC(VeryHigh Speed Integrated Circuit)Hardware Verilog HDL Description Language, ABEL HDL AHDL 现在公布的最新VHDL标 System Verilog 准版本是EEE1076-2002 SystemC

KX 康芯科技 1.3 VHDL HDL VHDL Verilog HDL ABEL AHDL SystemVerilog SystemC。 英文全名是VHSIC(Very High Speed Integrated Circuit)Hardware Description Language, 现在公布的最新VHDL标 准版本是IEEE 1076-2002

K能花科液 1.4EDA的优势 1.可以大大降低设计成本,缩短设计周期。 2.库都是EDA公司与半导体生产厂商合作、共同开发。 3.极大地简化设计文档的管理。 4.极大地提高了大规模系统电子设计的自动化程度。 5.设计者拥有完全的自主权,再无受制于人之虞 6.良好的可移植与可测试性,为系统开发提供可靠的保证。 7.能将所有设计环节纳入统一的自顶向下的设计方案中。 8.在系统板设计结束后仍可利用计算机对硬件系统进行完整 的测试

KX 康芯科技 1.4 EDA的优势 1.可以大大降低设计成本,缩短设计周期。 2.库都是EDA公司与半导体生产厂商合作、共同开发。 3.极大地简化设计文档的管理。 4.极大地提高了大规模系统电子设计的自动化程度。 5.设计者拥有完全的自主权,再无受制于人之虞 6.良好的可移植与可测试性,为系统开发提供可靠的保证。 7.能将所有设计环节纳入统一的自顶向下的设计方案中。 8.在系统板设计结束后仍可利用计算机对硬件系统进行完整 的测试

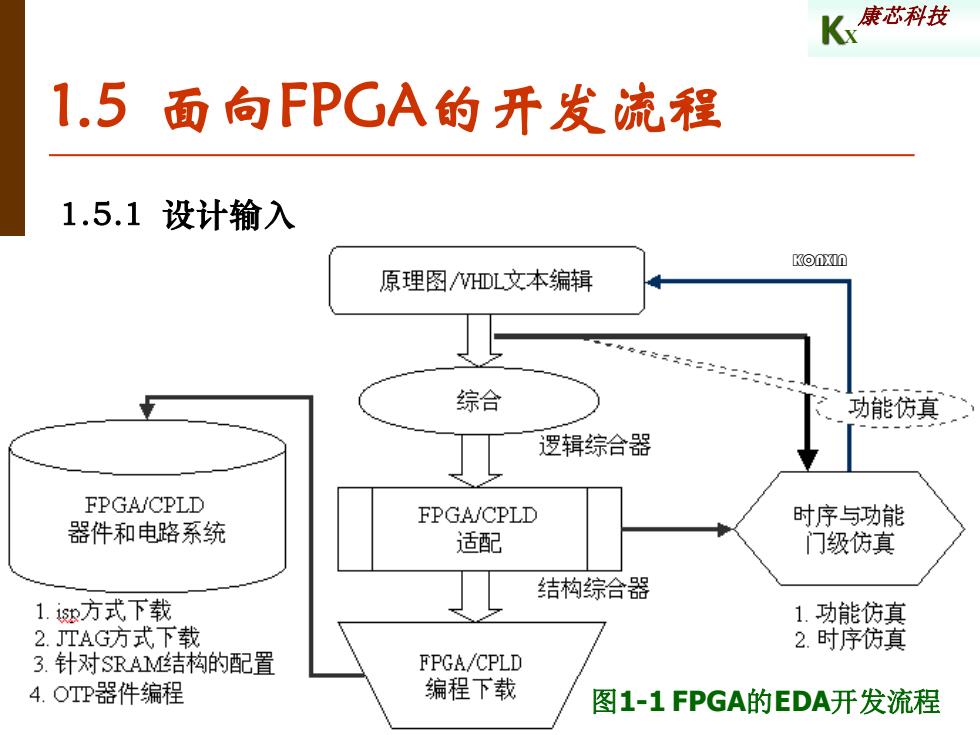

K康科技 1.5面向FPGA的开发流程 1.5.1设计输入 Konxin 原理图WDL文本编辑 综合 功能仿真, 逻辑综合器 FPGA/CPLD FPGA/CPLD 器件和电路系统 时序与功能 适配 门级仿真 结构综合器 1.♪方式下载 1.功能仿真 2.TAG方式下载 2.时序仿真 3.针对SRAM结构的配置 FPGA/CPLD 4.OIP器件编程 编程下载 图1-1FPGA的EDA开发流程

KX 康芯科技 1.5 面向FPGA的开发流程 1.5.1 设计输入 图1-1 FPGA的EDA开发流程 KONXIN

K能芯科技 1.5面向FP℃A的开发流程 1.5.1设计输入 原理图输入 1.图形输入 状态图输入 波形图输入 2.硬件描述语言文本输入

KX 康芯科技 1.5 面向FPGA的开发流程 1.5.1 设计输入 1. 图形输入 原理图输入 状态图输入 波形图输入 2. 硬件描述语言文本输入

K康还科技 1.5面向FPCA的开发流程 1.5.2综合 1.5.3布线布局(适配) 1.5.4仿真 时序仿真 功能仿真 1.5.5下载和硬件测试

KX 康芯科技 1.5 面向FPGA的开发流程 1.5.2 综合 1.5.3 布线布局(适配) 1.5.4 仿真 时序仿真 功能仿真 1.5.5 下载和硬件测试