K能花科技 EDA技术与VHDL 第6幸 16位CISC CPU设计

EDA技术与VHDL 第6章 16位CISC CPU设计 KX 康芯科技

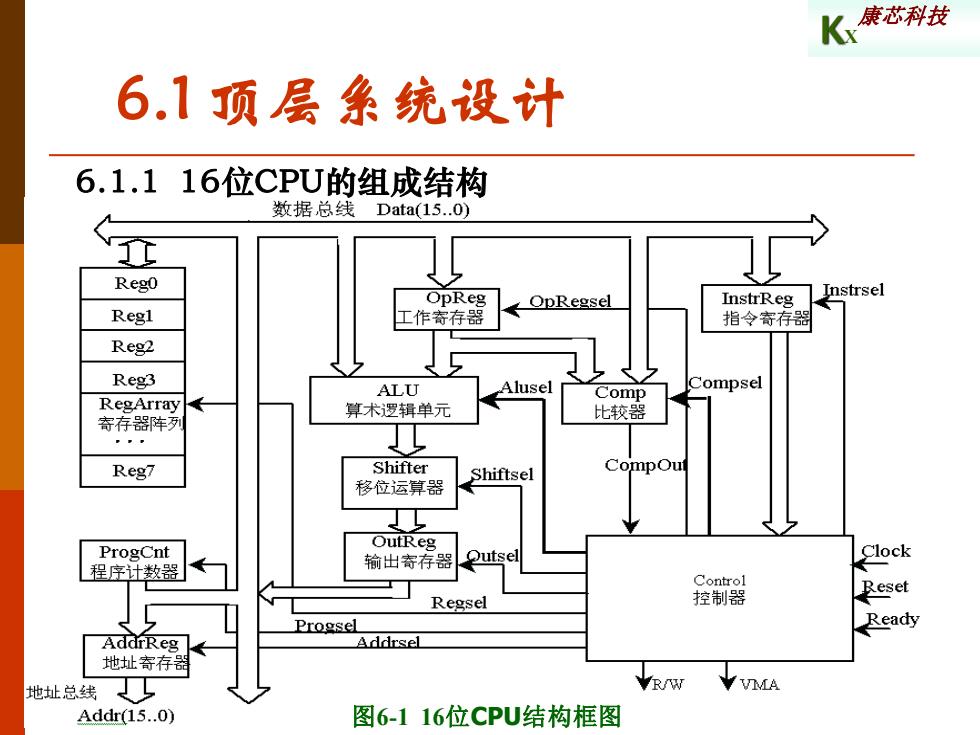

K 康芯科技 6.1顶层系统设计 6.1.116位CPU的组成结构 数据总线Data(15.0) Rego OpReg OpRegsel InstrReg Instrsel Regl 工作寄存器 指令寄存器 Reg2 Reg3 ALU Alusel Compsel Comp RegArray 算术逻辑单元 比较器 寄存器阵 Reg7 Shifter Shiftsel CompOu 移位运算器 J OutReg ProgCnt 程序计数器」《 输出寄存器 Clock Control 控制器 Reset Regsel Progsel Ready AddrReg Addrsel 地址寄存器 地址总线丁工 R/W Addr(15.0) 图6-116位CPU结构框图

KX 康芯科技 6.1 顶层系统设计 6.1.1 16位CPU的组成结构 图6-1 16位CPU结构框图 KX 康芯科技

K康在科拉 6.1顶层象统设计 6.1.2指令系统设计 1,指令格式 (1)单字指令 操作码 源操作数 目的操作数 Opcode SRC DST 15 14 13 12 11 5 3 2 1 0 图6-1单字节指令格式

KX 康芯科技 6.1 顶层系统设计 6.1.2指令系统设计 1.指令格式 KX 康芯科技 图6-1 单字节指令格式 (1)单字指令

K康芯科技 6.1顶层象统设计 ())N之地△ 操作码 目的操作数 Opcode DST 1514 131211 2 1 0 16位操作数 15 14131211109 8 6 54 3 2 图6-2双字指令格式 操作码 目的操作数 00 100 0 01 0000000000010101 0 0 1 5 图6-3双字节指令

KX 康芯科技 6.1 顶层系统设计 图6-2 双字指令格式 (2)双字指令 图6-3 双字节指令

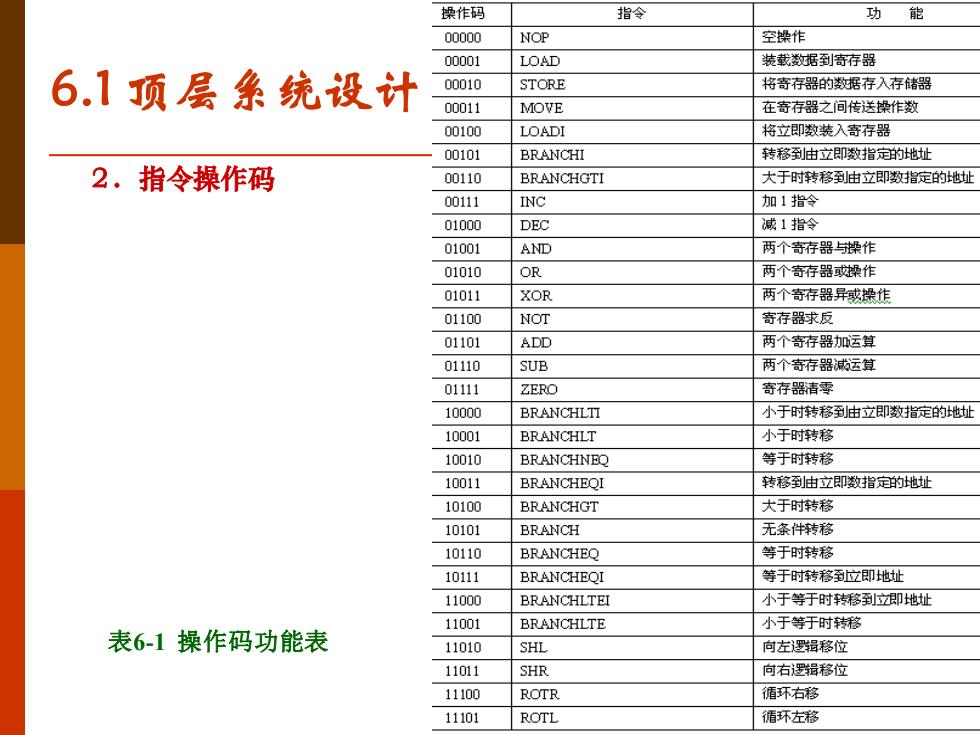

操作码 指令 功能 00000 NOP 空操作 00001 LOAD 装载数据到寄存器 6.1顶层象统设计 00010 STORE 格寄存器的数据存入存储器 00011 MOVE 在寄存器之间传送操作数 00100 LOADI 将立即数装入寄存器 00101 BRANCHI 转移到由立即数指定的地址 2。指令操作码 00110 BRANCHGTI 大于时转移到由立即数指定的地址 00111 INC 加1指冷 01000 DEC 减1指令 01001 AND 两个寄存器操作 01010 OR 两个奇存器或操作 01011 XOR 两个寄存器异感操作 01100 NOT 寄存器求反 01101 ADD 两个寄存器加运算 01110 SUB 两个寄存器减运算 01111 ZERO 寄存器清零 10000 BRANCHLTI 小于时转移到由立即数指定的地址 10001 BRANCHLT 小于时转移 10010 BRANCHNEQ 等于时转移 10011 BRANCHEQI 转移到由立即数指定的地址 10100 BRANCHGT 大于时转移 10101 BRANCH 无条件转移 10110 BRANCHEO 等于时转移 10111 BRANCHEQI 等于时转移到位即地址 11000 BRANCHLTEI 小于等于时转移到位即地址 11001 BRANCHLTE 小于等于时转移 表6-1操作码功能表 11010 SHL 向左逻辑移位 11011 SHR 向右逻辑移位 11100 ROTR 循环右移 11101 ROTL 循环左移

KX 康芯科技 6.1 顶层系统设计 2.指令操作码 KX 康芯科技 表6-1 操作码功能表

K 康芯科技 6.1顶层象统设计 2.指令操作码 表6-2常用指令举例 指令 机器码 字长 操作码 源作数 目的操作 功能说明 Opcode SRC 数DST 2001H 0 0 10 08 88 8 中 0 0 立即数0021H LOADI R1,0021H 2 0021H 0 0 0 0 0 0 00 0 0 0 0 0 送R1 从R1指定的存储 LOAD R3,[R1] 080BH 0 0 0 0 0 0 单元取数送R3 将R3的内容存 STORE [R2],R3 101AH 0 0 0 0 0 入R2指定单元 BRANCHGTI 300EH 0 若R1>R6,则 2 [0000] 0000H 0 0 0 0 转向地址[0000] 修改目的指 INC R2 3802H 0 0 针R.2<=R2+1 2800H 0 绝对地址转移指 BRANCHI [0006] 0006H 0 00 0 令,goto[0006]

KX 康芯科技 6.1 顶层系统设计 表6-2 常用指令举例 2.指令操作码

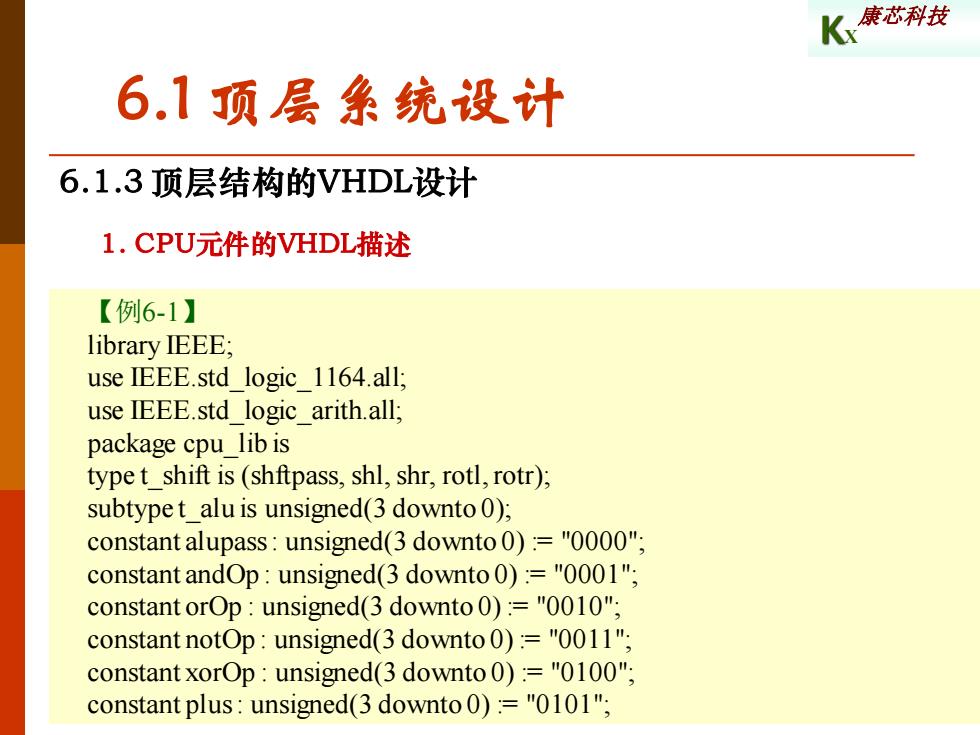

K康科技 6.1顶层象统设计 6.1.3顶层结构的VHDL设计 1.CPU元件的VHDL描述 【例6-1】 library IEEE; use IEEE.std logic_1164.all; use IEEE.std logic arith.all; package cpu lib is typet shift is(shftpass,shl,shr,rotl,rotr); subtypet alu is unsigned(3 downto 0); constant alupass:unsigned(3 downto 0):="0000"; constant andOp:unsigned(3 downto0):="0001"; constant orOp:unsigned(3 downto 0):="0010"; constant notOp:unsigned(3 downto0):="0011"; constant xorOp:unsigned(3 downto0):="0100"; constant plus:unsigned(3 downto0):="0101";

KX 康芯科技 6.1 顶层系统设计 1. CPU元件的VHDL描述 6.1.3 顶层结构的VHDL设计 【例6-1】 library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_arith.all; package cpu_lib is type t_shift is (shftpass, shl, shr, rotl, rotr); subtype t_alu is unsigned(3 downto 0); constant alupass : unsigned(3 downto 0) := "0000"; constant andOp : unsigned(3 downto 0) := "0001"; constant orOp : unsigned(3 downto 0) := "0010"; constant notOp : unsigned(3 downto 0) := "0011"; constant xorOp : unsigned(3 downto 0) := "0100"; constant plus : unsigned(3 downto 0) := "0101";

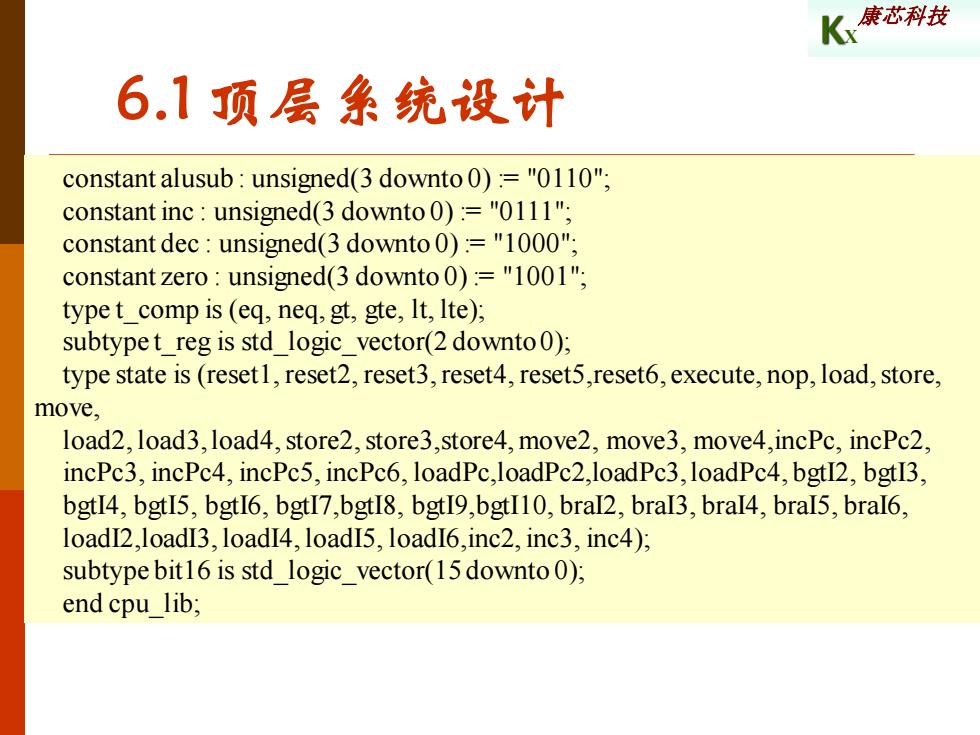

K康芯科技 6.1顶层系统设计 constant alusub:unsigned(3 downto 0):="0110"; constant inc:unsigned(3 downto0):="0111"; constant dec:unsigned(3 downto 0):="1000"; constant zero:unsigned(3 downto0):="1001"; type t_comp is (eq,neq,gt,gte,It,Ite); subtypet_reg is std_logic_vector(2 downto0); type state is(reset1,reset2,reset3,reset4,reset5,reset6,execute,nop,load,store, move, load2,load3,load4,store2,store3,store4,move2,move3,move4,incPc,incPc2, incPc3,incPc4,incPc5,incPc6,loadPc,loadPc2,loadPc3,loadPc4,bgtI2,bgtI3, bgt14,bgt15,bgt16,bgt17,bgtI8,bgt19,bgt110,bral2,bral3,bral4,bral5,bral6, loadI2,loadI3,loadI4,loadI5,loadI6,inc2,inc3,inc4); subtype bit16 is std logic_vector(15 downto 0); end cpu lib;

KX 康芯科技 6.1 顶层系统设计 1. CPU元件的VHDL描述 6.1.3 constant alusub : unsigned(3 downto 0) := "0110"; 顶层结构的VHDL设计 constant inc : unsigned(3 downto 0) := "0111"; constant dec : unsigned(3 downto 0) := "1000"; constant zero : unsigned(3 downto 0) := "1001"; type t_comp is (eq, neq, gt, gte, lt, lte); subtype t_reg is std_logic_vector(2 downto 0); type state is (reset1, reset2, reset3, reset4, reset5,reset6, execute, nop, load, store, move, load2, load3,load4,store2,store3,store4, move2, move3, move4,incPc, incPc2, incPc3, incPc4, incPc5, incPc6, loadPc,loadPc2,loadPc3,loadPc4, bgtI2, bgtI3, bgtI4, bgtI5, bgtI6, bgtI7,bgtI8, bgtI9,bgtI10, braI2, braI3, braI4, braI5, braI6, loadI2,loadI3, loadI4, loadI5, loadI6,inc2, inc3, inc4); subtype bit16 is std_logic_vector(15 downto 0); end cpu_lib;

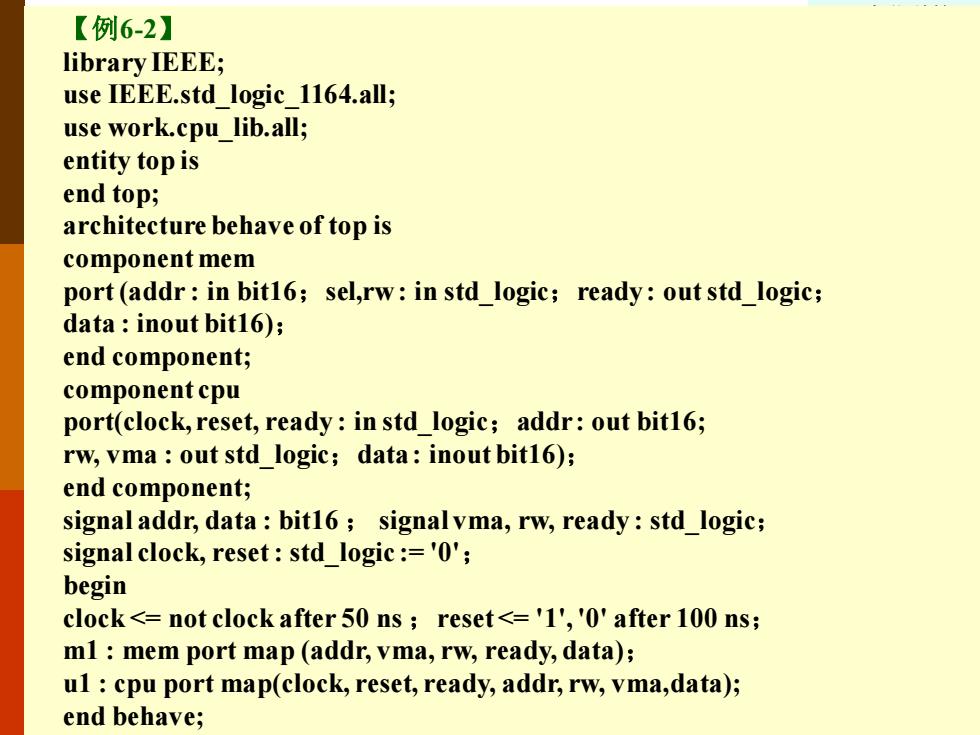

【例6-2】 library IEEE; use IEEE.std logic_1164.all; use work.cpu_lib.all; entity top is end top; architecture behave of top is component mem port(addr:in bit16;sel,rw:in std_logic;ready:out std_logic; data:inout bit16); end component; component cpu port(clock,reset,ready:in std_logic;addr:out bit16; rw,vma out std_logic;data:inout bit16); end component; signal addr,data:bit16;signal vma,rw,ready:std_logic; signal clock,reset std_logic:='0'; begin clock<=not clock after 50 ns reset<='1','0'after 100 ns; ml:mem port map (addr,vma,rw,ready,data); ul:cpu port map(clock,reset,ready,addr,rw,vma,data); end behave;

KX 康芯科技 6.1 顶层系统设计 1. CPU元件的VHDL描述 6.1.3 顶层结构的VHDL设计 【例6-2】 library IEEE; use IEEE.std_logic_1164.all; use work.cpu_lib.all; entity top is end top; architecture behave of top is component mem port (addr : in bit16;sel,rw : in std_logic;ready : out std_logic; data : inout bit16); end component; component cpu port(clock, reset, ready : in std_logic;addr : out bit16; rw, vma : out std_logic;data : inout bit16); end component; signal addr, data : bit16 ; signal vma, rw, ready : std_logic; signal clock, reset : std_logic := '0'; begin clock <= not clock after 50 ns ;reset <= '1', '0' after 100 ns; m1 : mem port map (addr, vma, rw, ready, data); u1 : cpu port map(clock, reset, ready, addr, rw, vma,data); end behave;

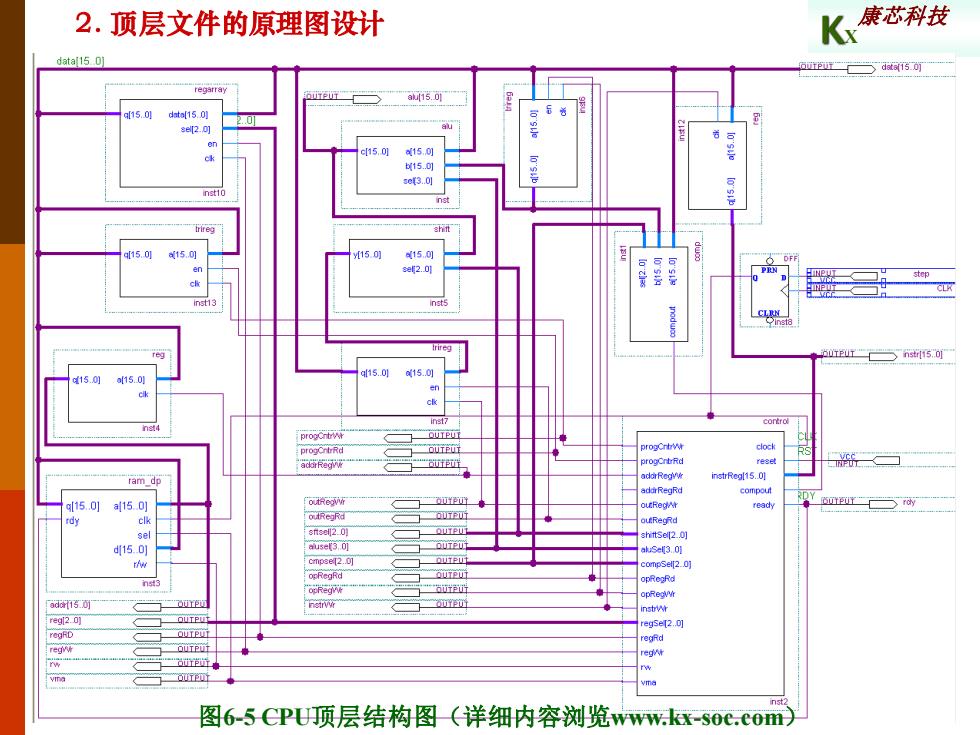

2.顶层文件的原理图设计 K康芯科技 data[150] 5可 regarray a15.01 a150dta15.01 0 8e2.0则 au en c15.015.0 t15.0可 se3.0 sh tt a15.0 150 15.0115.0则 82.0 step inst nst c15.0a15.01 q415.0c15.0 en ck progCntrRd “T adorkeg 进 progCrtrRd ram_dp addrReav instrRegl15.01 compou g15.01a1501 0e娇 rdy ouRegRd srsell2.0可 ausel3.0] OUTPUT OUTPI compSel2.0] ooReaRd opReqv 子出 opRedvv ad15商 reg]2.0] regsSe[2.0] regRd reg rw 图6-5CPU项层结构图(详细内容浏览www.kx-s0C.com)

KX 2. 顶层文件的原理图设计 康芯科技 图6-5 CPU顶层结构图(详细内容浏览www.kx-soc.com)