数字电子技术Digital Eleetronics Technolo 第七章脉中单元电路 石阿子大学《数字电子技木》保程组 电 活:0993-2057237 电子邮箱:rl mac(@shzu.edu.cn 机电学院电气工程系 上一页下一页回目绿 退出

机电学院电气工程系 上一页 下一页 回目录 退出 第七章 脉冲单元电路 数字电子技术Digital Electronics Technology 石河子大学《数字电子技术》课程组 电 话:0993-2057237 电子邮箱:rl_mac@shzu.edu.cn

7.1脉冲信号与脉冲电路 7.2集成555定时器 7.3施密特触发器 7.4多谐振荡器 7.5单稳态触发器 机电学院电气工程系 上一页下-页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 7.3 施密特触发器 7.4 多谐振荡器 7.1 脉冲信号与脉冲电路 7.2 集成555定时器 7.5 单稳态触发器

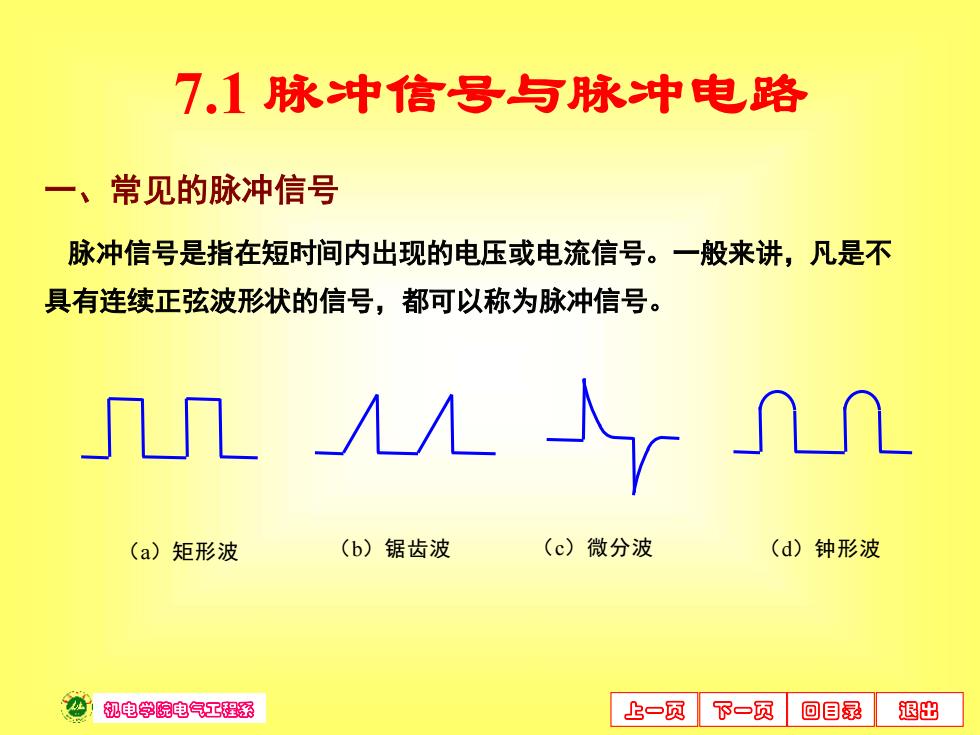

71脉冲信号与脉中电路 一、常见的脉冲信号 脉冲信号是指在短时间内出现的电压或电流信号。一般来讲,凡是不 具有连续正弦波形状的信号,都可以称为脉冲信号。 U几人人人y (a)矩形波 (b)锯齿波 (c)微分波 (d)钟形波 机电学院电气工程系 上-页下一页回目最 退出

机电学院电气工程系 上一页 下一页 回目录 退出 一、常见的脉冲信号 脉冲信号是指在短时间内出现的电压或电流信号。一般来讲,凡是不 具有连续正弦波形状的信号,都可以称为脉冲信号。 7.1 脉冲信号与脉冲电路 (a)矩形波 (b)锯齿波 (c)微分波 (d)钟形波

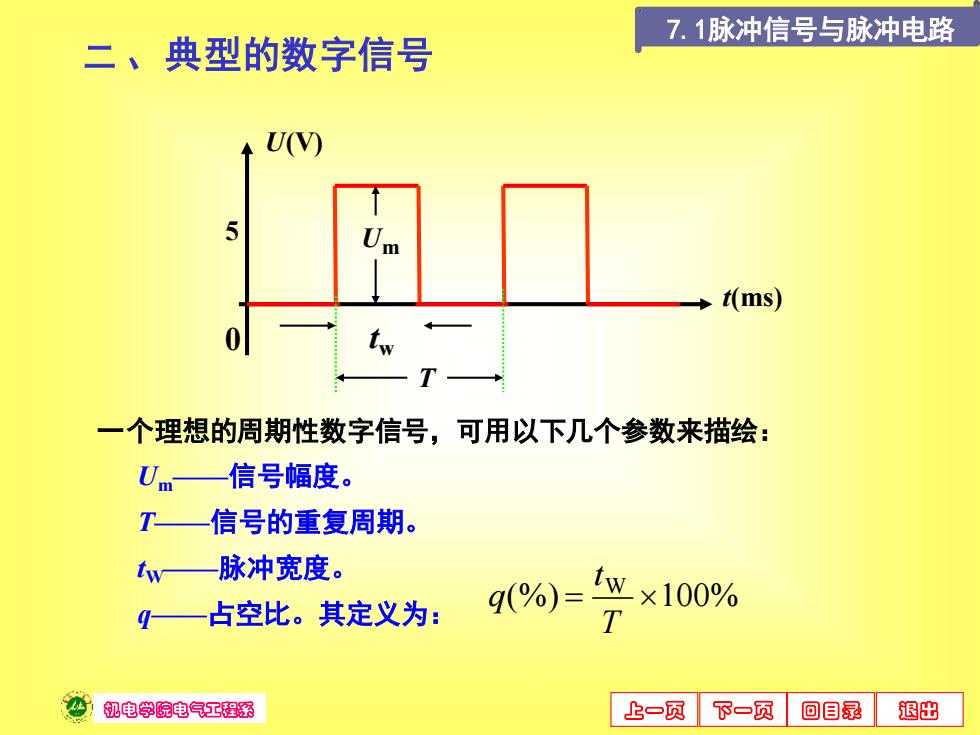

7.1脉冲信号与脉冲电路 二、典型的数字信号 U(V) 5 Um t(ms) 一个理想的周期性数字信号,可用以下几个参数来描绘: U 信号幅度。 T一信号的重复周期。 —脉冲宽度。 占空比。其定义为: 9(%)=y×100% 机电学院电气工程系 上一页 下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 二 、典型的数字信号 一个理想的周期性数字信号,可用以下几个参数来描绘: Um——信号幅度。 T——信号的重复周期。 tW——脉冲宽度。 q——占空比。其定义为: (%) = W 100% T t q 5 U(V) 0 t(ms) tw T Um 7.1脉冲信号与脉冲电路

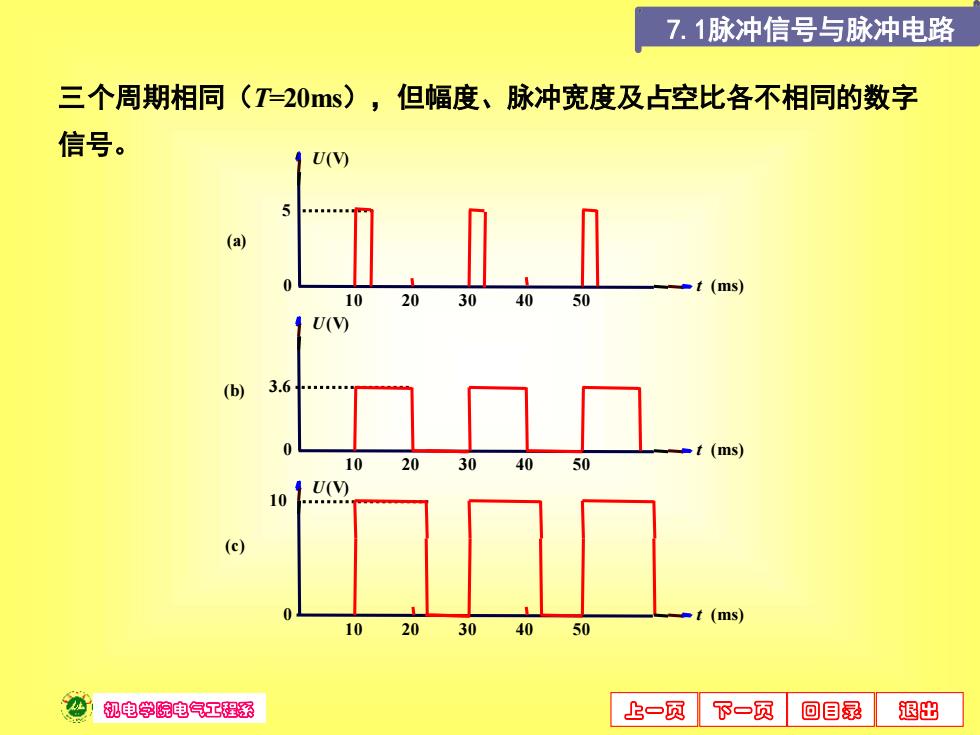

7.1脉冲信号与脉冲电路 三个周期相同(T=20ms),但幅度、脉冲宽度及占空比各不相同的数字 信号。 1U(V) (a) t (ms) 203040 U() (b) 3.6 (ms) 20 40 U() 10 (c) (ms) 20 4 机电学院电气工程系 上一页 下一页回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 三个周期相同(T=20ms),但幅度、脉冲宽度及占空比各不相同的数字 信号。 U t (V) (ms) 5 0 10 20 30 40 50 U t (V) 0 (ms) 10 20 30 40 50 U t (V) 0 (ms) 10 20 30 40 50 3.6 10 (a) (b) (c) 7.1脉冲信号与脉冲电路

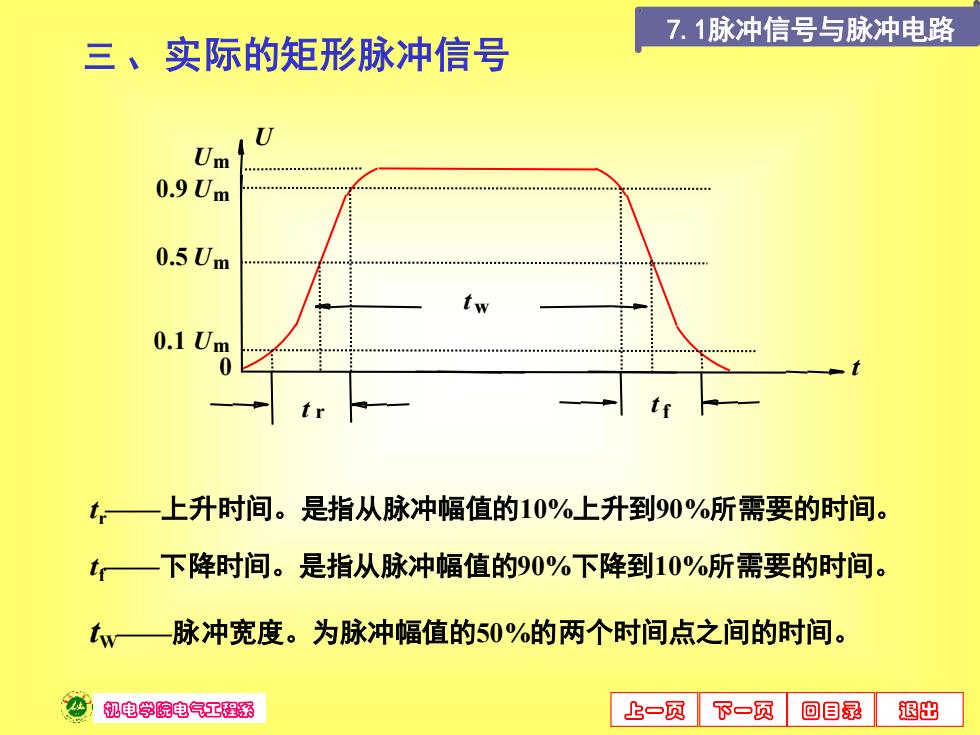

7.1脉冲信号与脉冲电路 三、实际的矩形脉冲信号 Um 0.9Um 0.5Um 0.1Um 0 t一上升时间。是指从脉冲幅值的10%上升到90%所需要的时间。 一下降时间。是指从脉冲幅值的90%下降到10%所需要的时间。 tw一脉冲宽度。为脉冲幅值的50%的两个时间点之间的时间。 机电学院电气工程系 上一页 下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 tr——上升时间。是指从脉冲幅值的10%上升到90%所需要的时间。 t f——下降时间。是指从脉冲幅值的90%下降到10%所需要的时间。 tW——脉冲宽度。为脉冲幅值的50%的两个时间点之间的时间。 三 、实际的矩形脉冲信号 0 t U Um Um Um 0.1 Um 0.5 0.9 t w t r t f 7.1脉冲信号与脉冲电路

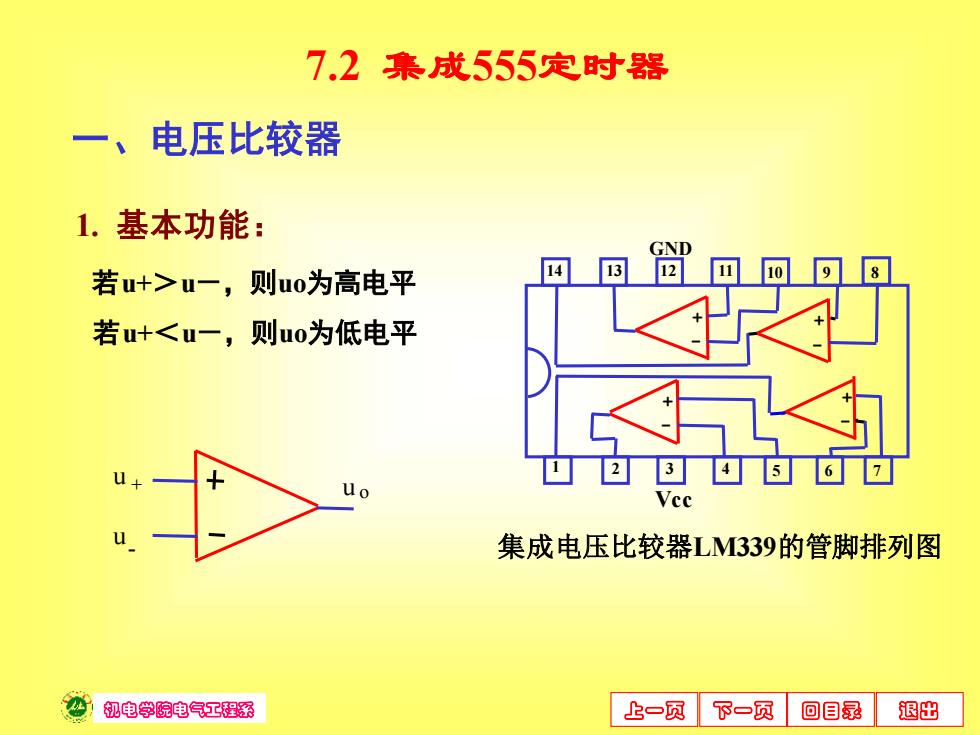

7.2集成555定时器 一、电压比较器 1.基本功能: GND 若u+>u一,则uo为高电平 4国2回回可8 若u+<u一,则uo为低电平 Vcc 集成电压比较器LM339的管脚排列图 机电学院电气工程系 上一页下一页回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 7.2 集成555定时器 一、电压比较器 1. 基本功能: 若u+>u-,则uo为高电平 若u+<u-,则uo为低电平 - + u o u u 1 2 3 4 5 6 7 Vcc - + - + - + 14 13 12 11 10 9 8 - + GND 集成电压比较器LM339的管脚排列图

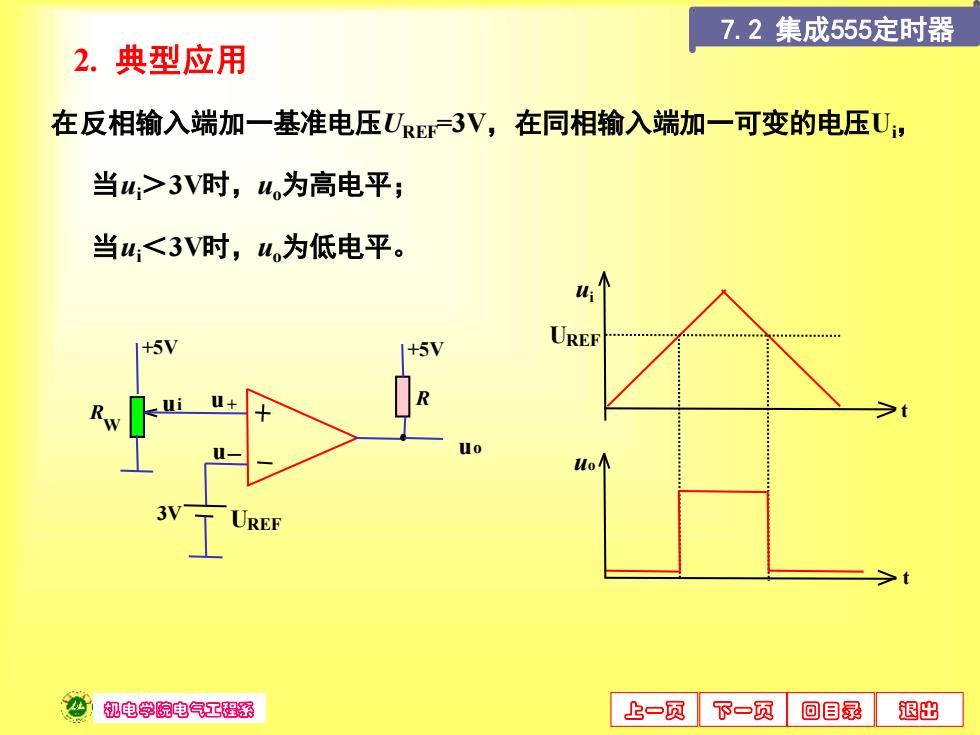

7.2集成555定时器 2.典型应用 在反相输入端加一基准电压U3V,在同相输入端加一可变的电压U, 当u>3V时,为高电平; 当u<3V时,为低电平。 UREF 机电学院电气工程系 上一页下-页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 在反相输入端加一基准电压UREF=3V,在同相输入端加一可变的电压Ui, 当ui>3V时,uo为高电平; 当ui<3V时,uo为低电平。 2. 典型应用 ui t UREF t uo u- o u + u +5V R R +5V 3V W UREF ui 7.2 集成555定时器

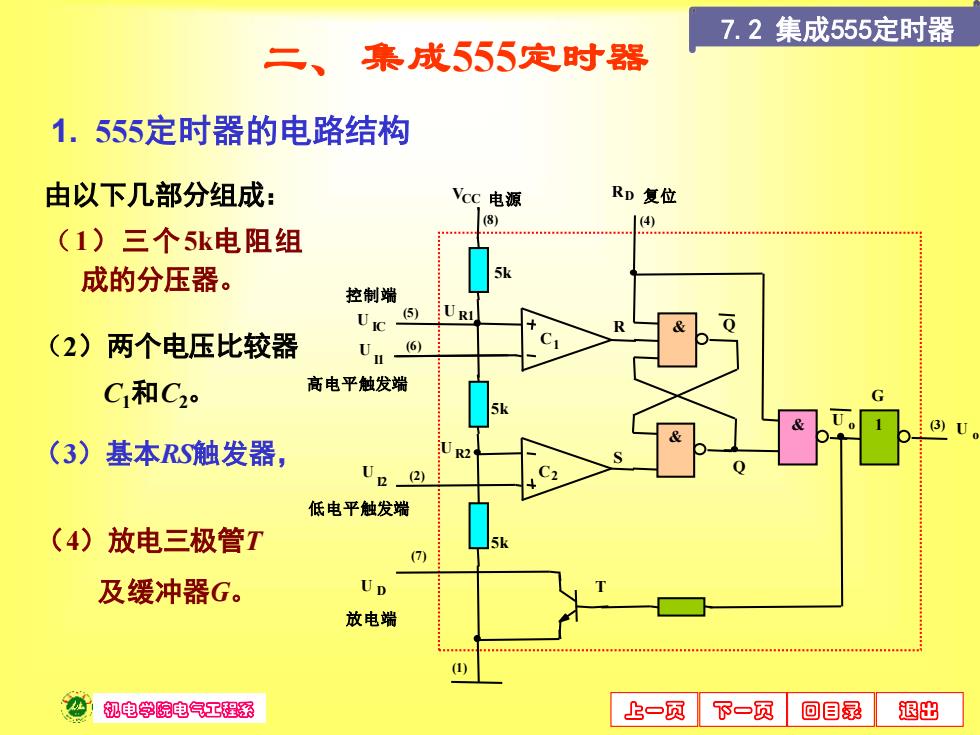

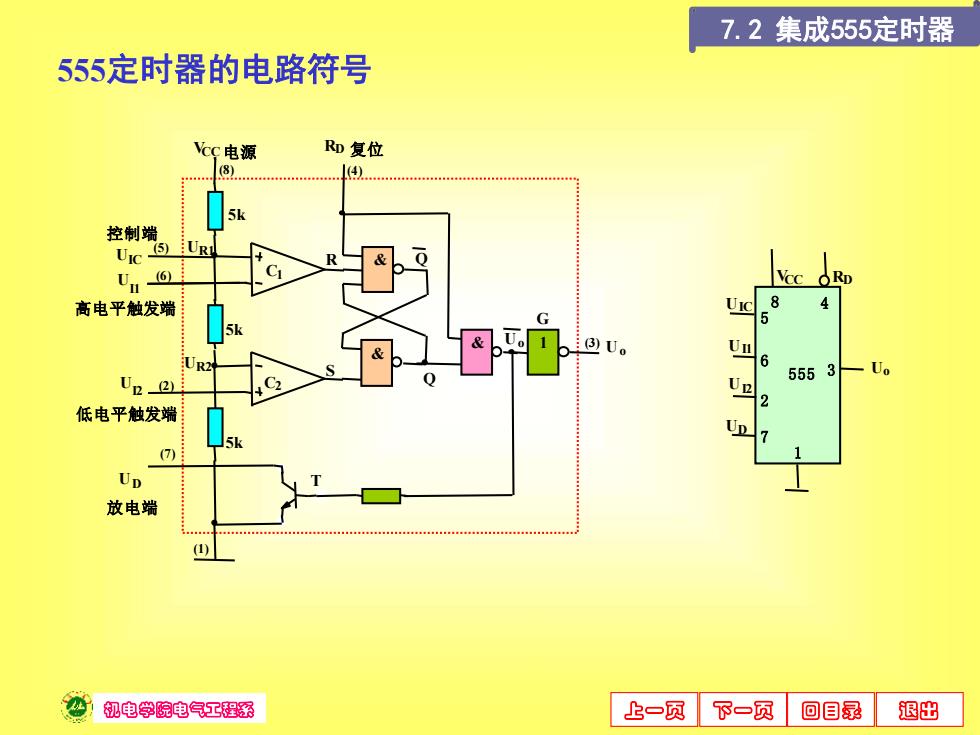

7.2集成555定时器 二、 集成555定时器 1.555定时器的电路结构 由以下几部分组成: VcC电源 RD复位 (8) 1(4) (1)三个5k电阻组 成的分压器。 控制端 UKC (5)URI (2)两个电压比较器 Un (6 C1和C20 高电平触发端 (3)基本RS触发器, 低电平触发端 (4)放电三极管T (7 及缓冲器G。 Up 放电端 机电学院电气工程系 上一页下一页回目绿退出

机电学院电气工程系 上一页 下一页 回目录 退出 二、 集成555定时器 由以下几部分组成: (1)三个5k电阻组 成的分压器。 (2)两个电压比较器 C1和C2。 1. 555定时器的电路结构 (3)基本RS触发器, (4)放电三极管T 及缓冲器G。 C C & & & 1 R S T G 5k 5k 5k 1 2 VCC RD I1 D (1) (7) (2) (6) (5) (8) (4) (3) 电源 复位 高电平触发端 控制端 低电平触发端 放电端 U I2 U U IC U U o U R1 U R2 Q Q U o 7.2 集成555定时器

7.2集成555定时器 555定时器的电路符号 VcC电源 RD复位 (8) 控制端 Uc包UR 0 Un VCC ORD 高电平触发端 8 UR2 Up C) Up 5553 低电平触发端 ⊙ Up 放电端 (1) 机电学院电气工程系 上一页 下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 1 2 6 5 8 4 3 7 I2 I1 IC VCC 555 RD Uo U U U UD C C & & & 1 R S T G 5k 5k 5k 1 2 VCC RD I1 D (1) (7) (2) (6) (5) (8) (4) (3) 电源 复位 高电平触发端 控制端 低电平触发端 放电端 U I2 U UIC U Uo UR1 UR2 Q Q Uo 555定时器的电路符号 7.2 集成555定时器