K康芯科技 EDA技术与VHDL 第3章 VHDL基础

EDA技术与VHDL 第3章 VHDL 基础 KX 康芯科技

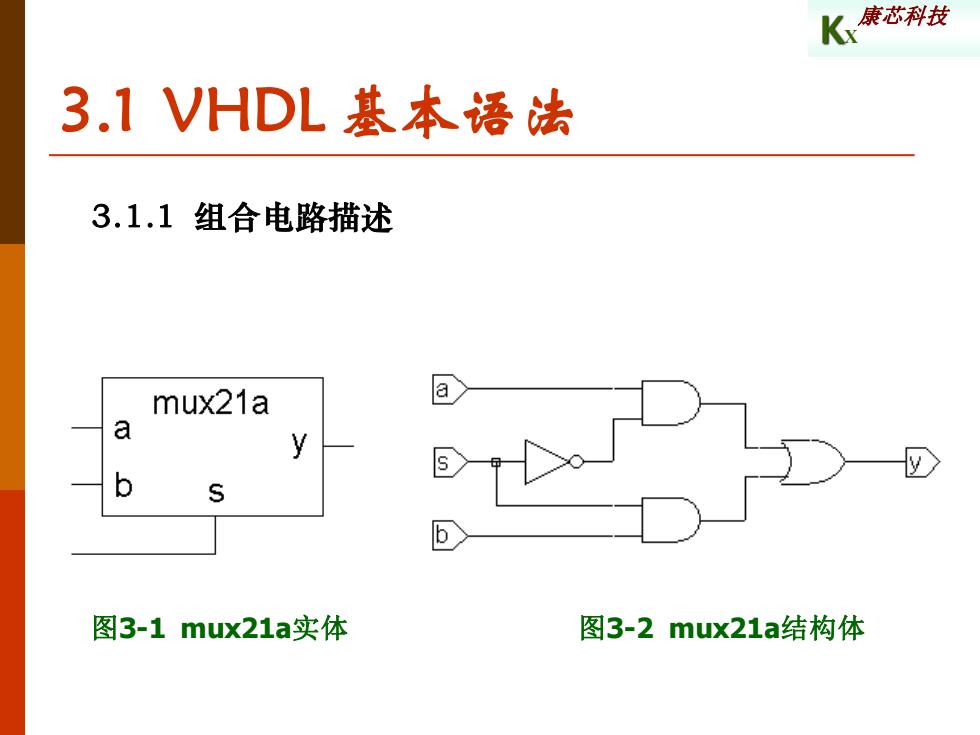

K能芯科技 3.1VHDL基本语法 3.1.1组合电路描述 mux21a y S 图3-1mux21a实体 图3-2mux21a结构体

KX 康芯科技 3.1 VHDL 基本语法 3.1.1 组合电路描述 图3-1 mux21a实体 图3-2 mux21a结构体

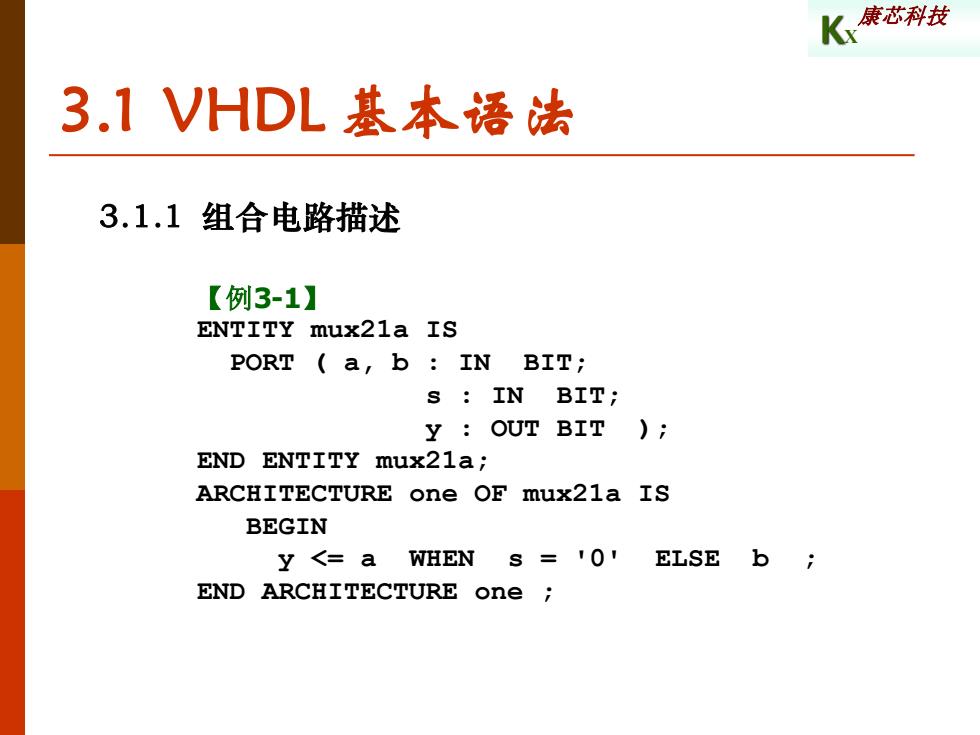

K康还科技 3.1VHDL基本语法 3.1.1组合电路描述 【例3-1】 ENTITY mux21a IS PORT(a,b:IN BIT; s IN BIT; y:OUT BIT ) END ENTITY mux21a; ARCHITECTURE one OF mux21a IS BEGIN y <a WHEN s=0 ELSE b; END ARCHITECTURE one

KX 康芯科技 3.1 VHDL 基本语法 3.1.1 组合电路描述 【例3-1】 ENTITY mux21a IS PORT ( a, b : IN BIT; s : IN BIT; y : OUT BIT ); END ENTITY mux21a; ARCHITECTURE one OF mux21a IS BEGIN y <= a WHEN s = '0' ELSE b ; END ARCHITECTURE one ;

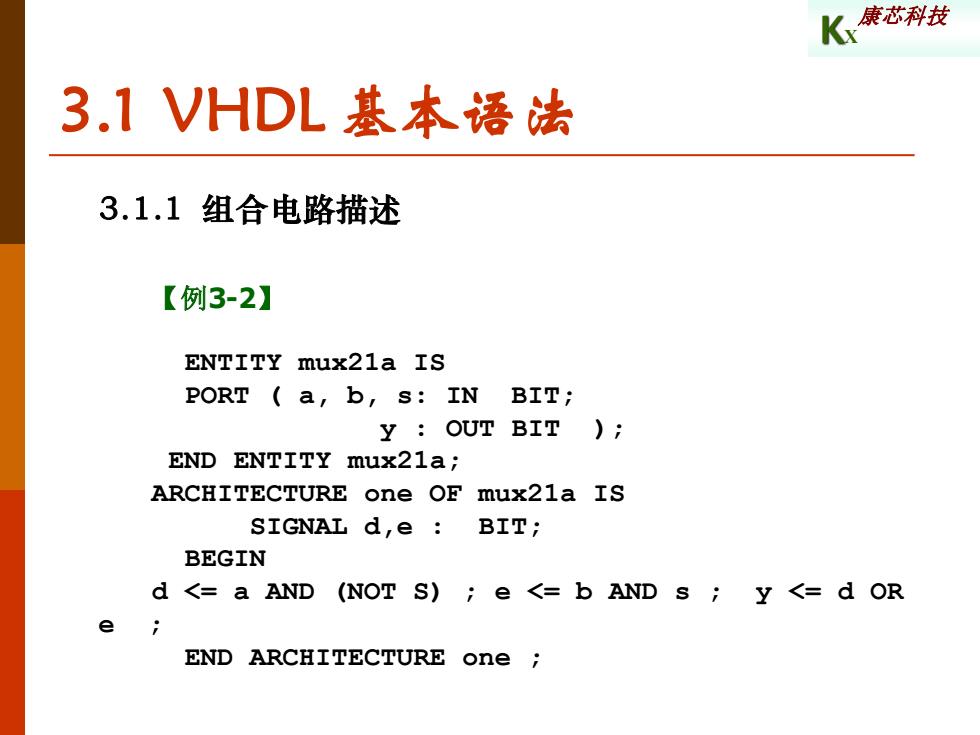

K能苏科技 3.1VHDL基本语法 3.1.1组合电路描述 【例3-2】 ENTITY mux21a IS PORT(a,b,S:IN BIT; y:OUT BIT ) END ENTITY mux21a; ARCHITECTURE one OF mux21a IS SIGNAL d,e:BIT; BEGIN d <-a AND (NOT S);e <-b AND s y <d OR e END ARCHITECTURE one;

KX 康芯科技 3.1 VHDL 基本语法 3.1.1 组合电路描述 【例3-2】 ENTITY mux21a IS PORT ( a, b, s: IN BIT; y : OUT BIT ); END ENTITY mux21a; ARCHITECTURE one OF mux21a IS SIGNAL d,e : BIT; BEGIN d <= a AND (NOT S) ; e <= b AND s ; y <= d OR e ; END ARCHITECTURE one ;

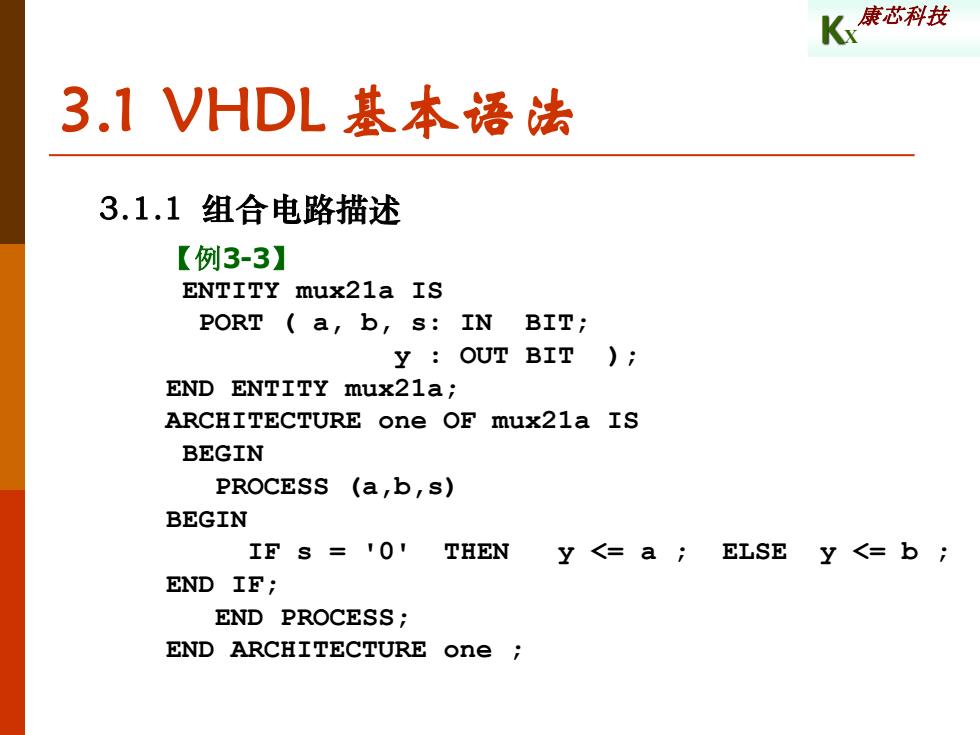

K康还科技 3.1VHDL基本语法 3.1.1组合电路描述 【例3-3】 ENTITY mux21a IS PORT a,b,s:IN BIT; y:OUT BIT ) END ENTITY mux21a; ARCHITECTURE one OF mux21a IS BEGIN PROCESS (a,b,s) BEGIN IF s =10'THEN y <a E工SEY<=b; END IF; END PROCESS; END ARCHITECTURE one;

KX 康芯科技 3.1 VHDL 基本语法 【例3-3】 ENTITY mux21a IS PORT ( a, b, s: IN BIT; y : OUT BIT ); END ENTITY mux21a; ARCHITECTURE one OF mux21a IS BEGIN PROCESS (a,b,s) BEGIN IF s = '0' THEN y <= a ; ELSE y <= b ; END IF; END PROCESS; END ARCHITECTURE one ; 3.1.1 组合电路描述

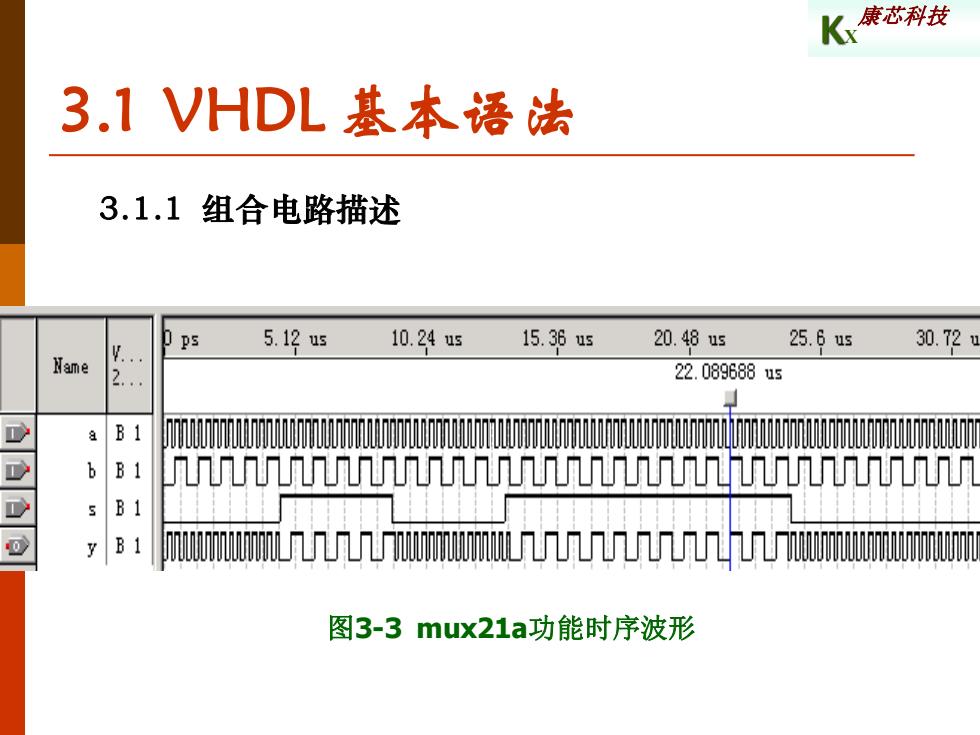

K黛芯科安 3.1VHDL基本语法 3.1.1组合电路描述 ps 5.12us 10.24us 15.36u5 20.48us 25.6us 30.72u Name 2. 22.089688us 8 B1 b B B 图3-3mux21a功能时序波形

KX 康芯科技 3.1 VHDL 基本语法 图3-3 mux21a功能时序波形 3.1.1 组合电路描述

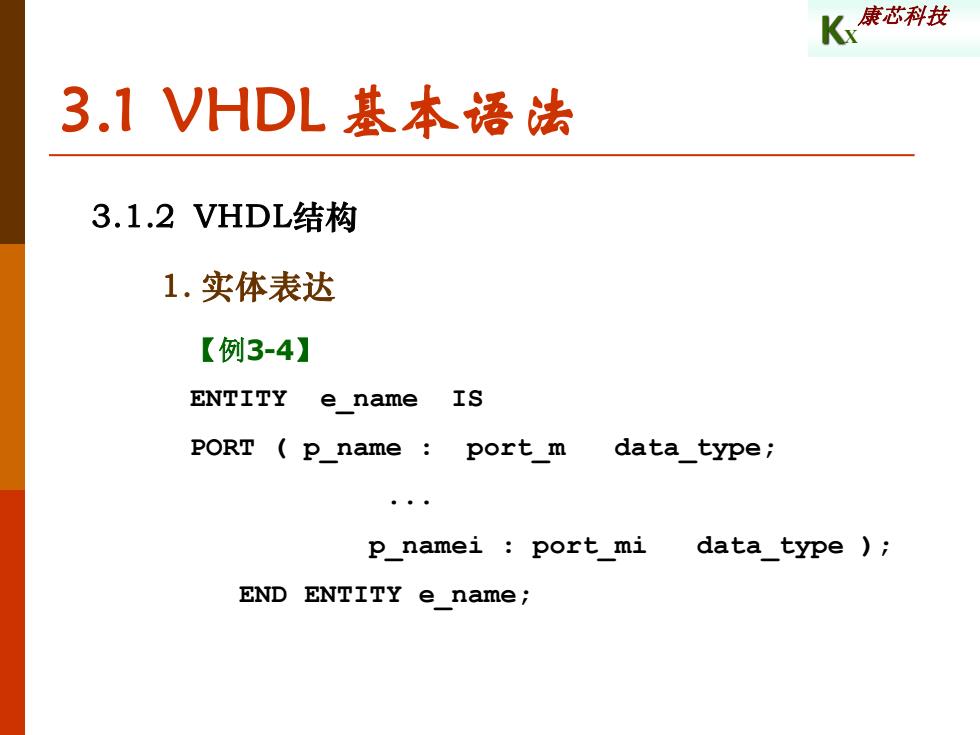

K康还科技 3.1VHDL基本语法 3.1.2VHDL结构 1.实体表达 【例3-4】 ENTITY e name IS PoRT(p_name:port_m data type; p namei port mi data type ) END ENTITY e name;

KX 康芯科技 3.1 VHDL 基本语法 3.1.2 VHDL结构 【例3-4】 ENTITY e_name IS PORT ( p_name : port_m data_type; . p_namei : port_mi data_type ); END ENTITY e_name; 1. 实体表达

K能苏科安 3.1VHDL基本语法 2.实体名 3.端口语句和端口信号名 4.端口模式 IN"、“OUTW、“INOUT、“BUFFER 5.数据类型

KX 康芯科技 3.1 VHDL 基本语法 2. 实体名 3. 端口语句和端口信号名 4. 端口模式 “IN”、“OUT”、“INOUT”、“BUFFER” 5. 数据类型

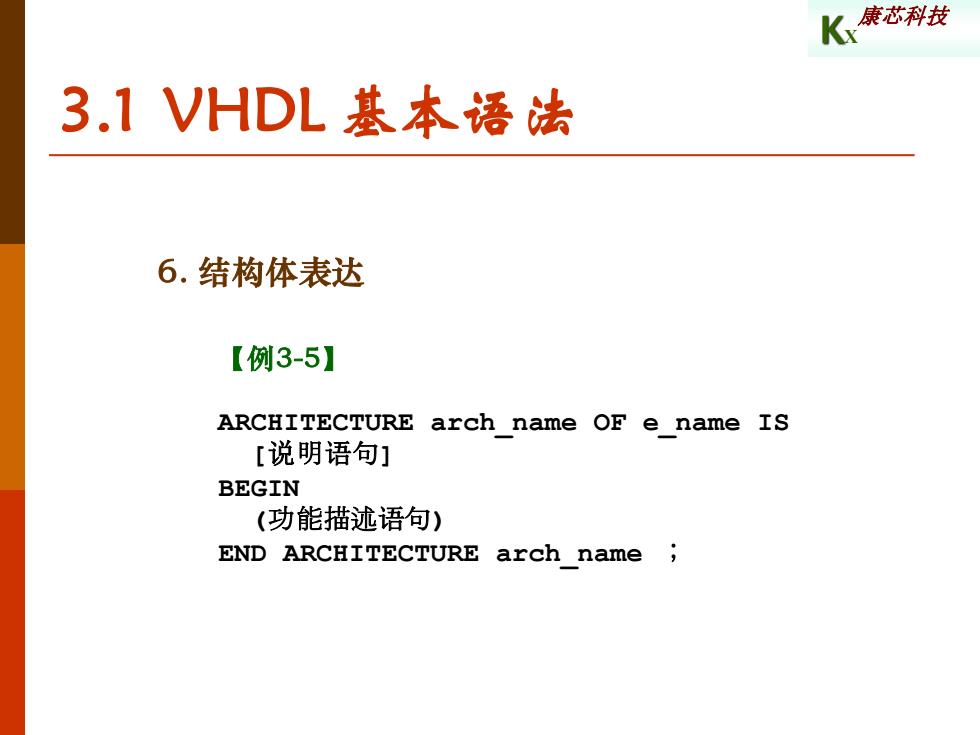

K康科技 3.1VHDL基本语法 6.结构体表达 【例3-5】 ARCHITECTURE arch name OF e name IS [说明语句] BEGIN (功能描述语句) END ARCHITECTURE arch name;

KX 康芯科技 3.1 VHDL 基本语法 6. 结构体表达 【例3-5】 ARCHITECTURE arch_name OF e_name IS [说明语句] BEGIN (功能描述语句) END ARCHITECTURE arch_name ;

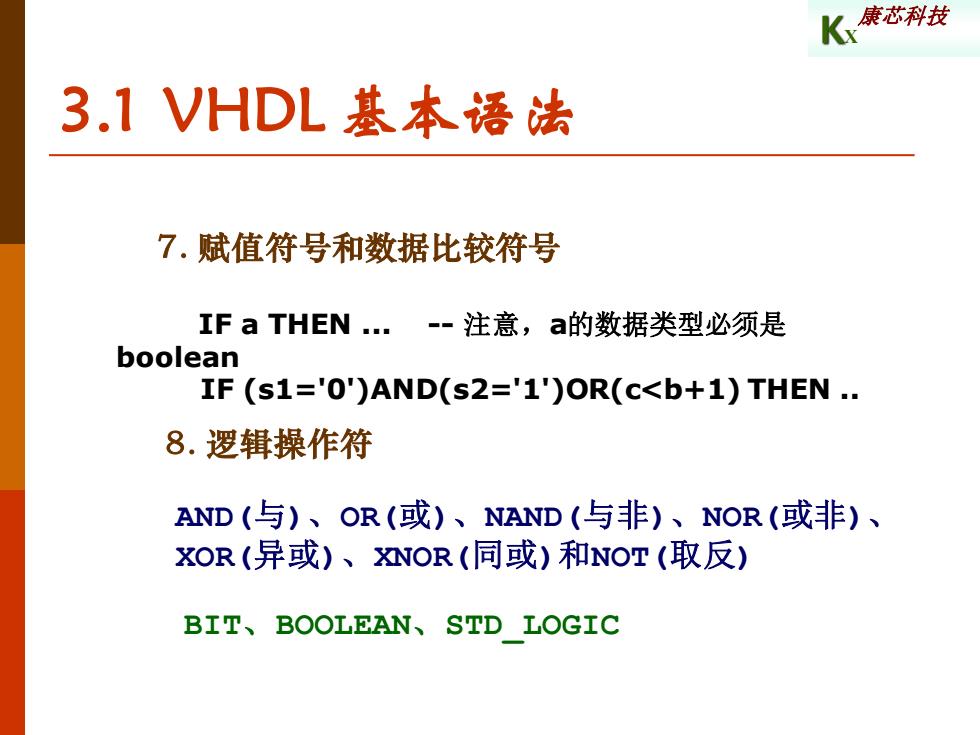

K能苏科数 3.1VHDL基本语法 7.赋值符号和数据比较符号 IF a THE.·-注意,a的数据类型必须是 boolean IF (s1='0')AND(s2='1')OR(c<b+1)THEN . 8.逻辑操作符 AND(与)、OR(或)、NAND(与非)、NOR(或非)、 XOR(异或)、NOR(同或)和NOT(取反) BIT、BOOLEAN、STD LOGIC

KX 康芯科技 3.1 VHDL 基本语法 7. 赋值符号和数据比较符号 IF a THEN . - 注意,a的数据类型必须是 boolean IF (s1='0')AND(s2='1')OR(c<b+1) THEN . 8. 逻辑操作符 BIT、BOOLEAN、STD_LOGIC AND(与)、OR(或)、NAND(与非)、NOR(或非)、 XOR(异或)、XNOR(同或)和NOT(取反)