K康芯科技 EDA技术与VHDL 第10章 DSP Builder设计深入

EDA技术与VHDL 第10章 DSP Builder设计深入 KX 康芯科技

K康科拉 10.1F1R数字滤波器设计 10.1.1FIR滤波器原理 M ()=6=* 10-1 k=0 L-1 y(n)= x0n-0h0 10-2 i=0 y(n)=x(n)*h(n) 10-3 h(n)=h(0)x(n)+h(1)x(n-1)+h(2)x(n-2)+h(3)x(n-3)10-4

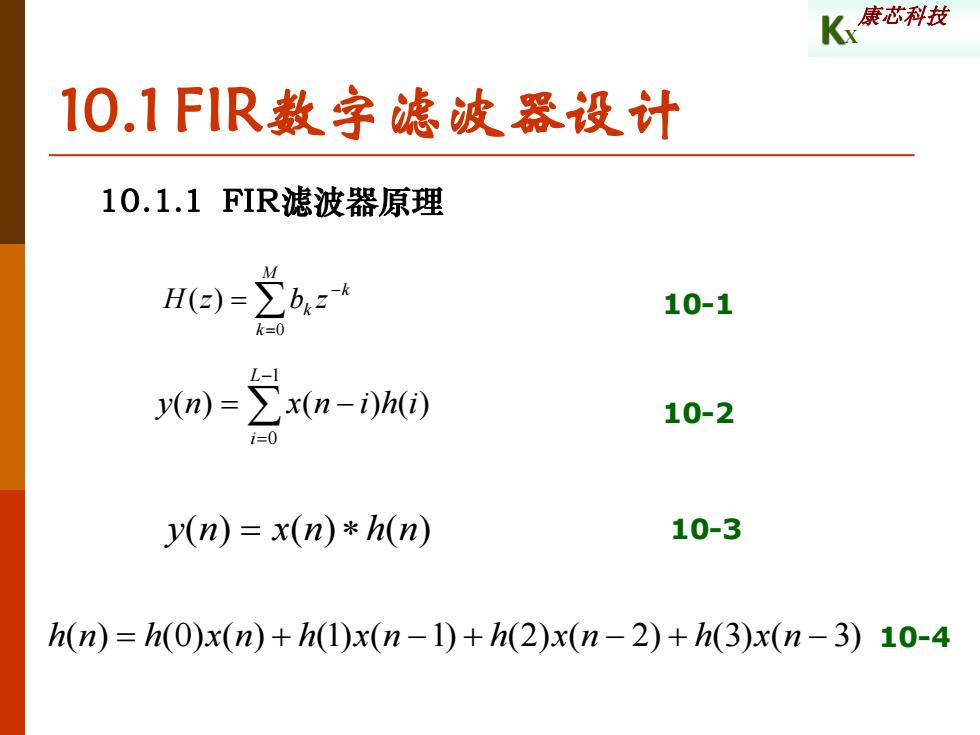

KX 康芯科技 10.1 FIR数字滤波器设计 10.1.1 FIR滤波器原理 = − = M k k k H z b z 0 ( ) − = = − 1 0 ( ) ( ) ( ) L i y n x n i h i y(n) = x(n) h(n) h(n) = h(0)x(n) + h(1)x(n −1) + h(2)x(n − 2) + h(3)x(n − 3) 10-1 10-2 10-3 10-4

K康还科技 10.1F1R数字滤波器设计 10.1.1FIR滤波器原理 x(n) 图10-13阶FIR滤波器结构 Ly(n)

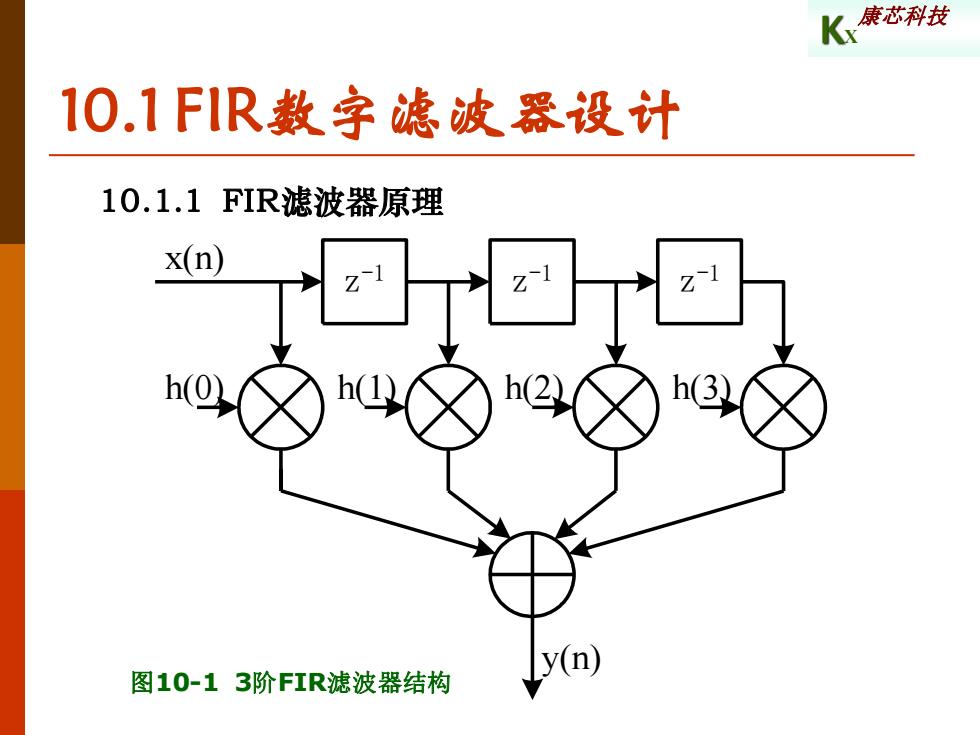

KX 康芯科技 10.1 FIR数字滤波器设计 10.1.1 FIR滤波器原理 z -1 z -1 z -1 x(n) h(0) h(1) h(2) h(3) y(n) 图10-1 3阶FIR滤波器结构

K能科拉 10.1F1R数字滤波器设计 10.1.2使用DSP Builder设计FIR滤波器 1.3阶常数系数FIR滤波器设计 h(n)=C,(h(0)x(n)+h(1)x(n-1)+h(2)x(n-2)+h(3)x(n-3) 10-5 h(0)=63 h(1)=127 h(2)=127 h(3)=63

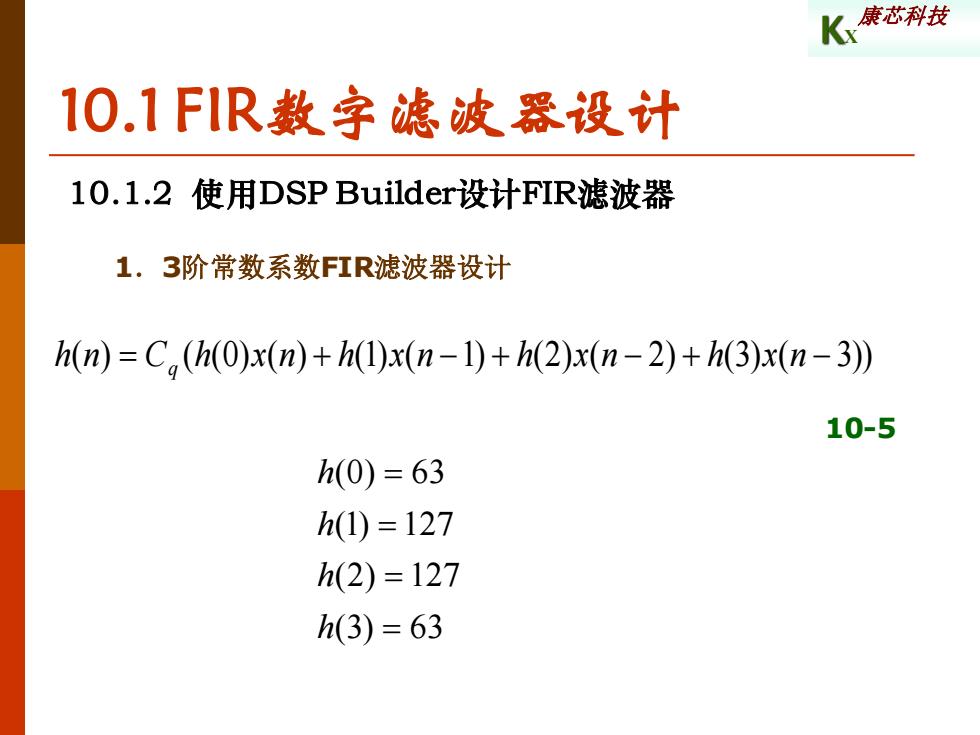

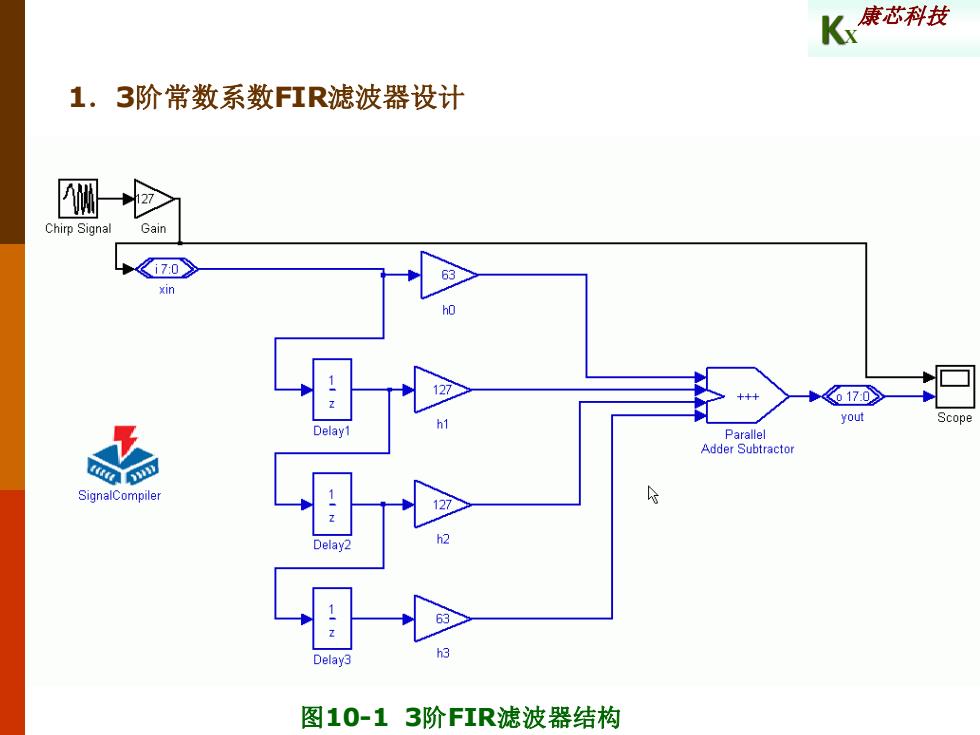

KX 康芯科技 10.1 FIR数字滤波器设计 10.1.2 使用DSP Builder设计FIR滤波器 1.3阶常数系数FIR滤波器设计 h(n) = C (h(0)x(n) + h(1)x(n −1) + h(2)x(n − 2) + h(3)x(n − 3)) q 10-5 (3) 63 (2) 127 (1) 127 (0) 63 = = = = h h h h

K 康芯科技 1.3阶常数系数FIR滤波器设计 Chirp Signal Gain 170 xin +++ +《0170 yout Scope Delay1 Parallel Adder Subtractor SignalCompiler Delay2 Delay3 图10-13阶FIR滤波器结构

KX 康芯科技 10.1.2 使用DSP Builder设计FIR滤波器 1.3阶常数系数FIR滤波器设计 图10-1 3阶FIR滤波器结构

K能在科拉 10.1F1R数字滤波器设计 10.1.2使用DSP Builder设计FIR滤波器 1.3阶常数系数FIR滤波器设计 Chirp Signal模块:(Chirp Signal) 库:Simulink中Sources库 参数“Initial Frequency(Hz)”设为“O.1” 参数“Target time'”设为“10 参数“Frequency at target time(Hz)”设为“1” 参数“Interpret vectors parameters as 1-D”选中 Gain模块:(Gain) 库:Simulink中Math Operations库 参数“Gain”设为“127” 参数“Multiplication”设为“Element wise(K.*u)” Scope模块:(Scope) 库:simulink中sinks库 参数“Number of Axes"为“2

KX 康芯科技 10.1 FIR数字滤波器设计 10.1.2 使用DSP Builder设计FIR滤波器 1.3阶常数系数FIR滤波器设计 Chirp Signal模块:(Chirp Signal) 库:Simulink中Sources库 参数“Initial Frequency(Hz)”设为“0.1” 参数“Target time”设为“10” 参数“Frequency at target time(Hz)”设为“1” 参数“Interpret vectors parameters as 1-D”选中 Gain模块:(Gain) 库:Simulink中Math Operations库 参数“Gain”设为“127” 参数“Multiplication”设为“Element wise(K.*u)” Scope模块:(Scope) 库:simulink中sinks库 参数“Number of Axes”为“2

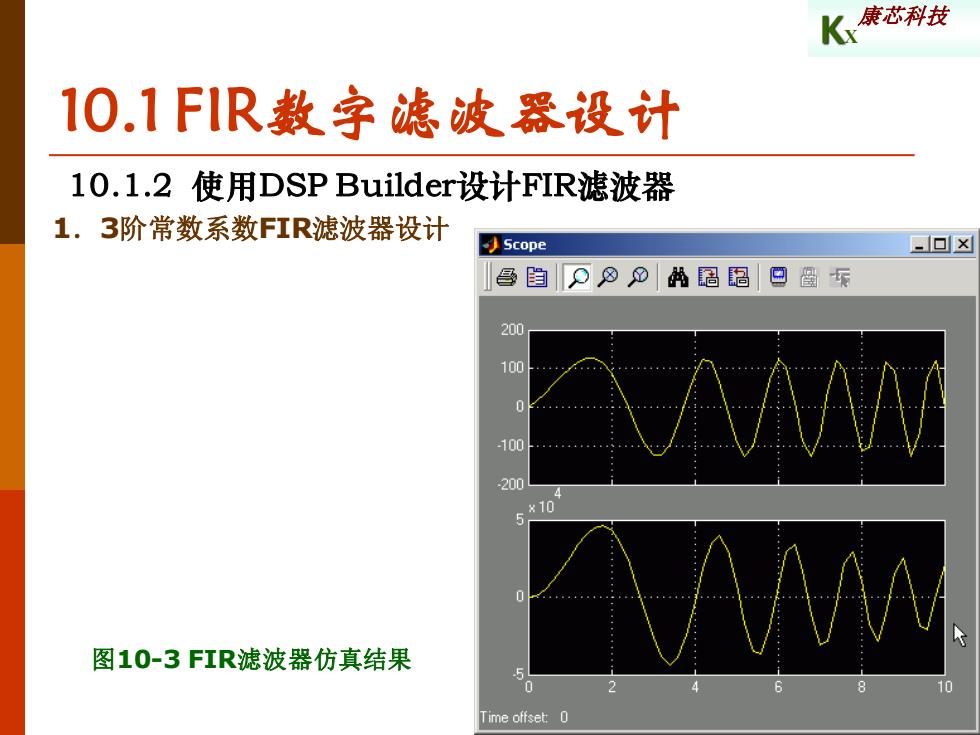

K 康芯科技 10.1F1R数字滤波器设计 10.1.2使用DSP Builder设计FIR滤波器 1.3阶常数系数FIR滤波器设计 Scope ▣x 昌自P的居图但盈 200 100 100 200 生 图10-3FIR滤波器仿真结果 Time offset:0

KX 康芯科技 10.1 FIR数字滤波器设计 10.1.2 使用DSP Builder设计FIR滤波器 1.3阶常数系数FIR滤波器设计 图10-3 FIR滤波器仿真结果

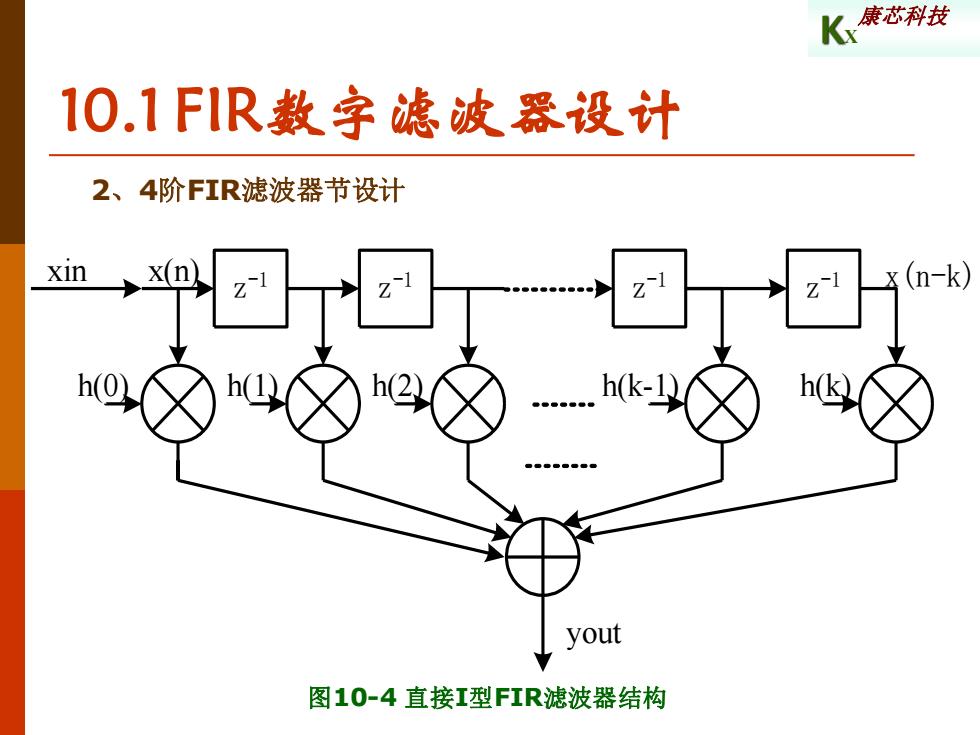

K能芯科我 10.1F1R数字滤波器设计 2、4阶FIR滤波器节设计 x(n (n-k) yout 图10-4直接I型FIR滤波器结构

KX 康芯科技 10.1 FIR数字滤波器设计 2、4阶FIR滤波器节设计 图10-4 直接I型FIR滤波器结构 z -1 z -1 z x(n) -1 h(0) h(1) h(2) h(k) yout xin z -1 h(k-1) x(n-k)

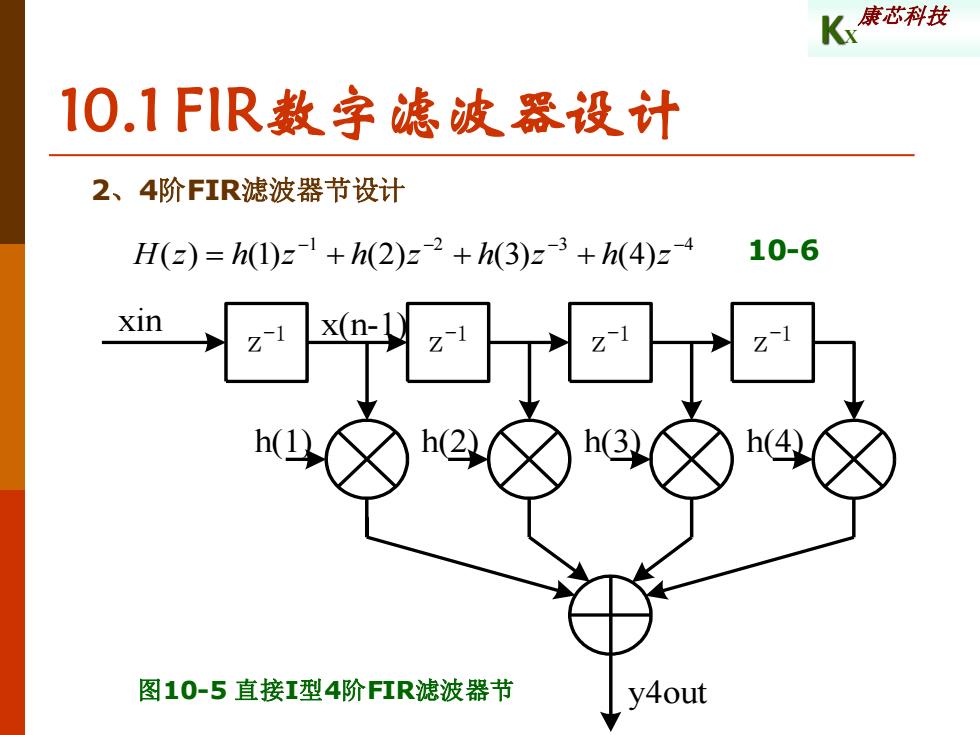

K 康芯科技 10.1F1R数字滤波器设计 2、4阶FIR滤波器节设计 H(z)=h(1)z+h(2)z2+h(3)z3+h(4)z4 10-6 Xin x(n-D 图10-5直接I型4阶FIR滤波器节 y4out

KX 康芯科技 z -1 z -1 z x(n-1) -1 h(1) h(2) h(3) h(4) y4out z -1 xin 10.1 FIR数字滤波器设计 2、4阶FIR滤波器节设计 图10-5 直接I型4阶FIR滤波器节 1 2 3 4 ( ) (1) (2) (3) (4) − − − − H z = h z + h z + h z + h z 10-6

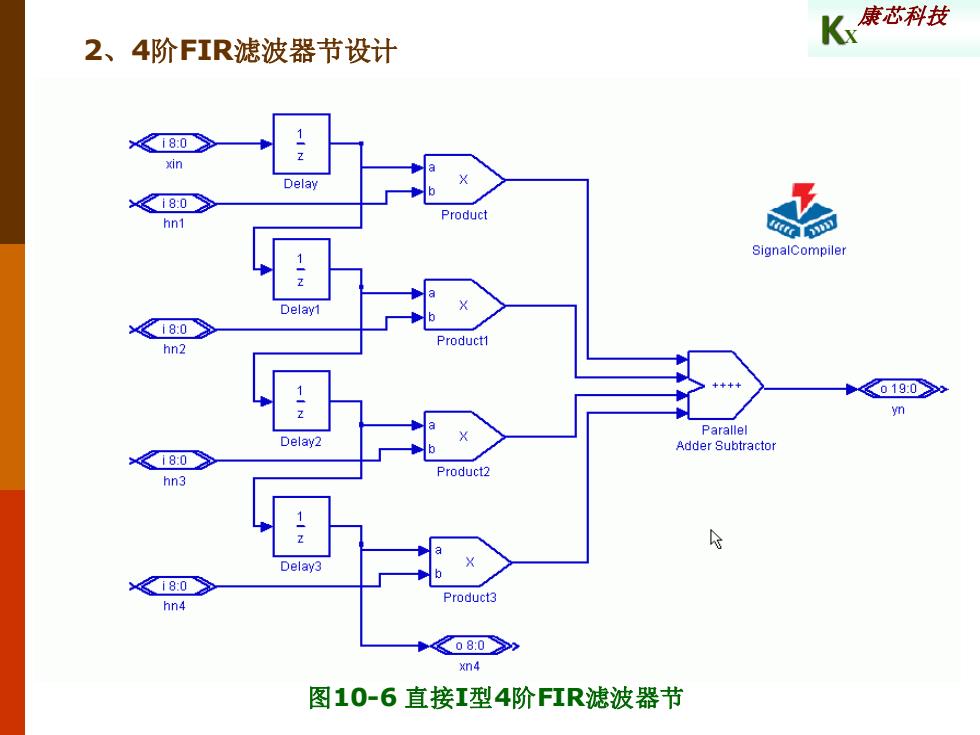

K能芯科我 2、4阶FIR滤波器节设计 180 xin Delay ≤180 Product hn1 SignalCompiler Delay1 《180 hn2 Product1 019:0 Parallel Delay2 Adder Subtractor >《80> Product2 hn3 Delay3 180 hn4 Product3 > xn4 图10-6直接I型4阶FIR滤波器节

KX 康芯科技 10.1 FIR数字滤波器设计 2、4阶FIR滤波器节设计 图10-6 直接I型4阶FIR滤波器节