第七章(选择、判断共30题) 一、选择题 1.同步计数器和异步计数器比较,同步计数器的显著优点是 A.工作速度高B.触发器利用率高C.电路简单D.不受时钟CP控制。 2.把一个五进制计数器与一个四进制计数器串联可得到进制计数器。 A.4 B.5 C.9 D.20 3.下列逻辑电路中为时序逻辑电路的是 A.变量译码器B.加法器C.数码寄存器D.数据选择器 4.N个触发器可以构成最大计数长度(进制数)为 的计数器。 A.N B.2N C.N2 D.2N 5.N个触发器可以构成能寄存位二进制数码的寄存器。 A.N-1 B.N C.N+1 D.2N 6.五个D触发器构成环形计数器,其计数长度为一 A.5 B.10 C.25 D.32 7.同步时序电路和异步时序电路比较,其差异在于后者一。 A.没有触发器 B.没有统一的时钟脉冲控制 C.没有稳定状态 D.输出只与内部状态有关 8.一位8421BCD码计数器至少需要个触发器。 A.3 B.4 C.5 D.10 9.欲设计0,1,2,3,4,5,6,7这几个数的计数器,如果设计合理,采用同 步二进制计数器,最少应使用级触发器。 A.2 B.3 C.4 D.8 10.8位移位寄存器,串行输入时经_个脉冲后,8位数码全部移入寄存器中。 A.1 B.2 C.4 D.8 11.用二进制异步计数器从0做加法,计到十进制数178,则最少需要_个 触发器。 A.2 B.6 C.7 D.8 E.10 12.某电视机水平-垂直扫描发生器需要一个分频器将31500Hz的脉冲转换为60Hz 的脉冲,欲构成此分频器至少需要个触发器。 A.10 B.60C.525 D.31500 13.某移位寄存器的时钟脉冲频率为100KHz,欲将存放在该寄存器中的数左移8

第七章(选择、判断共 30 题) 一、选择题 1.同步计数器和异步计数器比较,同步计数器的显著优点是 。 A .工作速度高 B .触发器利用率高 C .电路简单 D .不受时钟 C P 控制。 2.把一个五进制计数器与一个四进制计数器串联可得到 进制计数器。 A . 4 B . 5 C . 9 D . 2 0 3.下列逻辑电路中为时序逻辑电路的是 。 A .变量译码器 B .加法器 C .数码寄存器 D .数据选择器 4 . N 个触发器可以 构成最大计数长度(进制数)为 的计数器。 A . N B . 2 N C . N 2 D . 2 N 5 . N 个触发器可以构成能寄存 位二进制数码的寄存器。 A . N - 1 B . N C . N + 1 D . 2 N 6.五个 D 触发器构成环形计数器,其计数长度为 。 A . 5 B . 1 0 C . 2 5 D . 3 2 7.同步时序电路和异步时序电路比较,其差异在于后者 。 A .没有触发器 B .没有统一的时钟脉冲控制 C .没有稳定状态 D .输出只与内部状态有关 8.一位 8421BCD 码计数器至少需要 个触发器。 A . 3 B . 4 C . 5 D . 1 0 9 .欲设计 0, 1, 2, 3, 4, 5, 6, 7 这几个数的计数器,如果设计合理,采用同 步二进制计数器,最少应使用 级触发器。 A . 2 B . 3 C . 4 D . 8 1 0. 8 位 移 位 寄 存 器 , 串 行 输 入 时 经 个脉冲后,8 位数码全部移入寄存器中。 A . 1 B . 2 C . 4 D . 8 1 1.用二进制异步计数器从 0 做加法,计到十进制数 178,则最少需要 个 触发器。 A . 2 B . 6 C . 7 D . 8 E .10 1 2.某 电 视 机 水 平 -垂直扫描发生器需要一个分频器将 31500H Z 的脉冲转换为 60H Z 的脉冲,欲构成此分频器至少需要 个触发器。 A . 1 0 B . 6 0 C . 525 D . 31500 1 3.某 移 位 寄 存 器 的 时 钟 脉 冲 频 率 为 1 0 0KH Z ,欲 将 存 放 在 该 寄 存 器 中 的 数 左 移 8

位,完成该操作需要时间。 A.104SB.80μSC.100μS D.800ms 14.若用JK触发器米实现特性方程为Q=AQ”+AB,则JK端的方程为 A.J=AB,K=4+B B.J=AB,K=4B C.J=4+B,K=AB D.J=AB,K=AB 15.要产生10个顺序脉冲,若用四位双向移位寄存器CT74LS194来实现,需要」 片 A.3 B.4 C.5 D.10 16.若要设计一个脉冲序列为1101001110的序列脉冲发生器,应选用个触 发器。 A.2 B.3 C.4 D.10 二、判断题(正确打√,错误的打X) 1.同步时序电路由组合电路和存储器两部分组成。() 2.组合电路不含有记忆功能的器件。() 3.时序电路不含有记忆功能的器件。() 4.同步时序电路具有统一的时钟CP控制。() 5.异步时序电路的各级触发器类型不同。() 6.环形计数器在每个时钟脉冲CP作用时,仅有一位触发器发生状态更新。() 7.环形计数器如果不作自启动修改,则总有孤立状态存在。() 8.计数器的模是指构成计数器的触发器的个数。() 9.计数器的模是指对输入的计数脉冲的个数。() 10.D触发器的特征方程Qn+1=D,而与Q无关,所以,D触发器不是时序电路。() 11.在同步时序电路的设计中,若最简状态表中的状态数为2,而又是用N级 触发器来实现其电路,则不需检查电路的自启动性。() 12.把一个5进制计数器与一个10进制计数器串联可得到15进制计数器。() 13.同步二进制计数器的电路比异步二进制计数器复杂,所以实际应用中较少使 用同步二进制计数器。() 14,利用反馈归零法获得N进制计数器时,若为异步置零方式,则状态SN只是 短暂的过渡状态,不能稳定而是立刻变为0状态。() 三、填空题 1.寄存器按照功能不同可分为两类:」 寄存器和 寄存器。 2.数字电路按照是否有记忆功能通常可分为两类:

位,完成该操作需要 时间。 A . 1 0μ S B .80μ S C .100μ S D .800ms 14.若 用 J K 触发器来实现特性方程为 Q AQ AB n 1 n = + + , 则 J K 端的方程为 。 A . J=AB, K = A + B B . J=AB, K = AB C . J = A + B , K = A B D . J = AB , K=AB 15.要产生 10 个顺序脉冲,若用四位双向移位寄存器 CT74LS194 来实现,需要 片。 A . 3 B . 4 C . 5 D . 1 0 1 6.若要设计一个脉冲序列为 1101001110 的序列脉冲发生器,应选用 个 触 发器。 A . 2 B . 3 C . 4 D . 1 0 二、判断题(正确打√,错误的打×) 1.同步时序电路由组合电路和存储器两部分组成。( ) 2.组合电路不含有记忆功能的器件。( ) 3.时序电路不含有记忆功能的器件。( ) 4.同步时序电路具有统一的时钟 CP 控制。( ) 5.异步时序电路的各级触发器类型不同。( ) 6.环形计数器在每个时钟脉冲 CP 作用时,仅有一位触发器发生状态更新。( ) 7.环形计数器如果不作自启动修改,则总有孤立状态存在。( ) 8.计数器的模是指构成计数器的触发器的个数。( ) 9.计数器的模是指对输入的计数脉冲的个数。( ) 10.D 触发器的特征方程 Q n + 1 = D, 而 与 Q n 无关,所以, D 触 发 器 不 是 时 序 电 路 。( ) 1 1.在同步时序电路的设计中,若最简状态表中的 状态数为 2 N ,而又是用 N 级 触 发 器 来 实 现 其 电 路 , 则 不 需 检 查 电 路 的 自 启 动 性 。( ) 12.把一个 5 进制计数器与一个 10 进制计数器串联可得到 15 进 制 计 数 器 。( ) 1 3.同 步 二 进 制 计 数 器 的 电 路 比 异 步 二 进 制 计 数 器 复 杂 ,所 以 实 际 应 用 中 较 少 使 用 同 步 二 进 制 计 数 器 。( ) 1 4.利用反馈归零法获得 N 进制计数器时,若为异步置零方式,则状态 S N 只 是 短暂的过渡状态,不能稳定而是立刻变为 0 状 态 。( ) 三、填空题 1.寄存器按照功能不同可分为两类: 寄存器和 寄存器。 2.数字电路按照是否有记忆功能通常可 分为两类: 、

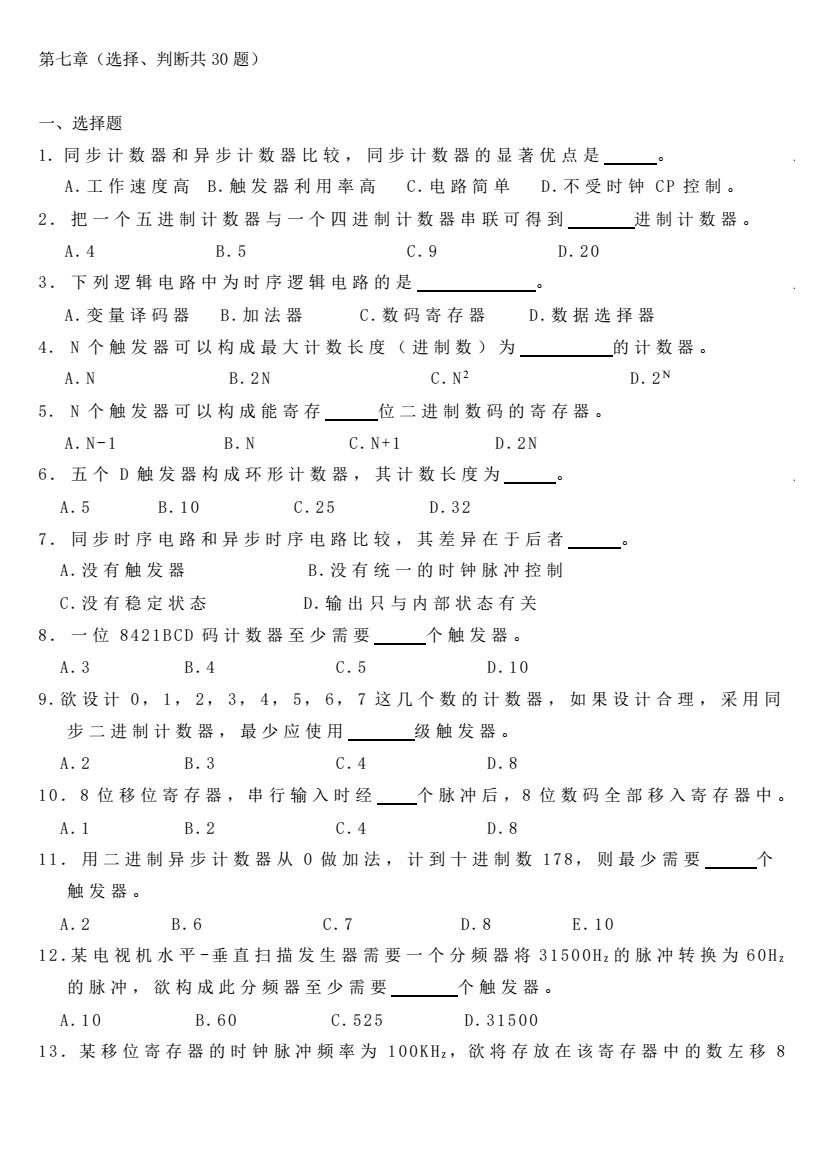

3。由四位移位寄存器构成的顺序脉冲发生器可产生个顺序脉冲。 4.时序逻辑电路按照其触发器是否有统一的时钟控制分为时序电路和 时序电路。 四、简答题 1.说明时序电路和组合电路在逻辑功能和电路结构上有何不同。 解:包含触发器的数字电路称为时序电路,任何时刻的输出不仅取决于当前的输入,同时也取决于 过去的输入序列,即时序电路具有对过去事件的记忆能力:仅包含门电路的数字电路称为组合电路,其 输出仅取决于当前的输入。 2.为什么组合电路用逻辑函数就可以表示其逻辑功能,而时序电路则用驱动方程、状态方程、输 出方程才能表示其功能? 解:因为组合电路的输出只与当前的输入有关,因此用逻辑函数就可以表示其逻辑功能:而时序电 路任何时刻的输出不仅取决于当前的输入,同时也取决于过去的输入序列,因此需要用驱动方程、状态 方程、输出方程才能表示其功能。 3.试分析图下所示的两个电路,哪一个为时序电路?为什么? (a) (b) 解:根据上图可以写出 F=AB+A+C=AB+A+AC.B=AB.A-AC.B=AB(A+C)B=ABC F ABF;.ABF:AB.4.B=ABF:+ABF.AB+4.B=ABF +AB+4.B AB(F"+1)+4.B=AB+AB 从F1、F,表达式看出图(a)图的输出F1不仅和输入有关,而且和中间变量C有关,所以()图为时 序电路。F2只与输入A、B有关,故图(b)为组合电路。 4.试分析下图所示电路的功能。要求写出驱动方程、状态方程、输出方程,画出状态转换图并对 逻辑功能作出说明。 解:由图可以写出 1是 Q6+1=D=Q6

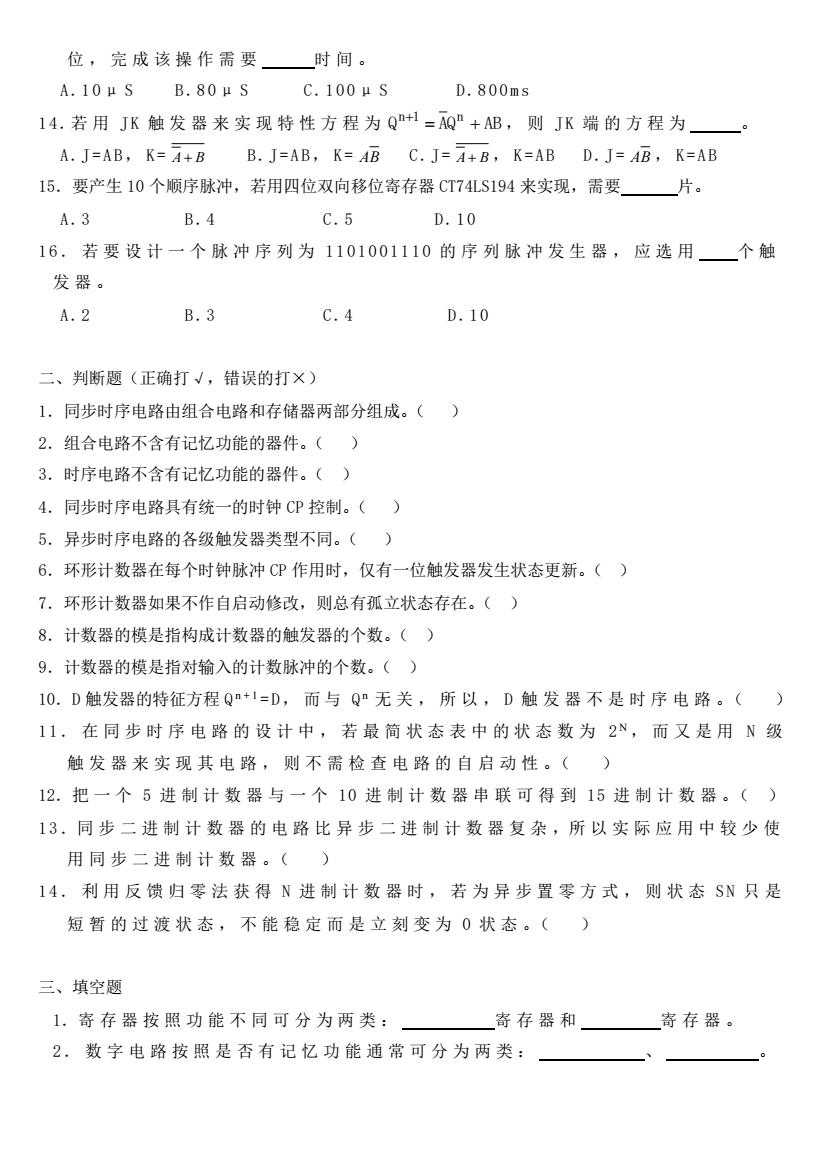

3.由四位移位寄存器构成的顺序脉冲发生器可产生 个顺序脉冲。 4.时序逻辑电路按照其触发器是否有统一的时钟控制分为 时序电路和 时序电路。 四、简答题 1.说明时序电路和组合电路在逻辑功能和电路结构上有何不同。 解:包含触发器的数字电路称为时序电路,任何时刻的输出不仅取决于当前的输入,同时也取决于 过去的输入序列,即时序电路具有对过去事件的记忆能力;仅包含门电路的数字电路称为组合电路,其 输出仅取决于当前的输入。 2.为什么组合电路用逻辑函数就可以表示其逻辑功能,而时序电路则用驱动方程、状态方程、输 出方程才能表示其功能? 解:因为组合电路的输出只与当前的输入有关,因此用逻辑函数就可以表示其逻辑功能;而时序电 路任何时刻的输出不仅取决于当前的输入,同时也取决于过去的输入序列,因此需要用驱动方程、状态 方程、输出方程才能表示其功能。 3.试分析图下所示的两个电路,哪一个为时序电路?为什么? 解:根据上图可以写出 F1 = AB + A+C = AB + A+ AC B = AB A AC B = AB(A+C)B = ABC AB F A B AB AB F ABF ABF AB A B ABF ABF AB A B ABF AB A B n n n n n n = + + = + = = + + = + + ( 1) 2 2 2 2 2 2 2 从 F1、F2 表达式看出图 (a)图的输出 F1 不仅和输入有关,而且和中间变量 C 有关,所以(a)图为时 序电路。F2 只与输入 A、B 有关,故图(b)为组合电路。 4.试分析下图所示电路的功能。要求写出驱动方程、状态方程、输出方程,画出状态转换图并对 逻辑功能作出说明。 解:由图可以写出 n n Q D0 Q0 1 0 = = +

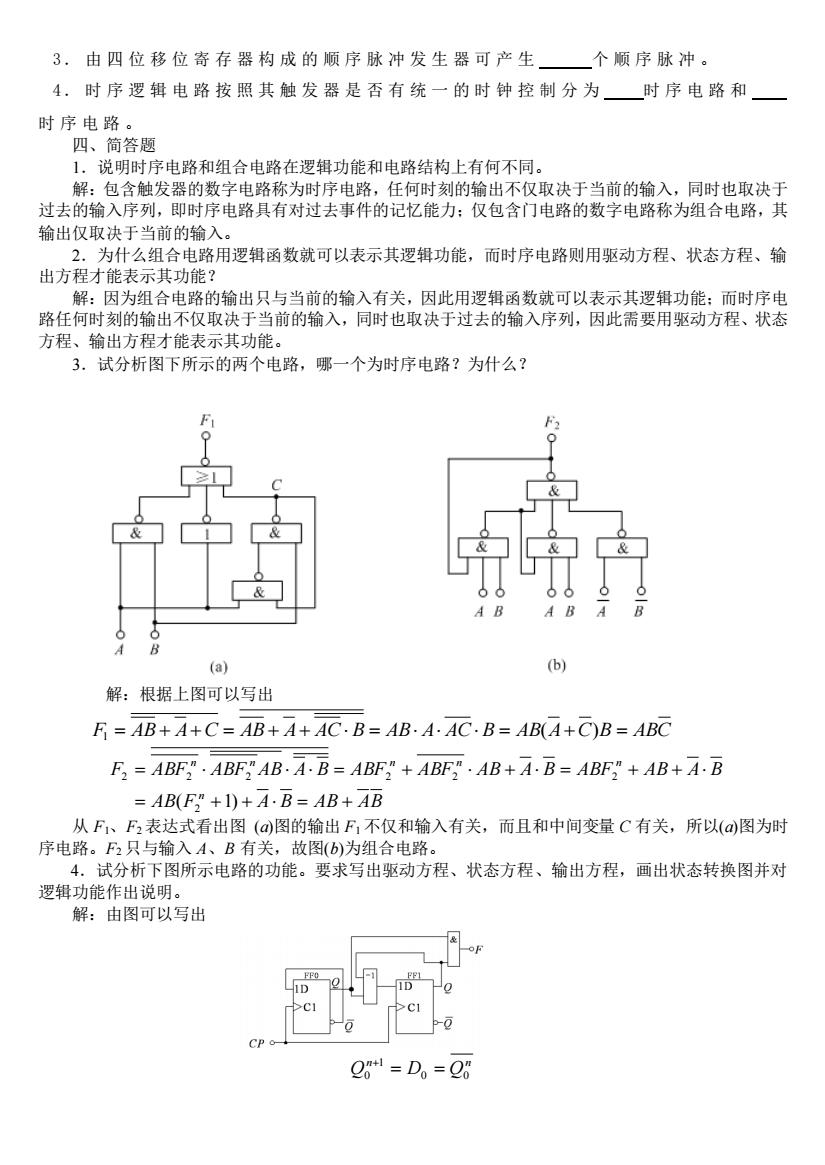

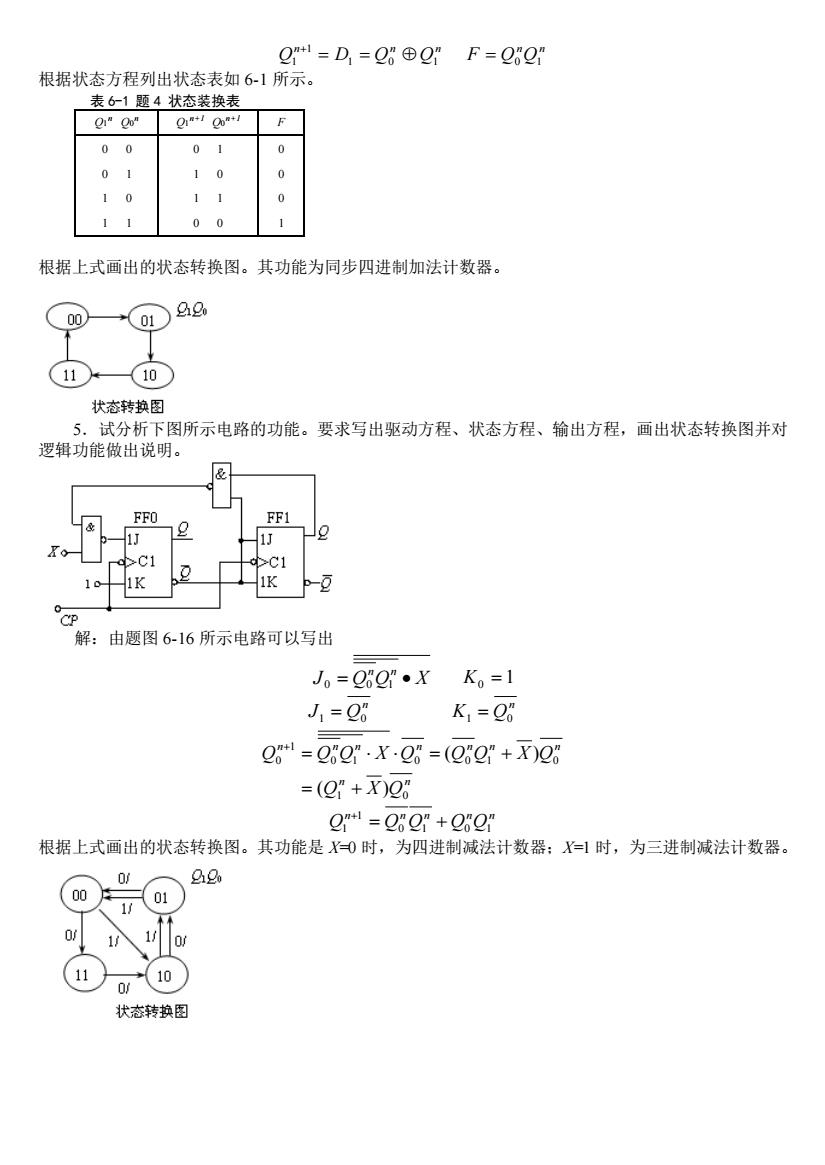

Q1=D,=Q8⊕2F=Q621 根据状态方程列出状态表如61所示。 表女1题4状态装换表 ++F 00 01 0 01 10 11 0 00 根据上式画出的状态转换图。其功能为同步四进制加法计数器。 00 (019g 1110 状态转换图 5.试分析下图所示电路的功能。要求写出驱动方程、状态方程、输出方程,画出状态转换图并对 逻辑功能做出说明。 10 -1K 解:由题图616所示电路可以写出 J=Q5grxK。=1 J1=06 K=0 Q=Qg”·X.Q6=(g6g”+X)0 =(g+X)g. Q1=Q62+Q60" 根据上式画出的状态转换图。其功能是0时,为四进制减法计数器:X=1时,为三进制减法计数器。 、9 状态转换图

n n n Q D1 Q0 Q1 1 1 = = + n n F = Q0 Q1 根据状态方程列出状态表如 6-1 所示。 表 6-1 题 4 状态装换表 Q1 n Q0 n Q1 n+1 Q0 n+1 F 0 0 0 1 1 0 1 1 0 1 1 0 1 1 0 0 0 0 0 1 根据上式画出的状态转换图。其功能为同步四进制加法计数器。 5.试分析下图所示电路的功能。要求写出驱动方程、状态方程、输出方程,画出状态转换图并对 逻辑功能做出说明。 解:由题图 6-16 所示电路可以写出 J Q Q X n n = • 0 0 1 K0 = 1 n J1 = Q0 n K1 = Q0 n n n n n n n n n Q X Q Q Q Q X Q Q Q X Q 1 0 0 1 0 0 1 0 1 0 ( ) ( ) = + = = + + n n n n n Q Q0 Q1 Q0 Q1 1 1 = + + 根据上式画出的状态转换图。其功能是 X=0 时,为四进制减法计数器;X=1 时,为三进制减法计数器