数字电子技术Digital Electronics Technology 第四章组合逻辑电路 石河子大学《数字电子枝术》裸程祖 电 活:0993-2057237 电子邮箱:rl mac@shzu.edu.cn 机电学院电气工程系 上一页下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 第四章 组合逻辑电路 数字电子技术Digital Electronics Technology 石河子大学《数字电子技术》课程组 电 话:0993-2057237 电子邮箱:rl_mac@shzu.edu.cn

4.1组合逻辑电路的分析方法与设计方法 4.2编码器 4.3译码器 4.4数据选择器 4.5数值比较器 4.6加法器 4.7组合逻辑电路中的竞争冒险 4.8组合逻辑电路的VHDL描述 少机电学院电气工程系 上一页下一页回目绿 退出

机电学院电气工程系 上一页 下一页 回目录 退出 4.4 数据选择器 4.3 译码器 4.5 数值比较器 4.6 加法器 4.2 编码器 4.1 组合逻辑电路的分析方法与设计方法 4.7 组合逻辑电路中的竞争冒险 4.8 组合逻辑电路的VHDL描述

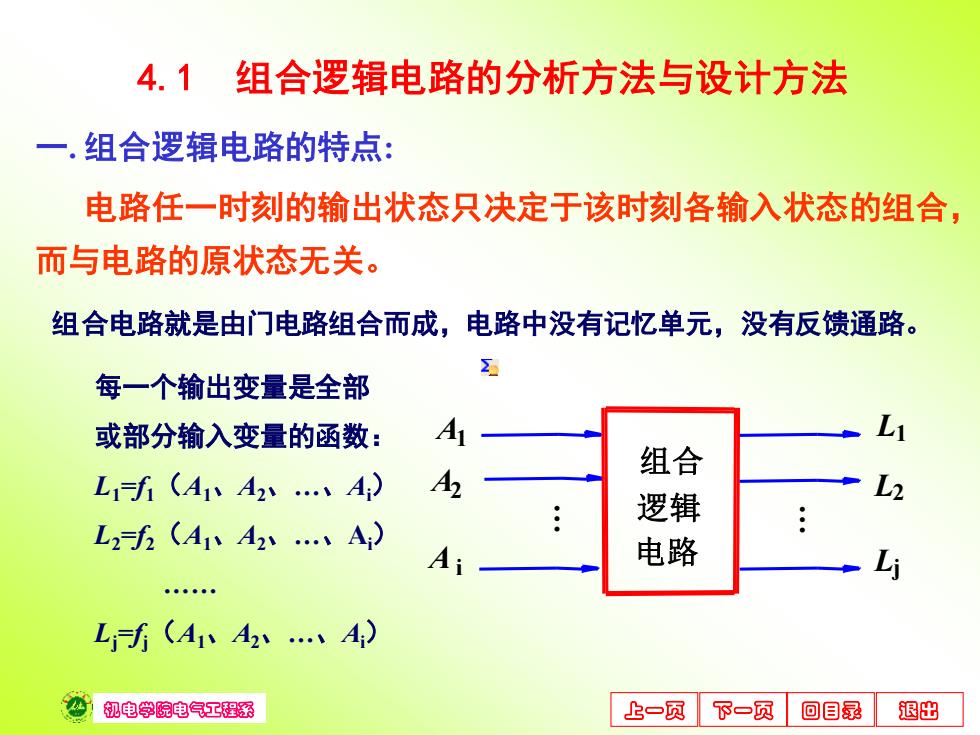

4.1组合逻辑电路的分析方法与设计方法 一.组合逻辑电路的特点: 电路任一时刻的输出状态只决定于该时刻各输入状态的组合, 而与电路的原状态无关。 组合电路就是由门电路组合而成,电路中没有记忆单元,没有反馈通路。 每一个输出变量是全部 或部分输入变量的函数: A 组合 L1=f(A1小A2NA) A 逻辑 L L2f(A1A2、A) Ai 电路 Li Lf(A1A2、A) 心祝电袋院电气工避繇 上一页下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 4.1 组合逻辑电路的分析方法与设计方法 每一个输出变量是全部 或部分输入变量的函数: L1=f1(A1、A2、.、Ai) L2=f2(A1、A2、.、Ai) . Lj=fj(A1、A2、.、Ai) 一. 组合逻辑电路的特点: 电路任一时刻的输出状态只决定于该时刻各输入状态的组合, 而与电路的原状态无关。 组合电路就是由门电路组合而成,电路中没有记忆单元,没有反馈通路。 . . 组合 逻辑 电路 A1 A2 Ai L1 L2 Lj

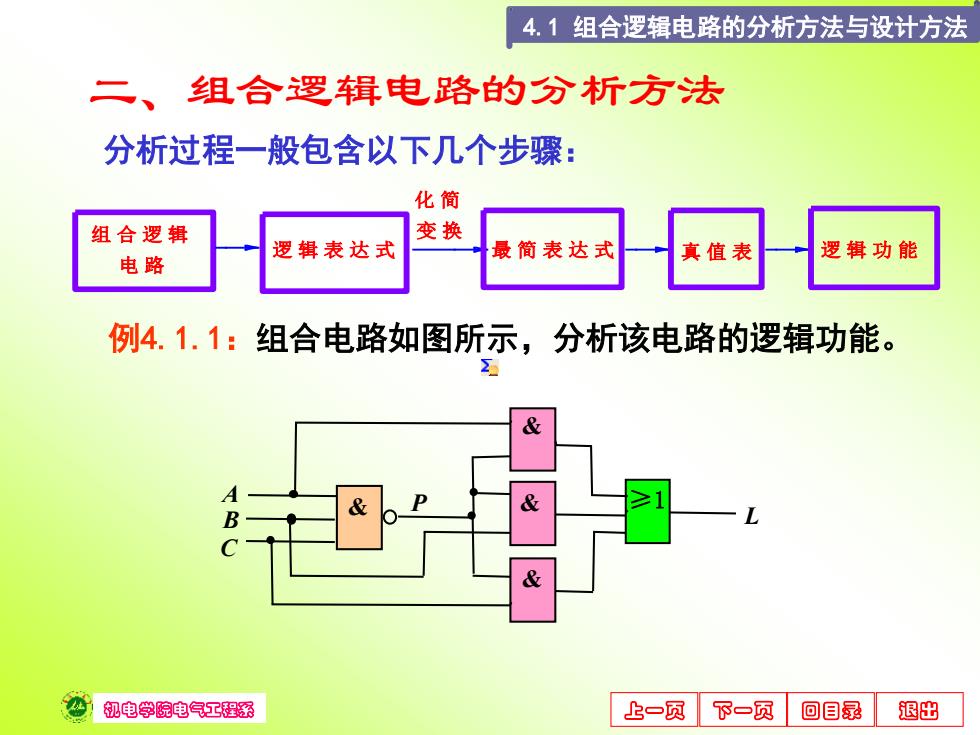

4.1组合逻辑电路的分析方法与设计方法 二、组合逻辑电路的分析方法 分析过程一般包含以下几个步骤: 化简 组合逻辑 变换 逻辑表达式 最简表达式 逻辑功能 电路 真值表 例4.1.1:组合电路如图所示,分析该电路的逻辑功能。 少饥电学院电气工程系 上一页下一页回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 二、组合逻辑电路的分析方法 例4.1.1:组合电路如图所示,分析该电路的逻辑功能。 组合逻辑 电 路 逻辑表达式 最简表达式 真值表 逻辑功能 化 简 变 换 分析过程一般包含以下几个步骤: 4.1 组合逻辑电路的分析方法与设计方法 & & & & A ≥1 B C L P

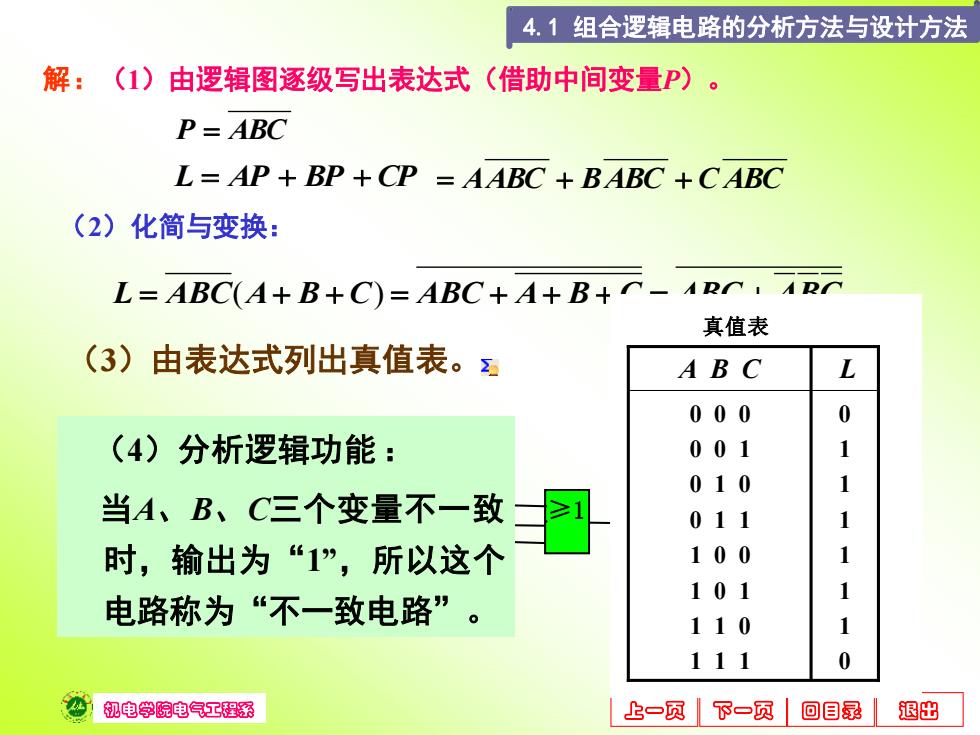

4.1组合逻辑电路的分析方法与设计方法 解:(1)由逻辑图逐级写出表达式(借助中间变量P)。 P=ABC L=AP+BP+CP =AABC BABC +CABC (2)化简与变换: L=ABC(A+B+C)=ABC+A+B+C-RCRC 真值表 (3)由表达式列出真值表。 ABC L 000 0 (4)分析逻辑功能: 001 1 010 当A、B、C三个变量不一致 011 1 时,输出为“1”,所以这个 100 1 101 电路称为“不一致电路”。 110 1 111 0 机电学院电气工程系 上一页|下一页|回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 & & & & A ≥1 B C L P (3)由表达式列出真值表。 P = ABC L = AP + BP + CP = AABC + BABC + C ABC L = ABC(A+ B + C) = ABC + A+ B + C = ABC + ABC (4)分析逻辑功能: 当A、B、C三个变量不一致 时,输出为“1” ,所以这个 电路称为“不一致电路” 。 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 A B C 0 1 1 1 1 1 1 0 L 真值表 解:(1)由逻辑图逐级写出表达式(借助中间变量P)。 (2)化简与变换: 4.1 组合逻辑电路的分析方法与设计方法

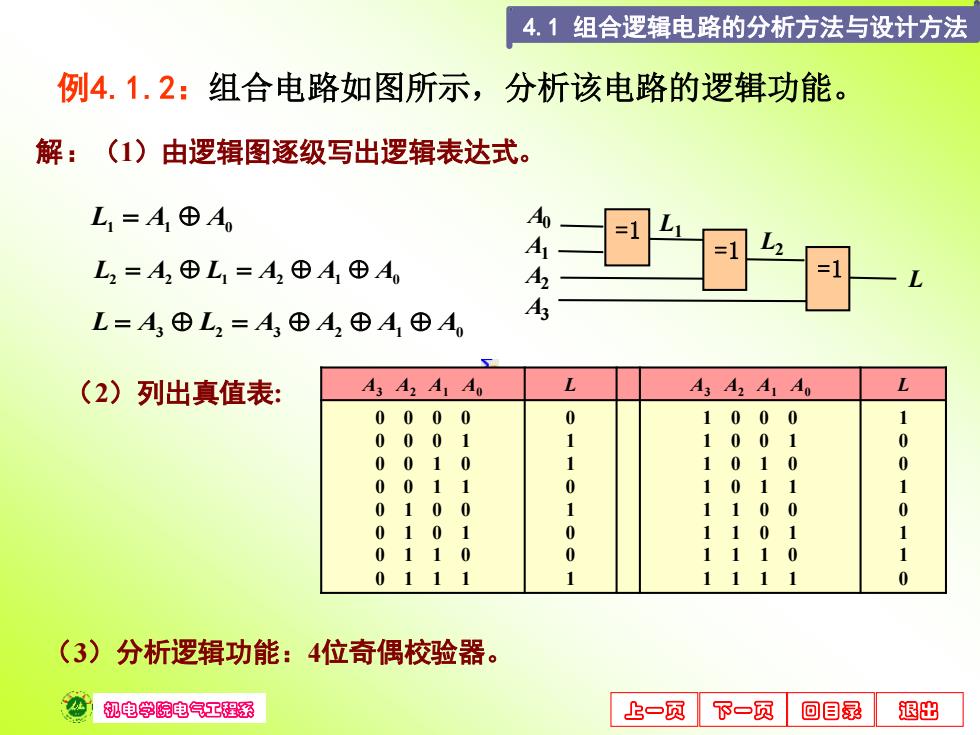

4.1组合逻辑电路的分析方法与设计方法 例4.1.2:组合电路如图所示,分析该电路的逻辑功能。 解:(1)由逻辑图逐级写出逻辑表达式。 L1=A1⊕A L2=A2⊕L1=A2⊕A1⊕A0 L=A⊕L2=A⊕A,⊕A1⊕A 4 (2)列出真值表: A3 A2 A Ao L A3 A2 A Ao L 0000 0 1000 1 0001 1 1001 0 0010 1010 0011 0 1011 1 0 010 1100 0101 0 1101 1 0110 0 110 1 0111 111 0 (3)分析逻辑功能:4位奇偶校验器。 少机电学院电气工程系 上一页下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 例4.1.2:组合电路如图所示,分析该电路的逻辑功能。 解:(1)由逻辑图逐级写出逻辑表达式。 L1 = A1 A0 L2 = A2 L1 = A2 A1 A0 L = A3 L2 = A3 A2 A1 A0 (2)列出真值表: A3 A2 A1 A0 L A3 A2 A1 A0 L 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 0 1 1 0 1 0 0 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 1 0 0 1 0 1 1 0 (3)分析逻辑功能:4位奇偶校验器。 4.1 组合逻辑电路的分析方法与设计方法 =1 A =1 =1 L L1 L2 0 A1 A2 A3

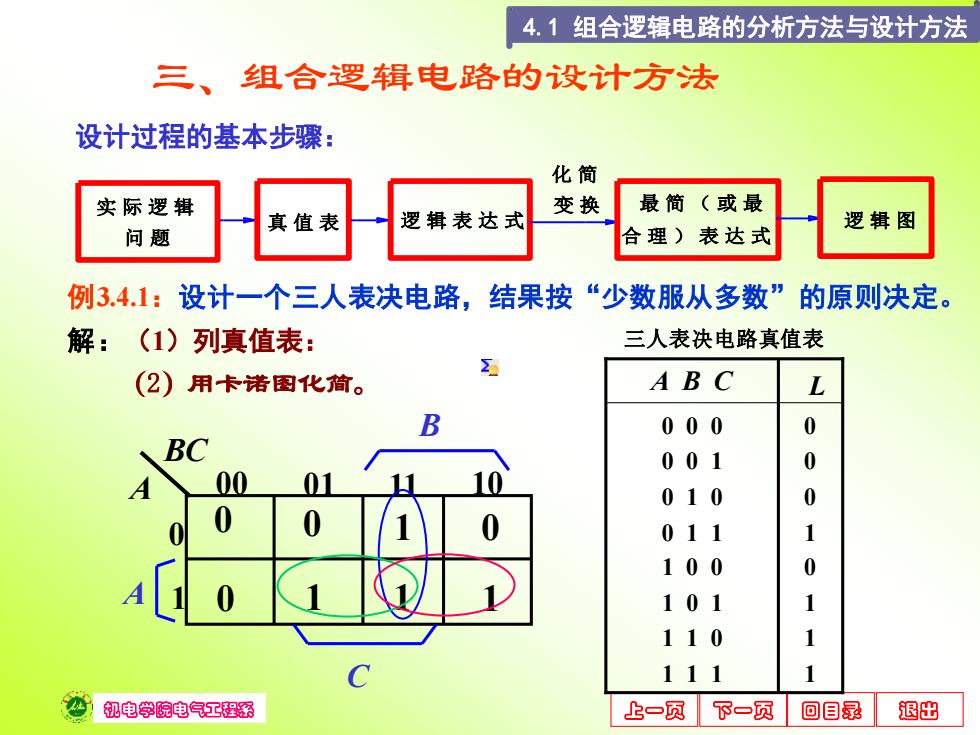

4.1组合逻辑电路的分析方法与设计方法 三、组合逻辑电路的设计方法 设计过程的基本步骤: 化简 实际逻辑 变换 最简(或最 真值表 逻辑表达式 逻辑图 问题 合理)表达式 例3.4.1:设计一个三人表决电路,结果按“少数服从多数”的原则决定。 解:(1)列真值表: 三人表决电路真值表 (2)用卡诺图化简。 AB C L B 000 0 001 0 010 0 011 1 100 0 101 1 110 111 机电学院电气工程系 上一页 下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 三、组合逻辑电路的设计方法 例3.4.1:设计一个三人表决电路,结果按“少数服从多数”的原则决定。 解:(1)列真值表: (2)用卡诺图化简。 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 A B C 0 0 0 1 0 1 1 1 L 三人表决电路真值表 A BC 0 00 01 1 11 10 A B C 1 1 1 0 0 1 0 0 实际逻辑 问 题 最简(或最 逻辑图 化 简 变 换 真值表 逻辑表达式 合理)表达式 设计过程的基本步骤: 4.1 组合逻辑电路的分析方法与设计方法

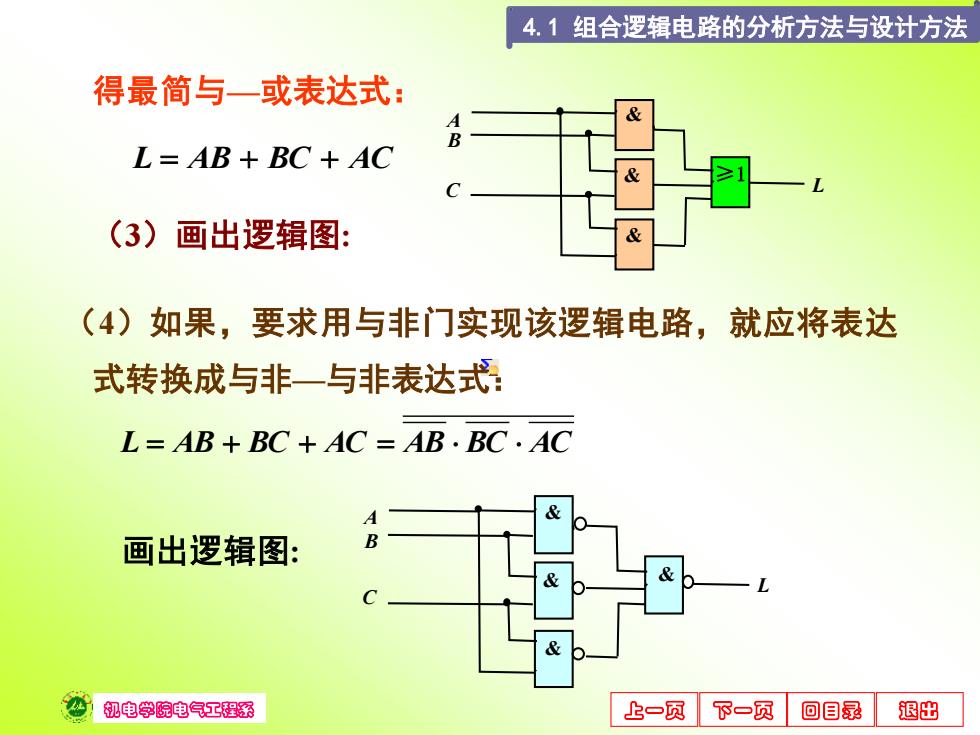

4.1组合逻辑电路的分析方法与设计方法 得最简与一或表达式: L=AB+BC+AC (3)画出逻辑图: (4)如果,要求用与非门实现该逻辑电路,就应将表达 式转换成与非一与非表达式 L=AB+BC+AC=AB.BC.AC 画出逻辑图: 机电学院电气工 上一页下一页 回目绿 退出

机电学院电气工程系 上一页 下一页 回目录 退出 L = AB + BC + AC (4)如果,要求用与非门实现该逻辑电路,就应将表达 式转换成与非—与非表达式: 画出逻辑图: L = AB + BC + AC = AB BC AC 得最简与—或表达式: (3)画出逻辑图: 4.1 组合逻辑电路的分析方法与设计方法 L & & & ≥1 A B C C B & A & & L &

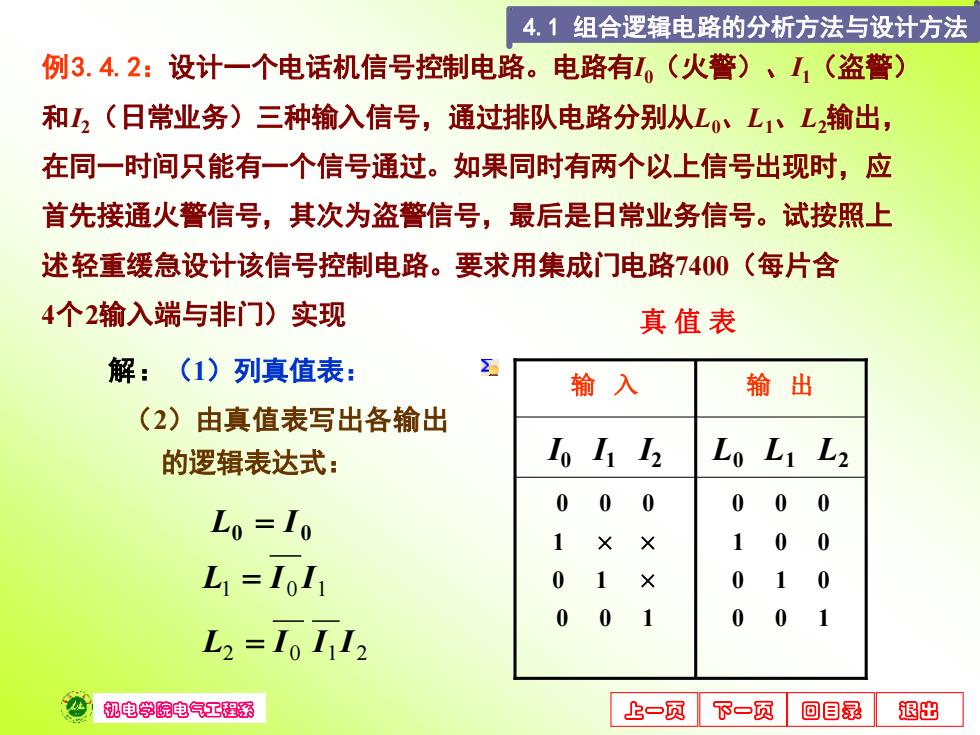

4.1组合逻辑电路的分析方法与设计方法 例3.4.2:设计一个电话机信号控制电路。电路有L0(火警)、1(盗警) 和L2(日常业务)三种输入信号,通过排队电路分别从Lo、L1小L输出, 在同一时间只能有一个信号通过。如果同时有两个以上信号出现时,应 首先接通火警信号,其次为盗警信号,最后是日常业务信号。试按照上 述轻重缓急设计该信号控制电路。要求用集成门电路7400(每片含 4个2输入端与非门)实现 真值表 解:(1)列真值表: 输入 输出 (2)由真值表写出各输出 的逻辑表达式: L012 Lo L L2 00 0 00 0 L0=I0 1×× 10 0 L=IoI 01 × 0 1 0 0 1 0 0 1 L2=1oI112 机电学院电气工程系 上一页 下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 解:(1)列真值表: (2)由真值表写出各输出 的逻辑表达式: 0 0 L = I 1 0 1 L = I I 2 0 1 2 L = I I I 输 入 输 出 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1 × × 0 1 × 0 0 1 L0 L1 L2 I0 I1 I2 真 值 表 例3.4.2:设计一个电话机信号控制电路。电路有I0(火警)、I1(盗警) 和I2(日常业务)三种输入信号,通过排队电路分别从L0、L1、L2输出, 在同一时间只能有一个信号通过。如果同时有两个以上信号出现时,应 首先接通火警信号,其次为盗警信号,最后是日常业务信号。试按照上 述轻重缓急设计该信号控制电路。要求用集成门电路7400(每片含 4个2输入端与非门)实现 4.1 组合逻辑电路的分析方法与设计方法

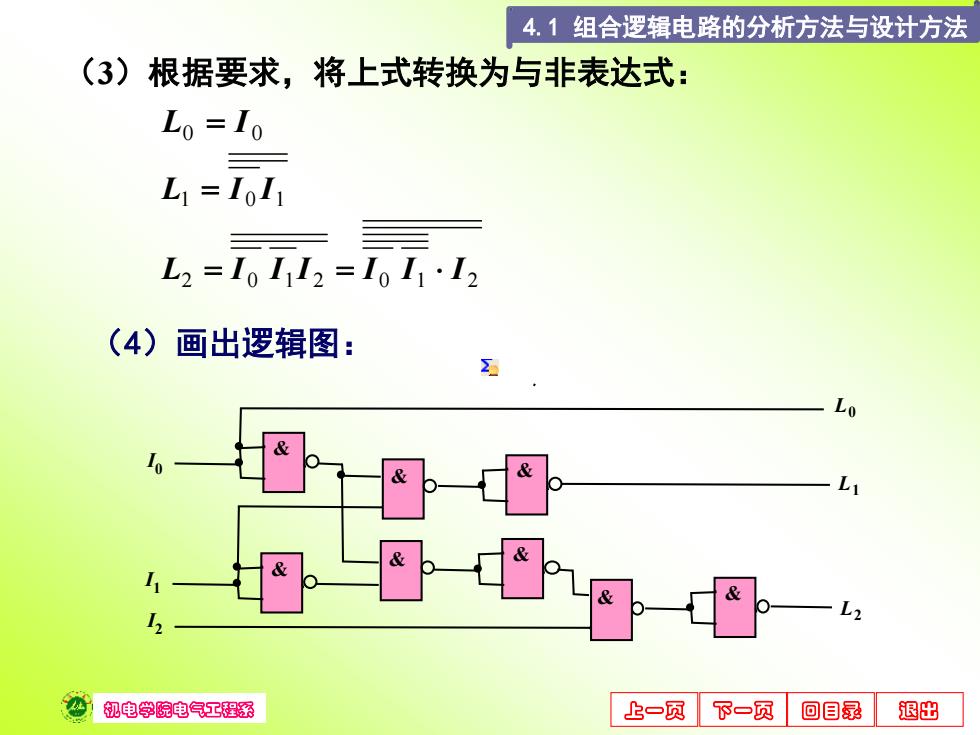

4.1组合逻辑电路的分析方法与设计方法 (3) 根据要求,将上式转换为与非表达式: Lo=Io L1=1o11 L2=I0I1I2=1011·12 (4)画出逻辑图: Lo 机电学院电气工程系 上一页下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 (4)画出逻辑图: 0 0 L = I 1 0 1 L = I I 2 0 1 2 0 1 2 L = I I I = I I I (3)根据要求,将上式转换为与非表达式: 4.1 组合逻辑电路的分析方法与设计方法 & & & & & & & & L I 0 2 I 1 I 2 L0 L1