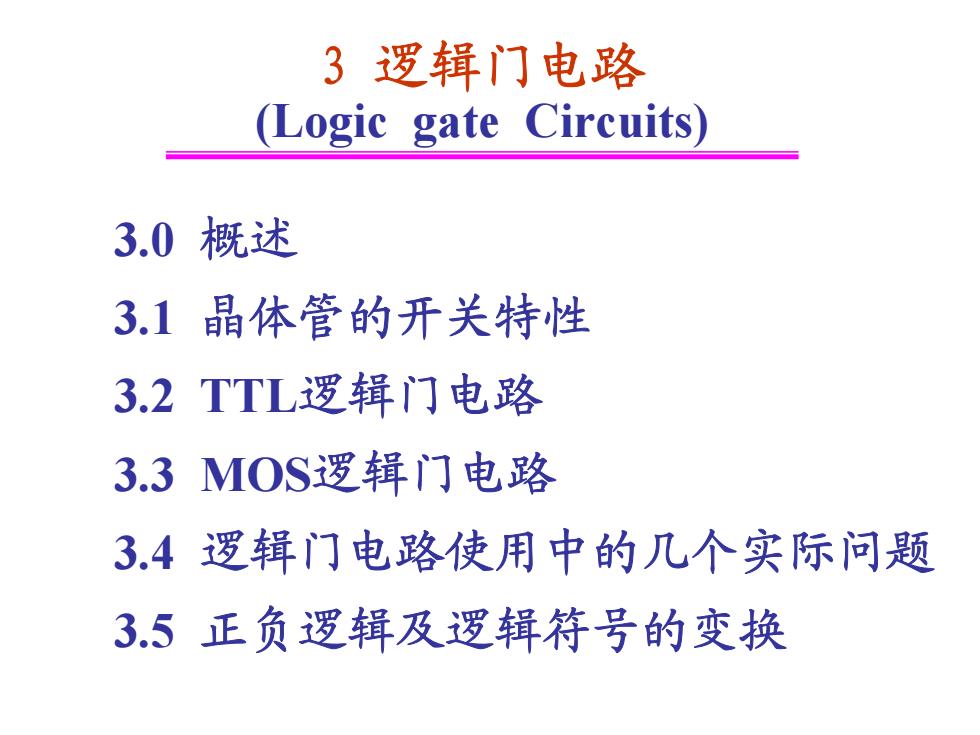

3逻辑门电路 (Logic gate Circuits) 3.0概述 3.1晶体管的开关特性 3.2TTL逻辑门电路 3.3MOS逻辑门电路 3.4逻辑门电路使用中的几个实际问题 3.5正负逻辑及逻辑符号的变换

3 逻辑门电路 (Logic gate Circuits) 3.1 晶体管的开关特性 3.2 TTL逻辑门电路 3.3 MOS逻辑门电路 3.0 概述 3.4 逻辑门电路使用中的几个实际问题 3.5 正负逻辑及逻辑符号的变换

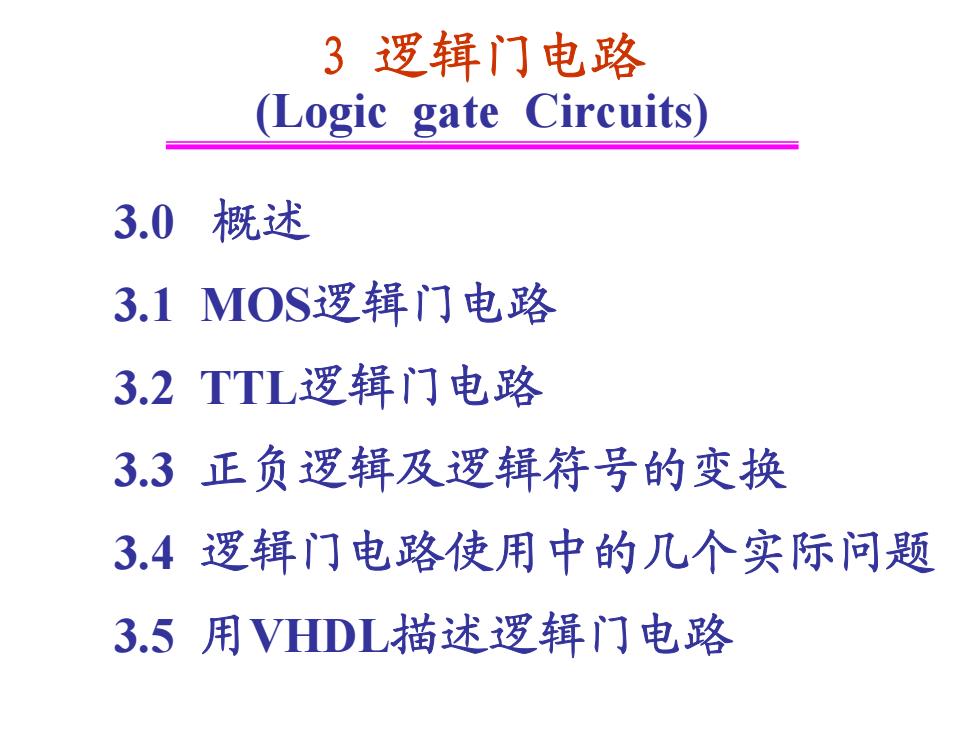

3逻辑门电路 (Logic gate Circuits) 3.0概述 3.1MOS逻辑门电路 3.2TTL逻辑门电路 3.3正负逻辑及逻辑符号的变换 34逻辑门电路使用中的几个实际问题 3.5用VHDL描述逻辑门电路

3 逻辑门电路 (Logic gate Circuits) 3.1 MOS逻辑门电路 3.2 TTL逻辑门电路 3.3 正负逻辑及逻辑符号的变换 3.0 概述 3.4 逻辑门电路使用中的几个实际问题 3.5 用VHDL描述逻辑门电路

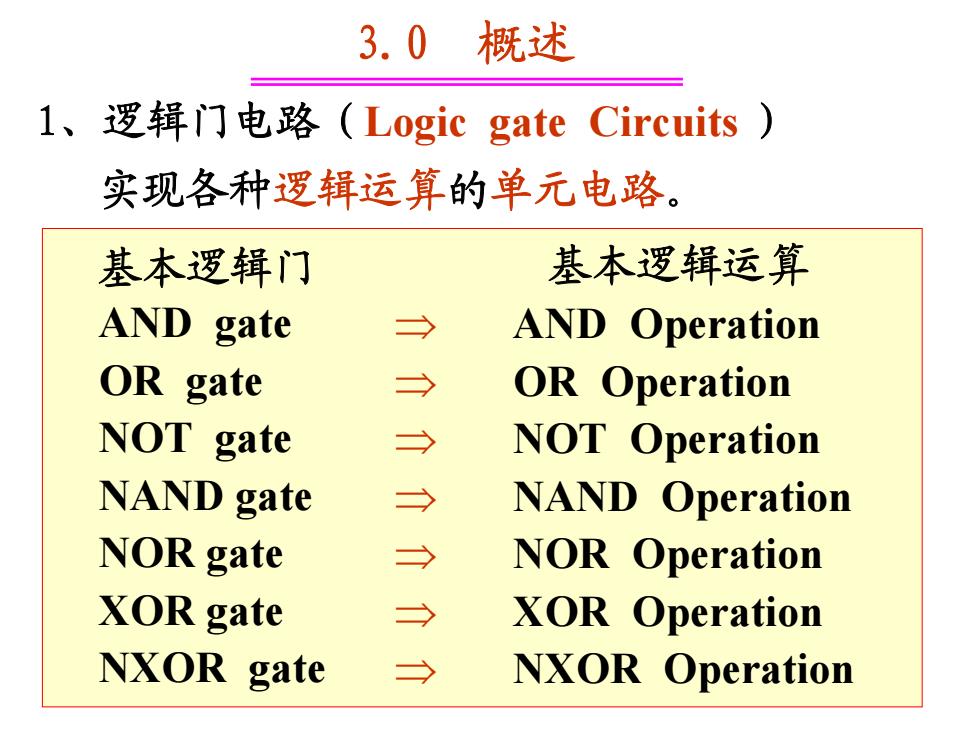

3.0概述 1、逻辑门电路(L0 gic gate Circuits 实现各种逻辑运算的单元电路。 基本逻辑门 基本逻辑运算 AND gate → AND Operation OR gate → OR Operation NOT gate ∂ NOT Operation NANd gate → NAND Operation NOR gate NOR Operation XOR gate XOR Operation NXOR gate NXOR Operation

3.0 概述 1、逻辑门电路(Logic gate Circuits ) 实现各种逻辑运算的单元电路。 基本逻辑门 AND gate OR gate NOT gate NAND gate NOR gate XOR gate NXOR gate 基本逻辑运算 AND Operation OR Operation NOT Operation NAND Operation NOR Operation XOR Operation NXOR Operation

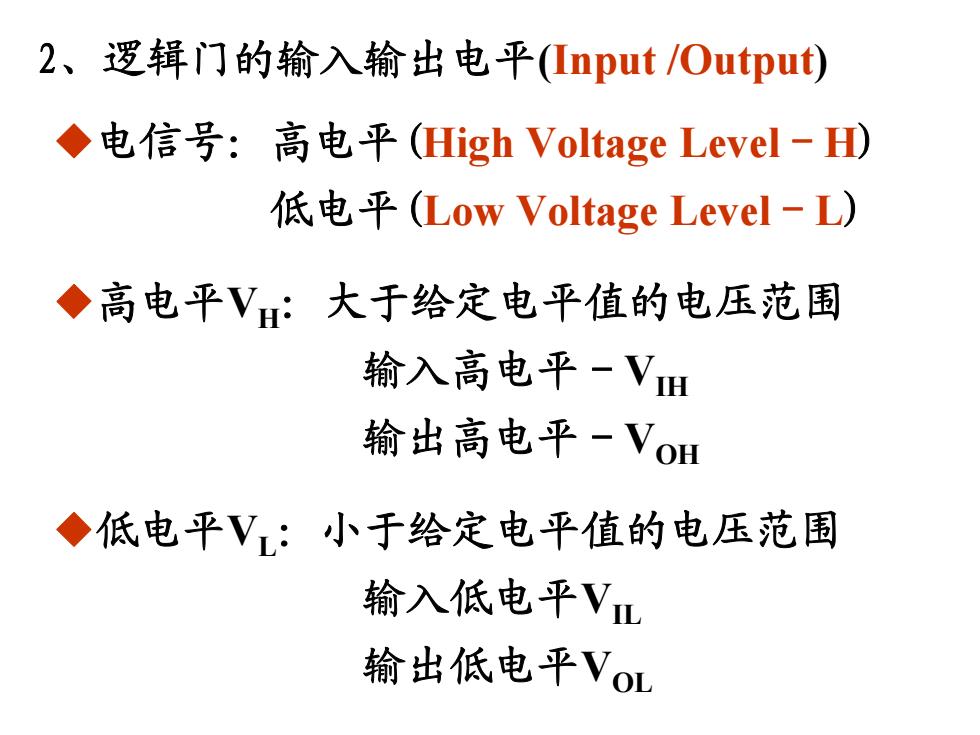

2、逻辑门的输入输出电平(nput/Output) ◆电信号:高电平(High Voltage Level-H) 低电平(Low Voltage Level-L) ◆高电平V:大于给定电平值的电压范围 输入高电平一VⅢ 输出高电平-VoH ◆低电平V:小于给定电平值的电压范围 输入低电平Vm 输出低电平VoL

2、逻辑门的输入输出电平 (Input /Output ) ◆电信号:高电平(High Voltage Level - H) 低电平(Low Voltage Level - L) ◆高电平 VH :大于给定电平值的电压范围 输入高电平- VIH 输出高电平- VOH ◆低电平 VL :小于给定电平值的电压范围 输入低电平 VIL 输出低电平 VOL

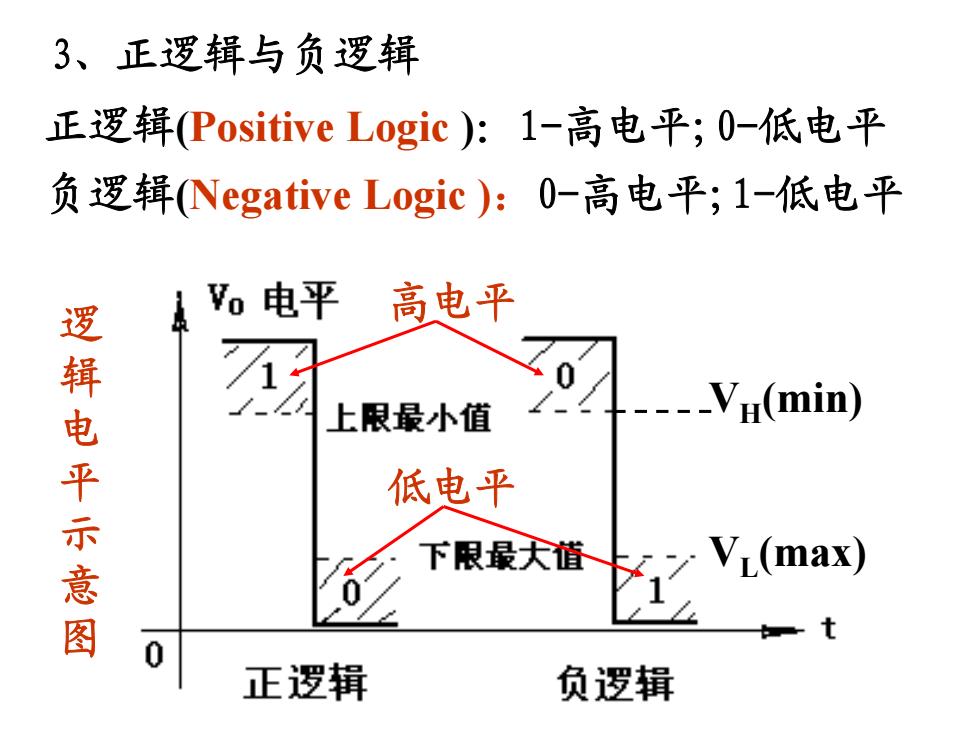

3、正逻辑与负逻辑 正逻辑Positive Logic):1-高电平;0-低电平 负逻辑Negative Logic):0-高电平;1-低电平 Vo电平 逻 高电平 电平示意图 上限最小值 Vn(mim) 低电平 0 正逻辑 负逻辑

VL (max) VH (min) 逻 辑 电 平 示 意 图 高电平 低电平 正逻辑(Positive Logic ):1-高电平;0-低电平 负逻辑(Negative Logic ):0-高电平;1-低电平 3、正逻辑与负逻辑

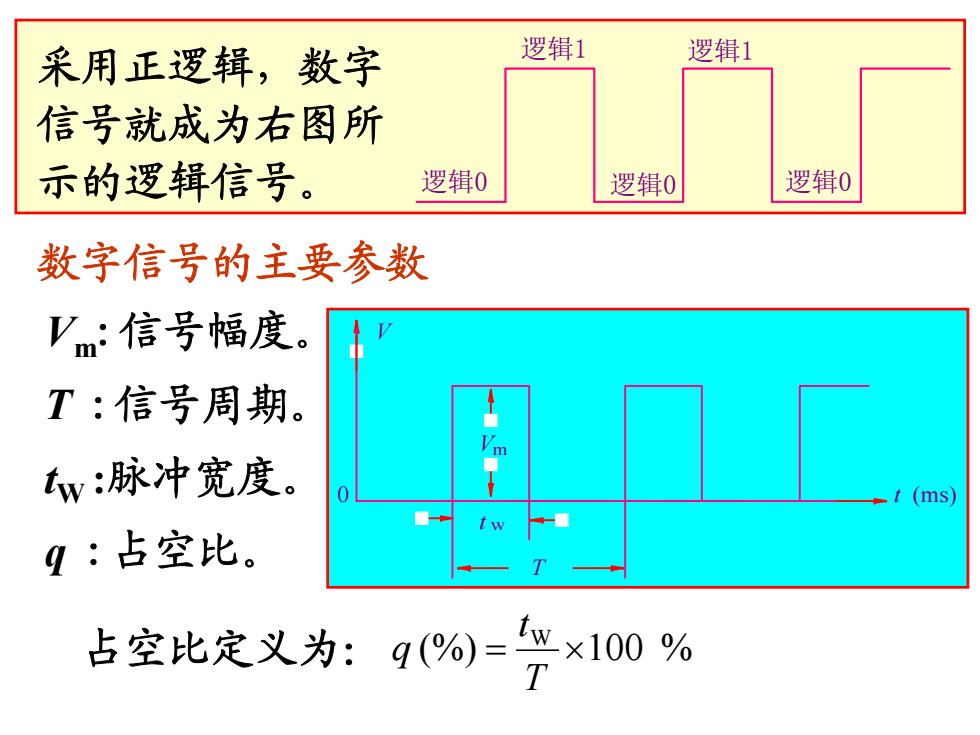

采用正逻辑,数字 逻辑1 逻辑1 信号就成为右图所 示的逻辑信号。 逻辑0 逻辑0 逻辑0 数字信号的主要参数 Vm:信号幅度。 T:信号周期。 w:脉冲宽度。 t(ms) t w q:占空比。 占空比定义为:9(%)=×100%

采用正逻辑,数字 信号就成为右图所 示的逻辑信号。 逻辑0 逻辑1 逻辑0 逻辑1 逻辑0 V 0 t (ms) Vm t w T 数字信号的主要参数 Vm :信号幅度。 T :信号周期。 tW :脉冲宽度。 q :占空比。 (%) % 100 W T t 占空比定义为: q

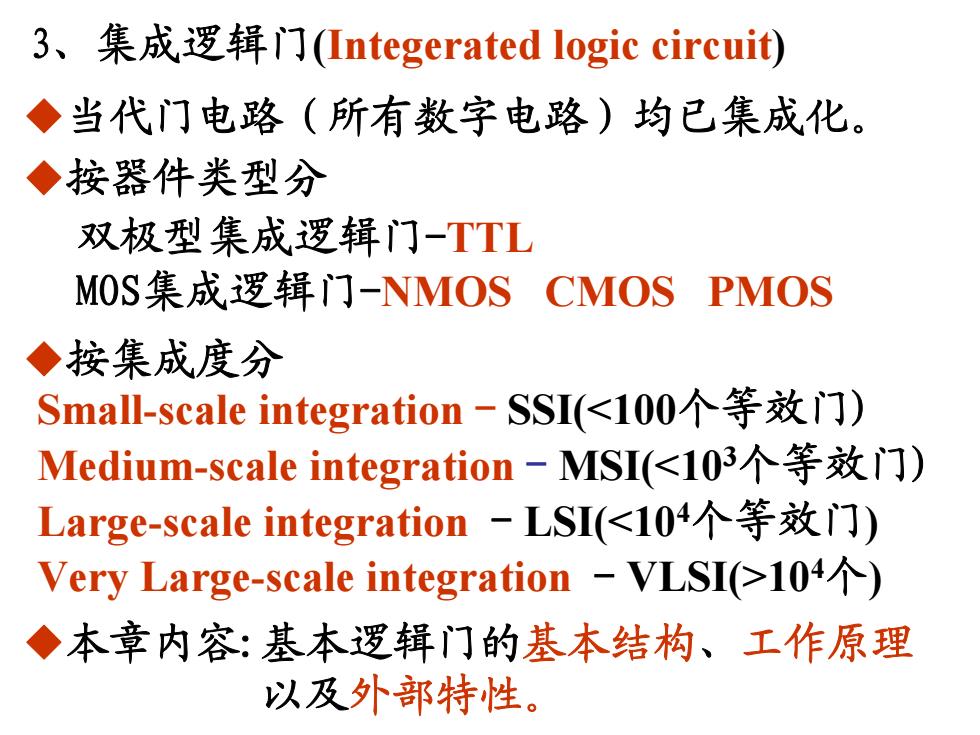

3、集成逻辑门(Integerated logic circuit) ◆当代门电路(所有数字电路)均已集成化。 ◆按器件类型分 双极型集成逻辑门-TTL MOS集成逻辑门-NMOS S CMOS PMOS ◆按集成度分 Smal-scale integration-SSI(<l00个等效门) Medium-scale integration-MSI(<l03个等效门) Large-scale integration-LSI(<l04个等效门) Very Large-scale integration-VLSI◇l04个) ◆本章内容:基本逻辑门的基本结构、工作原理 以及外部特性

3、集成逻辑门(Integerated logic circuit) ◆当代门电路(所有数字电路)均已集成化。 双极型集成逻辑门-TTL MOS集成逻辑门-NMOS CMOS PMOS ◆按器件类型分 ◆按集成度分 Small-scale integration-SSI(104个) ◆本章内容:基本逻辑门的基本结构、工作原理 以及外部特性

3.1晶体管的开关特性 (Switching characteristics) 门电路中晶体管均工作在开关状态。 一、二极管(Diode)的开关特性 1.二极管的静态特性(Static characteristics) (1)加正向电压V时,二极管导通,管压降V,可 忽略。二极管相当于一个闭合的开关。 K (a) (b)

一、二极管(Diode)的开关特性 D VF IF (a) RL (1)加正向电压VF 时,二极管导通,管压降VD 可 忽略。二极管相当于一个闭合的开关。 1.二极管的静态特性(Static characteristics) F K VF L R I (b) 门电路中晶体管均工作在开关状态。 3.1 晶体管的开关特性 (Switching characteristics)

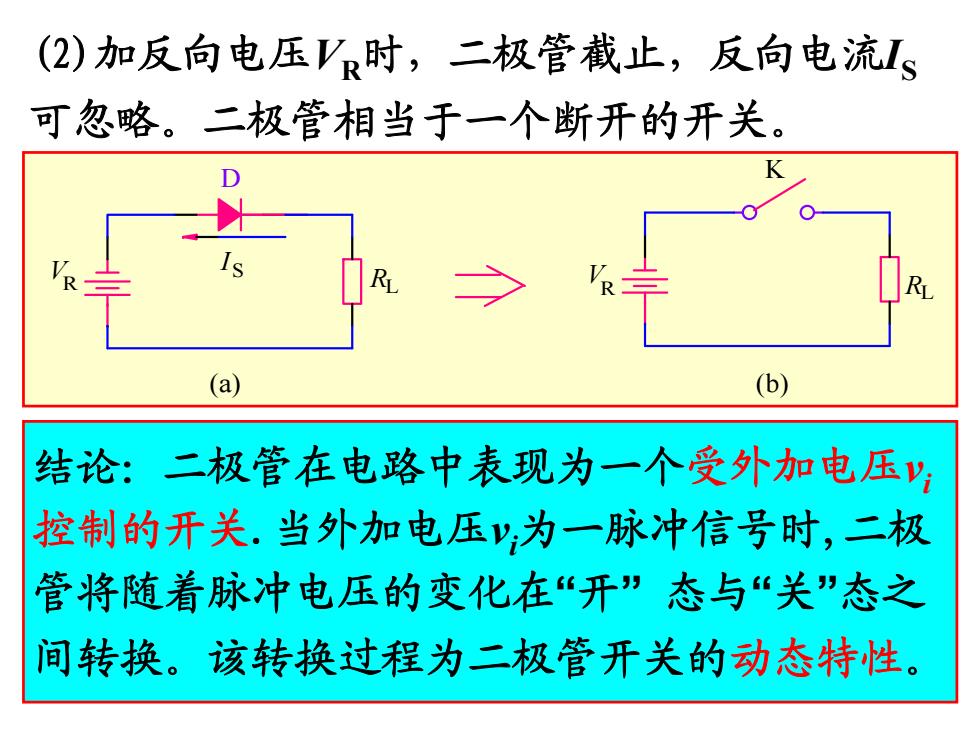

(2)加反向电压V.时,二极管截止,反向电流Is 可忽略。二极管相当于一个断开的开关。 (a) (b) 结论:二极管在电路中表现为一个受外加电压 控制的开关.当外加电压y为一脉冲信号时,二极 管将随着脉冲电压的变化在“开”态与“关”态之 间转换。该转换过程为二极管开关的动态特性

(2)加反向电压VR 时,二极管截止,反向电流IS 可忽略。二极管相当于一个断开的开关。 D VR IS RL (a) K RL VR (b) 结论:二极管在电路中表现为一个受外加电压vi 控制的开关.当外加电压vi为一脉冲信号时,二极 管将随着脉冲电压的变化在“开” 态与“关”态之 间转换。该转换过程为二极管开关的动态特性

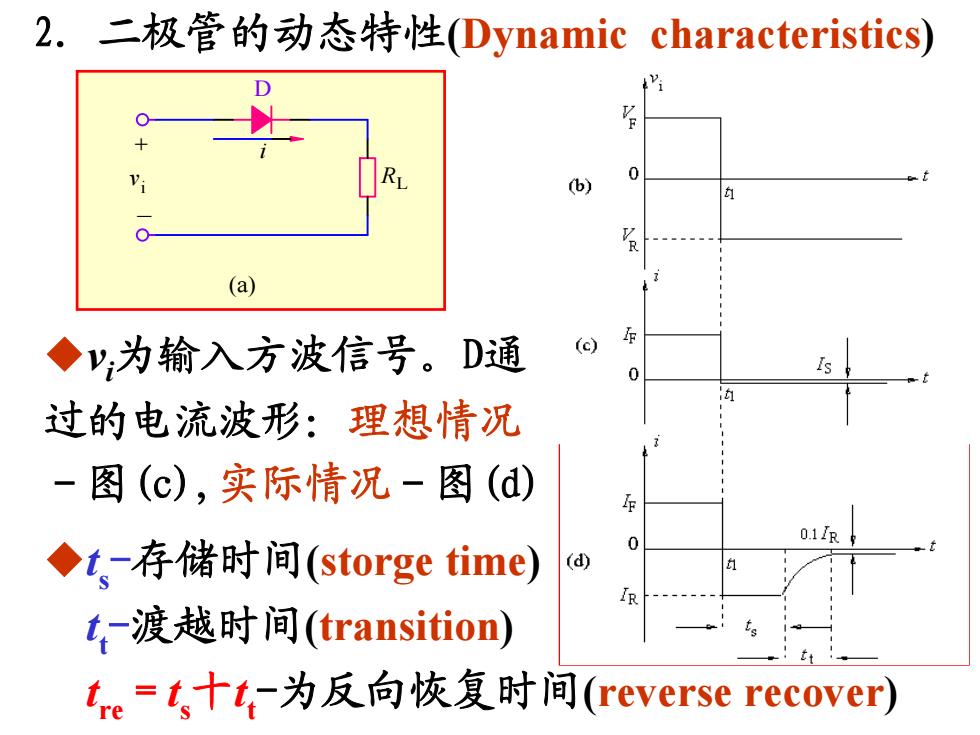

2.二极管的动态特性(Dynamic characteristics) (b) (a) ◆y,为输入方波信号。D通 过的电流波形:理想情况 -图(c),实际情况-图(d) 0.1/R ◆t,-存储时间(storge time) 0 t-渡越时间(transition) tre=t,十t,-为反向恢复时间(reverse recover)

2.二极管的动态特性 (Dynamic characteristics ) ◆ v i为输入方波信号。D通 过的电流波形:理想情况 -图(c),实际情况-图(d) ◆ ts -存储时间 (storge time ) tt -渡越时间 (transition ) tre = ts 十 tt -为反向恢复时间 (reverse recover ) + - D vi R L i (a) 产生反向恢复过程的 原因:反向恢复时间 tre 就是存储电荷消散 所需要的时间