Inputs Output y L H L H H y H L H HH Fig.10-1 Positive Logic NAND Gate 2002 Prentice Hall.Inc. M.Morris Mano DIGITAL DESIGN,3e

Inputs Output x y LL H L H L H L L HH L Fig.10-2 Positive Logic NOR Gate 2002 Prentice Hall,Inc. M.Morris Mano DIGITAL DESIGN,3e

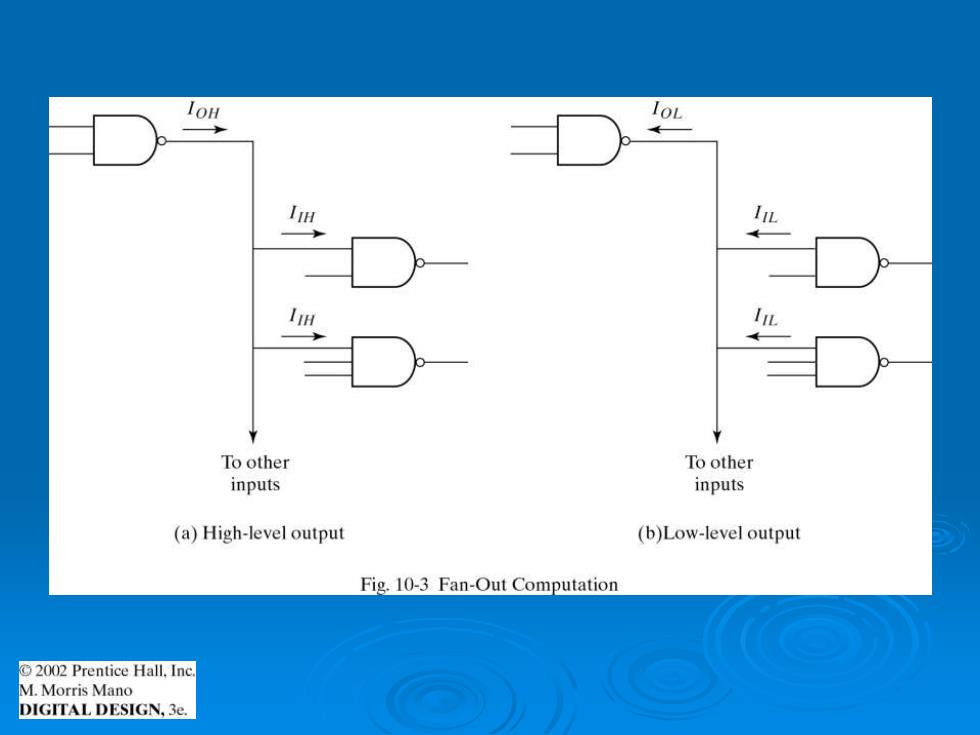

11L To other To other inputs inputs (a)High-level output (b)Low-level output Fig.10-3 Fan-Out Computation 2002 Prentice Hall.Inc. M.Morris Mano DIGITAL DESIGN,3e

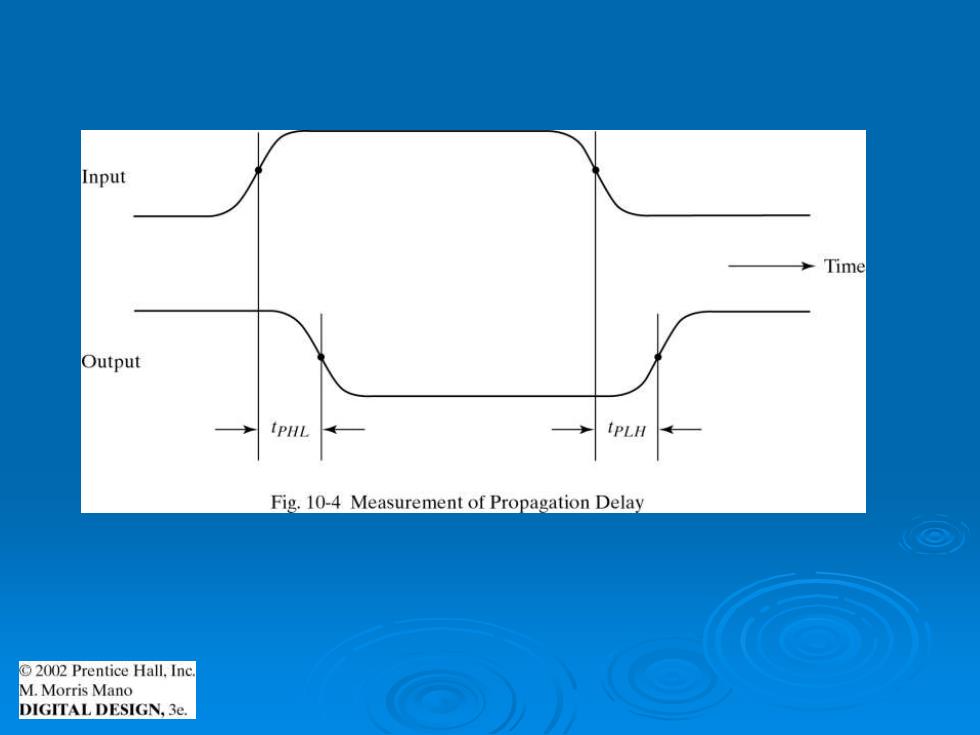

Input Time Output IPHL IPLH Fig.10-4 Measurement of Propagation Delay 2002 Prentice Hall.Inc M.Morris Mano DIGITAL DESIGN,3e

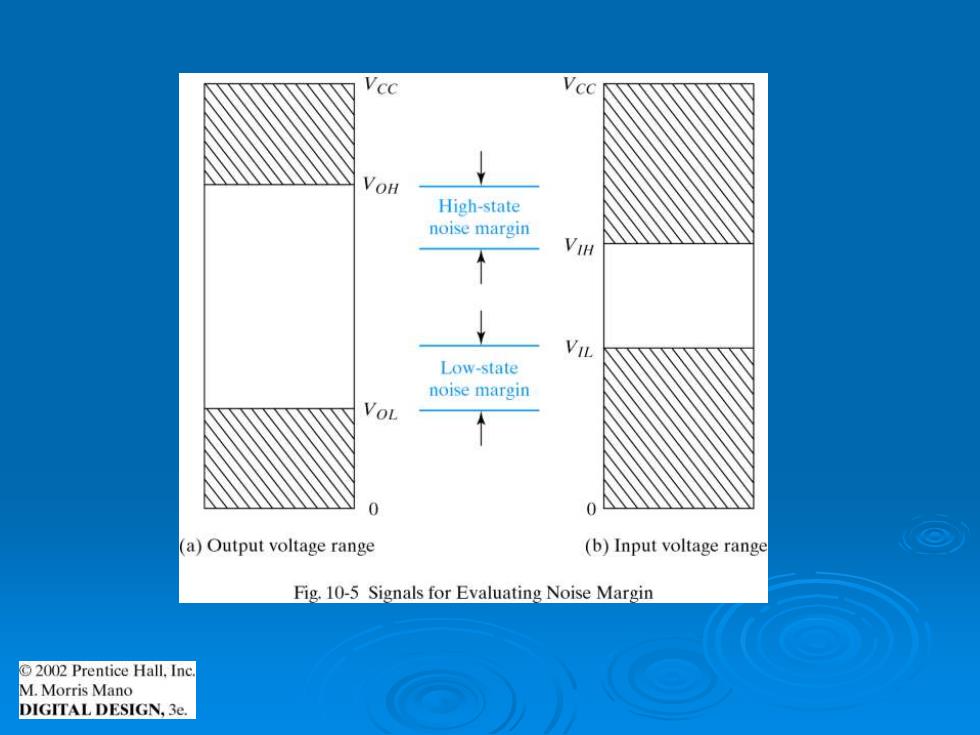

VOH High-state noise margin VIH VIL Low-state noise margin VOL 0 (a)Output voltage range (b)Input voltage range Fig.10-5 Signals for Evaluating Noise Margin 2002 Prentice Hall,Inc M.Morris Mano DIGITAL DESIGN,3e

oVo 1B RB (a)Inverter circuit 1c 1B (mA) (mA) Vc 0.6 Rc 0.5 0.4 0.4 1B=0.2mA 0.6 0.708'BE(y Vcc VCE (V) (b)Transistor-base characteristic (c)Transistor-collector characteristic Fig.10-6 Silicon npn Transistor Characteristics 2002 Prentice Hall.Inc. M.Morris Mano DIGITAL DESIGN,3e

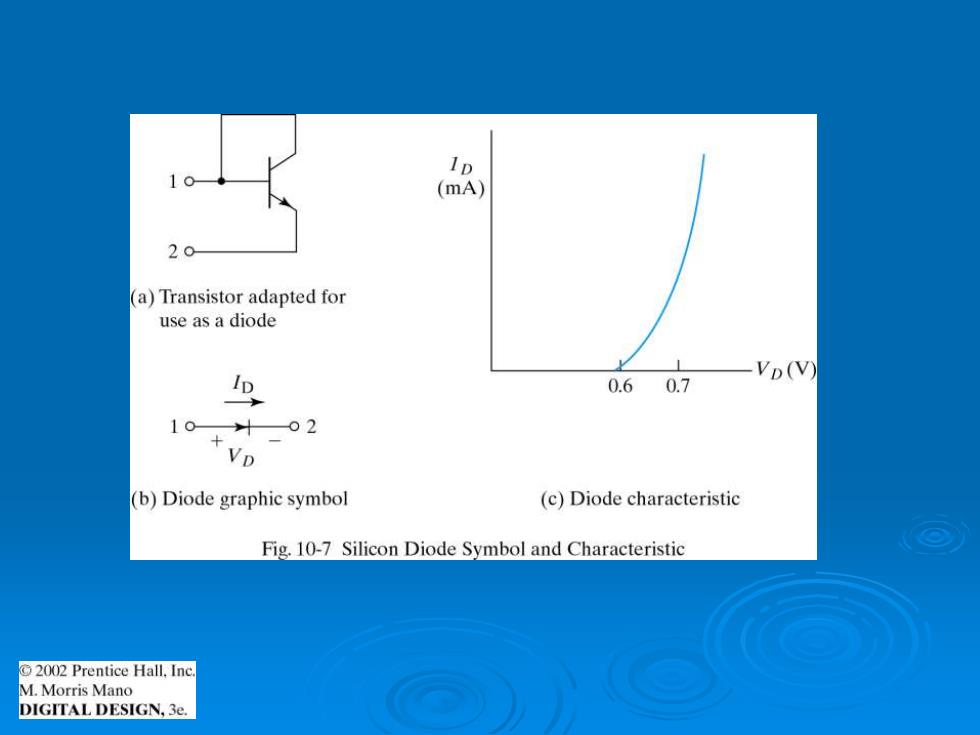

1D (mA) 20 (a)Transistor adapted for use as a diode Ip -VD(V) 0.60.7 10 402 × D (b)Diode graphic symbol (c)Diode characteristic Fig.10-7 Silicon Diode Symbol and Characteristic 2002 Prentice Hall.Inc. M.Morris Mano DIGITAL DESIGN,3e

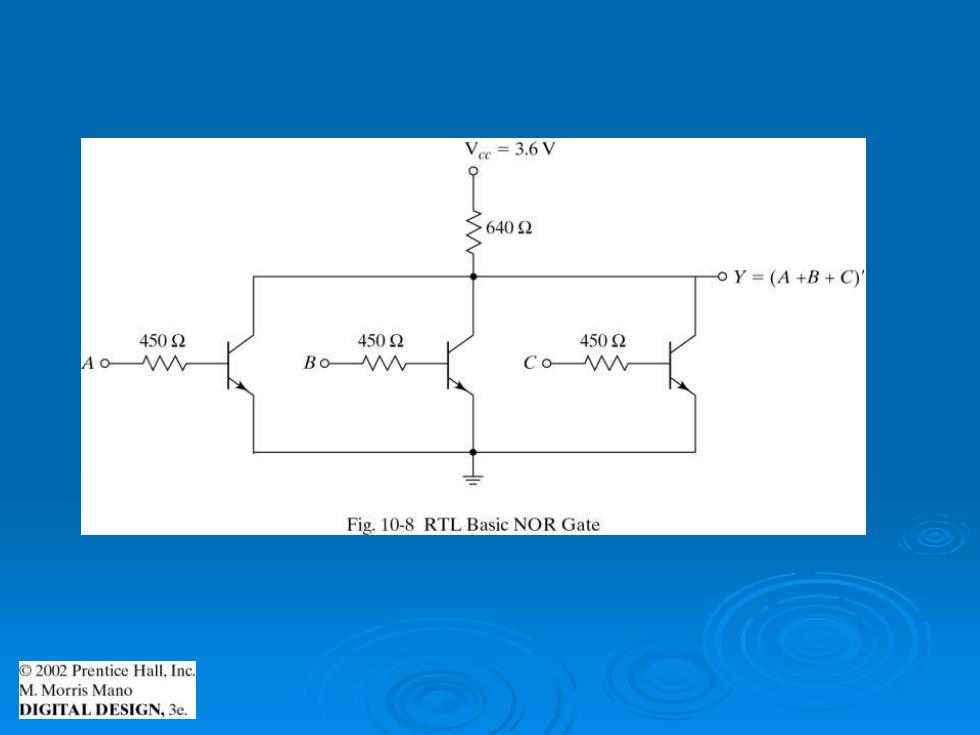

Vcc =3.6 V 0 三60n oY=(A+B+C) 4502 4502 4502 Co Fig.10-8 RTL Basic NOR Gate 2002 Prentice Hall,Inc. M.Morris Mano DIGITAL DESIGN,3e

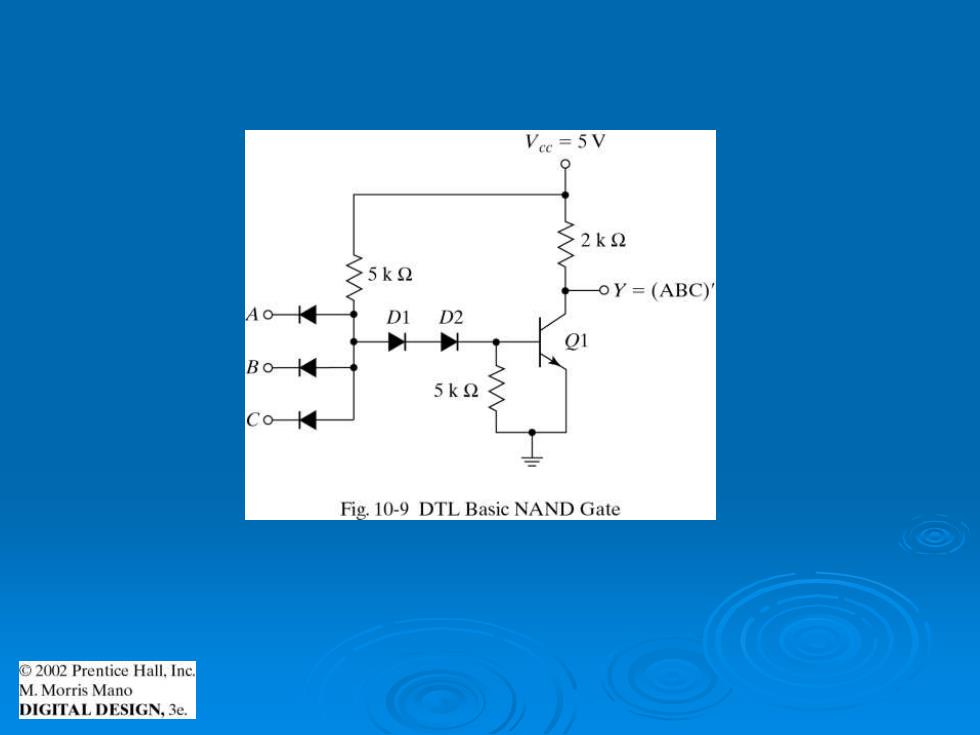

Vee=5V 22k2 5k oY=(ABC) D1 D2 5k2 Fig.10-9 DTL Basic NAND Gate 2002 Prentice Hall.Inc. M.Morris Mano DIGITAL DESIGN,3e

Vee=5V 31.6k2 32k0 32 oY=(ABC) A0 Q1 D2 5k2 Fig.10-10 Modified DTL Gate 2002 Prentice Hall,Inc. M.Morris Mano DIGITAL DESIGN,3e